Fターム[5F004AA05]の内容

半導体のドライエッチング (64,834) | 目的 (7,312) | 選択性の向上 (1,192) | エッチング条件の改良 (423)

Fターム[5F004AA05]に分類される特許

121 - 140 / 423

比重誘起ガス拡散分離(GIGDS)法によるプラズマ生成の制御

本発明は、比重誘起ガス拡散分離法によるプラズマ生成を用いた基板処理装置及び方法を供することができる。各異なる比重(つまり気体の構成要素の分子の重さと参照分子の重さとの比)を有する不活性ガスとプロセスガスを含むガスを追加又は使用することによって、2領域又は多領域プラズマを生成することができる。2領域又は多領域プラズマでは、一の種類のガスがプラズマ生成領域付近で強く閉じこめられ、かつ、他の種類のガスは、比重の違いにより誘起される拡散によって、前記一の種類のガスから大きく分離されて、前記一の種類のガスよりもウエハ処理領域の近くで閉じこめられる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 被エッチング材に形成するパターンの線幅の面内ばらつきを抑制可能な半導体装置の製造方法を提供する。

【解決手段】 被エッチング材105の第1領域110、第2領域210に、それぞれ第1パターン、第2パターンを形成する際に、リソグラフィのばらつきによりレジストパターン(開口部111、開口部211)に生じるばらつきに起因して発生する、第1パターン、第2パターンの線幅がばらつき、マスク材106の厚みを調整することにより抑制する。

(もっと読む)

半導体表面におけるパターンの作製方法

【課題】所望のパターンを有する第1のマスクと所望のパターンの開口部に拡散されるエッチング種の量を制御するための第2のマスクとを用いて、深さが変化する所望のパターンを半導体表面に作製するための方法において、エッチングに寄与するエッチング種を増大させること。

【解決手段】エッチングガスに塩素を用いてRIBEを行うと、図17(b)の構造が得られる。このエッチングにおいて、マスク厚の厚いSiNxマスク1411からの塩素プラズマの寄与が大きく、マスク厚の薄いSiO2マスク1410からの塩素プラズマの寄与は小さい。したがって、マスク幅の広い回折格子中央部ではマスク上で反応しない塩素プラズマが多量に開口部に拡散することにより開口部での塩素プラズマは高濃度になりエッチング速度が増加する。ここで用いるマスクは2段構造を有しており、1段構造に比べてより多くのエッチング種をエッチングに関与させる。

(もっと読む)

磁気素子の製造方法と装置

【課題】エッチング損傷を減少させるべくドライエッチングを用いて磁気素子を製造する。

【解決手段】磁気素子の製造方法と装置を提供する。素子の磁性及び/又は非磁性層はTaのような非有機材マスクを用いN2のような不活性ガスと水素ガスの混合ガスによりエッチングされる。結果として、研究例ではMTJテーパ角はほぼ垂直である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線絶縁膜としてSiOCH膜を用いる場合に、ビアホールの開口径に依らず、その加工制御性を十分に得て、下層Cu配線の表面の組成のバラツキを十分に抑制する。

【解決手段】下層Cu配線3上に形成されている積層構造20は、シリコンと炭素を含有するキャップ絶縁膜4と、キャップ絶縁膜4上に形成されている配線絶縁膜5としてのSiOCH膜を有する。積層構造20にビアホール8、9を形成する工程は、第1及び第2ドライエッチングを組み合わせて行う。第1ドライエッチングでは開口径が小さいビアホール9のエッチングレートが、開口径が大きいビアホール8のエッチングレートよりも大きくなるようにO2濃度が設定された第1混合ガスを用いる。第2ドライエッチングではビアホール8のエッチングレートがビアホール9のエッチングレートよりも大きくなるようにO2濃度が設定された第2混合ガスを用いる。

(もっと読む)

シリコン含有ハードマスクをパターンエッチングする方法

【課題】シリコン含有誘電物質の層をパターンエッチングする方法を提供する。

【解決手段】該方法は、約2:3〜約3:1、更に典型的には約1:1〜約2:1の範囲にあるCF4とCHF3を含むプラズマ供給源ガスを用いる。エッチングは、約4mTorr〜約6mTorrの範囲にあるプロセスチャンバ圧で行われる。

【効果】該方法は、1.5:1以上のフォトレジスト114に相対してシリコン含有誘電体層110をエッチングする選択性を与える。該方法は、また、半導体構造において前記エッチングされたシリコン含有誘電体層110と下にある水平層108間に88°〜92°の範囲にあるエッチングプロファイル側壁角を与える。該方法は、193nm放射光に敏感であるある種のフォトレジストと組み合わせて用いた場合に平滑な側壁を与える。

(もっと読む)

シリコン化合物膜のドライエッチング方法

【課題】 SF6等の地球温暖化の一因となるガスを用いずに、窒化シリコン膜、アモルファスシリコン膜等のシリコン化合物膜を良好にドライエッチングする。

【解決手段】 例えば、ゲート絶縁膜3の上面には真性アモルファスシリコン膜21および窒化シリコン膜(チャネル保護膜形成用膜)22が成膜され、その上にはレジスト膜23が形成されている。そして、少なくともCOF2ガスを含むエッチングガスを用いてドライエッチングすると、窒化シリコン膜22を良好にドライエッチングすることができ、レジスト膜23下にチャネル保護膜が形成される。この場合、下地の真性アモルファスシリコン膜21が露出され、この露出された真性アモルファスシリコン膜21がある程度ドライエッチングされるが、その際の選択比は約7である。

(もっと読む)

実質的にアンダカットのないシリコンを絶縁体構造上に作製するエッチング工程

【課題】シリコン・オン・インシュレータ界面のアンダカットを実質的に抑制する方法を提供する。

【解決手段】垂直方向に一様なエッチングを行うように様々なサイズの凹部内のイオン充電を制限するためにイオン密度が低減される反応性イオン・エッチング工程を仕上げエッチング段階として使用することによってアンダカットが実質的になくなる、シリコン・オン・インシュレータ基板に異方性プラズマ・エッチングを施す方法を開示する。

(もっと読む)

被処理体の処理方法、処理装置、薄膜形成方法、薄膜形成装置及びプログラム

【課題】被処理体に形成された自然酸化膜を除去することができる被処理体の処理方法、処理装置及びプログラムを提供する。

【解決手段】 熱処理装置1の制御部100は、自然酸化膜が形成された半導体ウエハWを収容した反応管2内を400℃に加熱する。反応管2内が400℃に加熱されると、制御部100は、処理ガス導入管17から、塩素を含む処理ガスを供給することにより処理ガスに含まれる塩素を活性化させる。この活性化された塩素が半導体ウエハWに供給されることにより、半導体ウエハWに形成された自然酸化膜が除去される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法

【課題】低いオン抵抗と高い耐圧性とを有する電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法を提供する。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板101と、前記基板上に形成された高抵抗層103と、前記高抵抗層上に形成された、炭素濃度が1×1018cm−3以下であり層厚が10nmより厚く、100nm以下であるチャネル層104を含む半導体動作層106と、前記半導体動作層に前記チャネル層の内部に到る深さまで形成されたリセス部107と、前記半導体動作層上に前記リセス部を挟んで形成されたソース電極108およびドレイン電極109と、前記半導体動作層上にわたって前記リセス部内を覆うように形成されたゲート絶縁膜110と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極111と、を備える。

(もっと読む)

高アスペクト比誘電体エッチングのための方法及び装置

【解決手段】高アスペクト比特徴をエッチングするための装置が提供される。プラズマ処理チャンバエンクロージャを形成するチャンバ壁と、下部電極と、上部電極と、ガス入口と、ガス出口とを含むプラズマ処理チャンバが提供される。上部電極又は下部電極の少なくとも一方に、高周波数無線周波数(RF)電源が電気的に接続される。上部電極及び下部電極の両方に、バイアス電力システムが電気的に接続され、該バイアス電力システムは、上部電極及び下部電極に少なくとも500ボルトの大きさのバイアスを供給することができ、下部電極に対するバイアスは、断続的にパルス化される。ガス源が、ガス入口と流体接続している。ガス源、高周波数RF電源、及びバイアス電力システムには、コントローラが可制御式に接続される。 (もっと読む)

半導体装置の製造方法

【課題】プラズマ雰囲気の周囲に存在する銅による影響を抑制する半導体装置の製造方法を提供する。

【解決手段】半導体基板1の上方に絶縁膜18〜21を形成する工程と、絶縁膜18〜21上にレジスト膜24を形成する工程と、レジスト膜24の上方にマスク膜25を形成する工程と、マスク膜25の上方にレジストパターン27を形成する工程と、レジストパターン27をマスクにしてマスク膜25をエッチングする工程と、酸素ガスとハイドロフロロカーボンガスの混合ガスを導入し、30mTorr以上の圧力の雰囲気内で、マスク膜25から露出する領域のレジスト膜24をエッチングする工程とを有する。

(もっと読む)

変調多周波処理方法

【課題】

【解決手段】ガスを受け入れるよう構成された内部の空間と、空間内で電磁場を生成するよう動作可能な電磁場生成部とを有する処理システムを動作させる方法が提供されている。その方法は、空間内にガスを供給する工程と、空間内で電磁場を生成してガスの少なくとも一部をプラズマに変換するように、駆動電位で電磁場生成部を動作させる工程とを備える。時間の関数としての駆動電位は、第1の電位関数部分および第2の電位関数部分に基づく。第1の電位関数部分は、第1の振幅と第1の周波数とを有する第1の連続周期的部分を含む。第2の電位関数部分は、最大振幅部分と最小振幅部分とデューティサイクルとを有する第2の周期的部分を含む。最大振幅部分は、最小振幅部分よりも高い振幅を有する。デューティサイクルは、最大振幅部分の持続時間および最小振幅部分の持続時間の合計に対する最大振幅部分の持続時間の比である。第2の周期的部分は、さらに、最大振幅部分の間に第2の周波数を有する。第2の周期的部分の振幅変調は、第1の連続周期的部分に位相固定される。

(もっと読む)

有機反射防止膜をプラズマエッチングする方法

【課題】有機反射防止膜のドライエッチングに、O2を含むガスを用いて、上層のフォトレジストが横方向にエッチングされ、クリティカルディメンジョンの変化を対策する方法を提供する。

【解決手段】半導体製造プロセスであって、このプロセスは、有機反射防止膜が、下層に対して選択性を与え、及び/又は、フォトレジストによって定められるクリティカルディメンジョンを維持する上層のフォトレジストの横方向のエッチング速度を最小化する。その為に、有機反射防止膜のドライエッチングに、エッチャントガスとしてSO2、キャリアガスとしてHe又はAr等を用いる。このガスには、随意的に、HBr等の他のガスを付加してもよい。このプロセスは、ダマシン構造等の構造を形成するときに0.25μmかそれ以下のコンタクト開口部又はビア開口部をエッチングするのに役立つ。

(もっと読む)

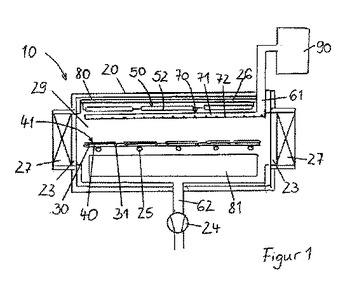

基板処理装置および基板処理方法

本発明は、少なくとも1つの基板を担持した少なくとも1つの基板キャリアを中に導入することができる少なくとも1つの排気可能なプロセス・チャンバと、プラズマ発生モジュールと、少なくとも1つのガス供給部と、少なくとも1つのガス排出部とを備える基板処理装置に関する。さらに、本発明は、少なくとも1つの基板を担持した少なくとも1つの基板キャリアが少なくとも1つの排気可能なプロセス・チャンバに導入され、プロセス・チャンバ内で、プラズマ・プロセスにおいてプラズマ発生モジュールによってガスまたはガス混合物中でプラズマが発生され、基板のコーティング、エッチング、表面改質、および/または洗浄が行われる基板処理方法に関する。本発明の目的は、十分に表面テクスチャ加工された基板でさえ高いスループットおよび高品質で等方性エッチングすることができる、上記の一般的なタイプの基板処理装置および基板処理方法を提供することである。この目的は、まず、上記の一般的なタイプの基板処理装置であって、気相エッチング・モジュールがプロセス・チャンバ内に組み込まれた基板処理装置によって実現される。さらに、この目的は、上記の一般的なタイプの基板処理方法であって、プロセス・チャンバ内で、少なくとも1つの基板の気相エッチングが、プラズマ・プロセスの前に、および/またはプラズマ・プロセスの後に、および/またはプラズマ・プロセスと交互に行われる基板処理方法によって実現される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】多層マスクエッチングを用いたホール加工において、開口径及び深さの均一なホールを絶縁膜内に形成する。

【解決手段】窒化膜1上に、層間絶縁膜2とレジスト膜3とハードマスク膜4とを順に積層させた多層マスクを形成する工程と、層間絶縁膜2を露出させる開口を多層マスクに形成する工程と、フルオロカーボンを含むガスFRをエッチングガスとしてエッチングを行うことにより、開口内の層間絶縁膜2を除去しつつ、開口の周囲のハードマスク膜4を除去する工程(図3(b))と、開口の周囲にレジスト膜3が露出する前に、ガスFRをガスFRよりもC/F(炭素原子数とフッ素原子数との比率)が高いフルオロカーボンを含むガスFPに切り替えてエッチングを行うことにより、開口から窒化膜1が底面をなすコンタクトホールを形成する工程(図3(c))と、を含む。

(もっと読む)

プラズマエッチング方法、プラズマエッチング装置及びコンピュータ記憶媒体

【課題】ArFフォトレジストのダメージ(荒れ)を抑制しつつ、シリコンを含有する反射防止膜(Si−ARC)を高いエッチングレート及び十分な選択比でプラズマエッチングすることのできるプラズマエッチング方法、プラズマエッチング装置及びコンピュータ記憶媒体を提供する。

【解決手段】基板に形成されたArFフォトレジスト103をマスクとして、ArFフォトレジスト103の下層に位置するSiを含有する反射防止膜102を、処理ガスのプラズマによりエッチングするプラズマエッチング方法であって、処理ガスとして、CF系ガス及び/又はCHF系ガスと、CF3Iガスと、酸素ガスとを含む混合ガスを使用し、かつ、上部電極に直流電圧を印加する。

(もっと読む)

プラズマ処理方法およびプラズマ処理装置

【課題】多層レジストや、メタルゲート/High−k等の積層膜のドライエッチング加工において、高精度の加工精度が要求される。

【解決手段】複数層の連続エッチング加工において、エッチング後の寸法測定することなく、加工の形状または寸法を、真空処理室1の内壁または半導体基板4と、真空処理室1内に生成されたプラズマとの間の電荷量に応じて変動するバイアス電位を計測し、また、プラズマ中の波長の異なる各イオン種の発光強度を測定し、これらから予め設定したモデル式にて、各膜種のエッチング処理毎に、エッチング後の各膜種の加工寸法を予測し、次の膜のエッチング後寸法が、所定の寸法値になるよう処理条件を変更し、連続して次の膜種のエッチング処理を行うことで、寸法や形状を補正するドライエッチング方法および装置を提供する。

(もっと読む)

プラズマ処理方法

【課題】基板にエッチング処理だけでなく電子を用いた処理を施すことができるプラズマ処理方法を提供する。

【解決手段】プラズマ処理装置10は、ウエハWを収容し且つプラズマが発生するチャンバ11と、該チャンバ11内に配置されてウエハWを載置し、且つプラズマ引き込み用の高周波電圧が印加されるサセプタ12と、チャンバ11内においてサセプタ12と対向するように配置され、且つ負の直流電圧が印加される上部電極33とを備え、プラズマ処理装置10では、上部電極33に負の直流電圧が印加される間、サセプタ12へのプラズマ引き込み用の高周波電圧の印加の所定時間に亘る継続と、サセプタ12へのプラズマ引き込み用の高周波電圧の印加の停止とが繰り返される。

(もっと読む)

121 - 140 / 423

[ Back to top ]