Fターム[5F032AA36]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 溝内埋込み分離 (7,414) | 溝の断面形状 (2,101) | 垂直側面を有するもの (1,970) | 溝上部にテーパのあるもの (127)

Fターム[5F032AA36]に分類される特許

1 - 20 / 127

半導体装置の製造方法及び半導体装置

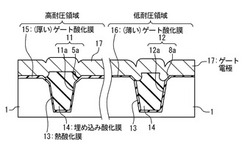

【課題】高耐圧MOSトランジスタと低電圧MOSトランジスタとの両方について良好な特性を得るための技術を提供する。

【解決手段】高耐圧領域に高耐圧トランジスタが形成され、低耐圧領域に低耐圧トランジスタが形成される半導体装置の製造方法が提供される。当該半導体装置の製造方法は、シリコン基板1の表面に、熱酸化膜2とシリコン窒化膜3を形成する工程と、高耐圧領域、低耐圧領域のそれぞれにおいて熱酸化膜2とシリコン窒化膜3に開口を形成する工程と、該開口を通じてシリコン基板1をエッチングしてトレンチ11、12を形成する工程と、トレンチ11、12に埋め込み酸化膜14を埋め込む工程と、熱酸化膜2とシリコン窒化膜3を除去する工程と、厚いゲート酸化膜15と薄いゲート酸化膜16とを形成する工程とを備えている。トレンチ12のテーパー部分8aの深さが、トレンチ11のテーパー部分5aの深さよりも浅い。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】アモルファスカーボン膜などの酸化によりパターン精度が劣化する材料からなるハードマスク膜上に保護膜とマスク膜の積層膜を形成し、マスク膜をダブルパターニング技術を用いてパターニングすると、保護膜も2回のエッチングに曝されて、保護膜としての機能が損なわれ、パターニングに使用する有機膜除去のアッシングの際に、ハードマスク膜が酸化されてパターン精度が劣化し、忠実なパターン転写ができなくなる。

【解決手段】マスク膜6の2回目のエッチングの際に、パターニングに用いる有機膜(反射防止膜7b、8b)をマスク膜6表面は露出するが、保護膜5表面は露出しないようにエッチングし、マスク膜6のみを選択的にパターニングすることで、その後の残存する有機膜のアッシング除去に際して、ハードマスク膜4を酸化から保護する保護膜5の機能を確保でき、パターン転写の忠実性を確保できる。

(もっと読む)

ドライエッチング方法

【課題】本発明は、ダミー材料の除去により形成される溝や孔に容易にトップラウンドを設けることができるドライエッチング方法を提供する。

【解決手段】本発明は、層間酸化膜に周囲を囲まれたダミー材料を除去することにより溝または孔を形成するドライエッチング方法において、前記ダミー材料を所定の深さまでエッチングし、前記エッチング後に等方性エッチングを行い、等方性エッチング後に前記ダミー材料の残りを除去することを特徴とするドライエッチング方法である。

(もっと読む)

半導体装置の製造方法

【課題】DHF処理後に実施されるHPM処理またはAPM処理を、良好に行うことができる半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、槽内に水を導入して、槽内から希フッ酸を排出する工程と、槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、槽内に、H2O2と、上記水よりも温度の高い温水とを導入する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】製造プロセスが複雑になるといったことを防ぎつつ、n型及びp型MOSトランジスタについて両方の性能を向上させた半導体装置を提供する。

【解決手段】半導体基板1の面内に、n型MOSトランジスタと、p型MOSトランジスタとを備える半導体装置であって、n型MOS型トランジスタが形成される第1の拡散層2aの間を絶縁分離する第1の絶縁層3aと、p型MOS型トランジスタが形成される第2の拡散層2cの間を絶縁分離する第2の絶縁層3bとを備え、第1の絶縁層3aは、半導体基板1の表層に形成された第1の溝部4aに、シリコン窒化膜5と、このシリコン窒化膜5の上にシリコン酸化膜6とを埋め込むことによって形成され、第2の絶縁層3bは、半導体基板1の表層に第1の溝部4aよりも幅広となるように形成された第2の溝部4bに、シリコン酸化膜6を埋め込むことによって形成されている。

(もっと読む)

半導体装置

【課題】 素子特性の劣化を抑制する。

【解決手段】 実施形態による半導体装置は、トランジスタ領域を有する半導体装置であって、トランジスタ領域は、基板上に形成された半導体領域と、半導体領域に隣接する素子分離領域と、ラテラルエピタキシャル層を備え、半導体領域上及び半導体領域と素子分離領域との間で横方向に成長するエピタキシャル層と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】塗布法を用いて形成される酸化膜を溝の内部に充填した溝型の素子分離部を有する半導体装置において、溝の内部におけるボイドの発生を抑制して、埋め込み不良を低減することのできる技術を提供する。

【解決手段】0.2μm以下の溝幅を有する溝4Sの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも高く、かつ1.0μm以上の溝幅を有する溝4Lの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも低くなるように、半導体基板1の主面上にポリシラザン膜を形成し、続いて、300℃以上の熱処理を行うことにより、ポリシラザン膜を酸化シリコン(SiO2)からなる第1埋め込み膜8へ転化すると同時に、溝4Sの上部に局所的に生じたボイドを消滅させる。

(もっと読む)

半導体装置およびその製造方法

【課題】溝型の素子間分離部により囲まれた活性領域に形成される電界効果トランジスタにおいて、所望する動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部SIOを、溝型素子分離膜6L,6Sと、溝型素子分離膜6L,6Sの上面に形成されたシリコン膜またはシリコン酸化膜からなる厚さ10〜20nmの拡散防止膜20と、拡散防止膜20の上面に形成された厚さ0.5〜2nmのシリコン酸化膜21L,21Sとから構成し、拡散防止膜20の組成をSiOx(0≦x<2)とし、溝型素子分離膜6L,6Sおよびシリコン酸化膜21L,21Sの組成をSiO2とする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の結晶性の悪化を招くことなく、素子分離トレンチの幅を小さくできる半導体装置の製造方法を提供する。

【解決手段】マスク用窒化膜51およびパッド酸化膜52からなるハードマスクを用いて、シリコン基板2がエッチングされることにより、素子分離トレンチ21が形成される。素子分離トレンチ21の内面に熱酸化法によりライナー酸化膜22が形成される。続いて、半導体基板2を窒素雰囲気中に配置して、半導体基板2が熱処理される。熱処理後に、エッチングにより、ライナー酸化膜22が薄膜化される。そして、HDP−CVD法により、絶縁物23が素子分離トレンチ21内に埋め込まれる。

(もっと読む)

シングルゲートフィンFET及びその製造方法

【課題】新規なFinFET構造及びその製造方法を提供する。

【解決手段】シングルゲートフィンFET構造100は、2つの拡大された頭部、及び当該拡大された頭部と下層の超薄型ボディとを連結する2つの徐々に細くなる首部を有するアクティブフィン構造を含む。2つのソース/ドレイン領域102,104が、2つの拡大された頭部にそれぞれドープされる。絶縁領域26が、2つのソース/ドレイン領域の間に挿入される。溝分離構造24が、音叉形状のフィン構造の一方の側に配置される。片面サイドウォールゲート電極12bが、アクティブフィン構造における、溝分離構造とは反対側の垂直なサイドウォールに配置される。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板中に形成した素子分離溝の上部角部への電界集中によるトランジスタの電気的特性の劣化を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1に半導体基板1表面とは異なる結晶面方位有する素子分離溝2を形成する工程と、半導体基板1上に酸素ラジカル発生を促進する金属3又は酸素ラジカル発生を促進する金属3を含む膜を堆積する工程と、半導体基板1を酸化する工程と、金属または金属を含む膜を除去する工程とを有する。

(もっと読む)

デュアルドープゲートの用途におけるプロフィル制御とN/Pローディングを改善する方法

【課題】プラズマエッチングチャンバ内でデュアルドープゲート構造をエッチングするための方法を提供する。

【解決手段】エッチングされるポリシリコンフィルムを保護するパターンを設ける工程、次いで、プラズマが点火され、保護されていないポリシリコンフィルムのほぼすべてがエッチングされる。次いで、シリコン含有ガスを導入しつつポリシリコンフィルムの残りをエッチングする。また、エッチング処理中にシリコン含有ガスを導入するよう構成されたエッチングチャンバ。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易なプロセスで、高い埋め込み性を確保する必要のない半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法では、まず支持基板SSと、埋め込み絶縁膜BOXと半導体層SLとがこの順で積層された構成を有する半導体基板SUBが準備される。半導体層SLの主表面に、導電部分を有する素子が完成される。上記素子を平面視において取り囲む溝DTRが、半導体層SLの主表面から埋め込み絶縁膜BOXに達するように形成される。上記素子上を覆うように、かつ溝DTR内に中空を形成するように素子上および溝DTR内に第1の絶縁膜(層間絶縁膜II)が形成される。上記第1の絶縁膜に素子の導電部分に達する孔であるコンタクトホールCHが形成される。

(もっと読む)

酸化物層を有する半導体部品

【課題】 酸化物層を有する半導体部品を提供する。

【解決手段】 酸化物層を有する半導体部品。一実施形態は、第1の半導体領域と第2の半導体領域とを含む。酸化物層は、第1および第2の半導体領域間に配置される。第1の半導体領域および酸化物層が第1の半導体−酸化物界面を形成する。第2の半導体領域および酸化物層が第2の半導体−酸化物界面を形成する。酸化物層は塩素濃度を有し、塩素濃度は、第1の半導体−酸化物界面の領域における第1の極大点と、第2の半導体−酸化物界面の領域における第2の極大点とを有する。

(もっと読む)

半導体装置の製造方法

【課題】SOIデバイスにおいて生じやすい基板浮遊問題やホットキャリアの問題を充分に抑制することが可能で、広く分布する部分分離絶縁膜であっても周囲の構造に対し結晶欠陥を生じさせにくい半導体装置の製造方法を提供する。

【解決手段】各MOSトランジスタTR1の間に設けられた部分分離絶縁膜5b内におよそ一定の間隔を置いて、素子としての機能を有しないダミー領域DM1を形成する。これにより、部分分離絶縁膜5b下のシリコン層3bよりも抵抗値の低いダミー領域DM1の占める割合が増加して、基板浮遊問題やホットキャリアの問題の抑制が行えるようになる。

(もっと読む)

半導体装置及びその製造方法

【課題】ナローチャネル特性の劣化を抑制する。

【解決手段】素子分離領域STIは、半導体基板100に形成されたトレンチ104内に設けられており、トレンチ104の側壁上に形成された下地絶縁膜105を有している。素子形成領域100a上にはゲート絶縁膜112が形成されており、ゲート絶縁膜112は高誘電率膜110を有している。高誘電率膜110の第1の部分110aは、素子形成領域100aにおける上面上に形成されており、高誘電率膜110の第2の部分110bは、素子形成領域における上部側面104a上に下地絶縁膜105を介して形成されている。第2の部分110bと下地絶縁膜105との間には、MISトランジスタの閾値電圧を変更する金属を含有する第1のキャップ膜106が設けられている。

(もっと読む)

半導体装置の製造方法、及び、半導体装置

【課題】 特性の優れた高耐圧トランジスタを形成することができる素子分離膜の形成方法を提供する。

【解決手段】

基板上にまず先にゲート酸化膜102を形成しておき、その上にCMPストッパ膜104を形成後、ゲート酸化膜とCMPストッパ膜をエッチングし、半導体基板をエッチングしてトレンチ108を形成する。また、トレンチ内をフィールド絶縁膜で充填する前に、ライナー絶縁膜112をトレンチ内壁に形成し、CMPストッパ膜の下のゲート酸化膜の側面の凹み部分をライナー絶縁膜で埋め込むことにより、ゲート酸化膜の側方の素子分離膜に空隙(ボイド)が形成されるのを抑止する。

(もっと読む)

半導体装置

【課題】高耐圧の電界効果トランジスタを有する半導体装置のキンク現象を抑制または防止する。

【解決手段】高耐圧pMISQHp1のチャネル領域のゲート幅方向の両端の溝型の分離部3と半導体基板1Sとの境界領域に、高耐圧pMISQHp1のソースおよびドレイン用のp+型の半導体領域P1,P1とは逆の導電型のn+型の半導体領域NVkを、高耐圧pMISQHp1の電界緩和機能を持つp−型の半導体領域PV1,PV1(特にドレイン側)に接しないように、そのp−型の半導体領域PV1,PV1から離れた位置に配置した。このn+型の半導体領域NVkは、溝型の分離部3よりも深い位置まで延在されている。

(もっと読む)

半導体装置

【課題】SOI基板のSOI層と浅溝素子分離との境界部の形状を改善することにより、半導体装置の低消費電力化を実現することのできる技術を提供する。

【解決手段】シリコン基板3の主面とSOI層1の側面に沿って延びる線とが交差する位置(SOIエッジ10)が、浅溝側壁8に沿って延びる線とシリコン基板3の主面に沿って延びる線とが交差する位置(STIエッジ9)よりも、浅溝素子分離4と反対方向に後退し、STIエッジ9におけるシリコン基板3の角が曲面を有している。

(もっと読む)

1 - 20 / 127

[ Back to top ]