Fターム[5F032AB03]の内容

素子分離 (28,488) | PN接合を用いる分離 (255) | 素子領域底面のみをPN接合で分離するもの (46)

Fターム[5F032AB03]に分類される特許

1 - 20 / 46

半導体装置

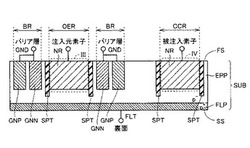

【課題】注入元素子から被注入素子への電子の移動を抑制する効果が高く、素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】第1および第2の主表面を有する半導体基板SUB内にはエピタキシャル層EPPと、n型不純物領域NRを含む注入元素子と、注入元素子と間隔を隔てて形成された被注入素子と、注入元素子と被注入素子との間の領域の少なくとも一部に形成され、注入元素子と被注入素子とを結ぶ方向に対して交差する方向に延在する接地電位が印加されたn型領域GNNおよびp型領域GPPを有するバリア層BRとを備える。さらに半導体基板SUB内でエピタキシャル層EPPに接するように形成されたフローティングp型裏面領域FLPを有する。

(もっと読む)

半導体装置

【課題】バルク半導体基板上に形成されるトンネルトランジスタ同士を電気的に分離することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板内に形成された第1および第2の素子分離絶縁膜とを備える。さらに、前記装置は、前記第1および第2の素子分離絶縁膜間の前記半導体基板上に、ゲート絶縁膜を介して形成されたゲート電極を備える。さらに、前記装置は、前記半導体基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域を備える。さらに、前記装置は、前記半導体基板内に前記第1および第2の素子分離絶縁膜に接するように形成され、前記第1および第2の主端子領域の下面よりも深い位置に上面を有する、前記第2導電型の第1の拡散層を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

バッファ付きフィンFETデバイス

【課題】フィンFETデバイスのロバストネスを向上させる。

【解決手段】トランジスタデバイスであって、半導体基板と、半導体基板に形成されたバッファ付き垂直フィン状構造であって、垂直フィン状構造は、ドレーン領域とソース領域512との間にチャンネル領域514を含む上位の半導体層と、上位の半導体層の下のバッファ領域304であって、第1のドーピング極性を有するバッファ領域と、第1のドーピング極性と反対である第2のドーピング極性を有するウェル領域302の少なくとも一部分と、バッファ領域とウェル領域との間の少なくとも1つのp−n接合であって、該垂直フィン状構造の水平断面を少なくとも部分的にカバーする少なくとも1つのp−n接合とを含むバッファ付き垂直フィン状構造と、上位の半導体層のチャンネル領域をおおい形成されたゲートスタックとを備えている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】STIの形成によるウェル拡散層の不純物濃度の変化を抑制し、かつ、ウェル拡散層のドーズロスを抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。メモリセル領域には、複数のメモリセルが半導体基板上に形成されている。周辺回路領域には、複数のメモリ素子を制御する複数の半導体素子が形成されている。素子分離領域は、複数のメモリセル間を分離し、あるいは、複数の半導体素子間を分離する。周辺回路領域において半導体素子が形成されているアクティブエリアの不純物濃度は、半導体基板の表面に対して水平方向に素子分離領域の側面からアクティブエリアの内部へ向かって低下している。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置

【課題】より確実に画素間クロストークを抑制することが可能な、固体撮像素子を備える半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に配置された第1導電型の不純物層DPWと、不純物層DPW上に、第1導電型の不純物領域と第2導電型の不純物領域とが互いに接合する構成を含む光電変換素子と、光電変換素子を含む単位画素を構成し、光電変換素子と電気的に接続されるトランジスタM1〜M4とを備えている。平面視において光電変換素子の外周部の少なくとも一部には、内部に空隙AGが含まれ、光電変換素子と、光電変換素子に隣接する光電変換素子とを、互いに電気的に絶縁する分離絶縁層SIが配置されている。上記分離絶縁層SIは、第1導電型の不純物層DPWの最上面に接する。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの形成工程を利用して、トレンチアイソレーションを形成できるようにした半導体装置の製造方法を提供する。

【解決手段】シリコン基板1にDTI層20とMOSトランジスタとを有する半導体装置の製造方法であって、シリコン基板1に深いトレンチを形成し、トレンチが形成されたシリコン基板1に熱酸化を施して、PMOSトランジスタ50のゲート酸化膜13を形成すると同時に、トレンチの内側面にSiO2膜14を形成する。次に、トレンチを埋め込むようにシリコン基板1上にポリシリコン膜15を堆積し、このポリシリコン膜15をパターニングする。これにより、PMOSトランジスタ50のゲート電極17を形成すると同時に、トレンチ内にSiO2膜14とポリシリコン膜18とを含むDTI層20を形成する。

(もっと読む)

半導体装置

【課題】出力トランジスタの形成領域から他の素子の形成領域への電子の移動を抑制する効果が高く、素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体基板SUBと、1対の注入元素子DRと、アクティブバリア構造ABと、p型接地領域PGDとを備える。半導体基板SUBは主表面を有し、かつ内部にp型領域を有する。1対の注入元素子DRは、p型領域上であって主表面に形成される。アクティブバリア構造ABは、主表面において1対の注入元素子DRに挟まれる領域に配置される。p型接地領域PGDは、主表面において1対の注入元素子DRに挟まれる領域を避けて1対の注入元素子DRおよびアクティブバリア構造ABよりも主表面の端部側に形成され、かつp型領域に電気的に接続された、接地電位を印加可能な領域である。p型接地領域PGDは、1対の注入元素子DRに挟まれる領域と隣り合う領域において分断されている。

(もっと読む)

半導体装置の製造方法

【課題】高性能・高信頼性を実現しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板にアライメントマークとなる溝を形成し、アライメントマークに位置合わせして素子分離領域となる領域を露出し素子領域となる領域を覆うマスク膜を形成し、マスク膜をマスクとして半導体基板を異方性エッチングし、半導体基板の素子分離領域となる領域に素子分離溝を形成し、素子分離溝を絶縁膜で埋め込み素子分離絶縁膜を形成する半導体装置の製造方法において、溝を形成する工程では、マスク膜の厚さに相当する深さよりも浅い溝を形成する。

(もっと読む)

半導体装置

【課題】小型化を実現し、かつ耐圧の高い半導体装置を提供すること。

【解決手段】活性領域10と分離領域30との間に設けられた耐圧構造部20は、順方向耐圧構造領域40と逆方向耐圧構造領域50とからなる。順方向耐圧構造領域40および逆方向耐圧構造領域50には、複数のフィールドリミッティングリング(FLR)41,51と、複数のフィールドプレート(FP)44,54が設けられている。複数のFP44のうち、最も逆方向耐圧構造領域50のFP(第1順方向FP)45は、分離領域30側に張り出すように設けられている。複数のFP54のうち、最も順方向耐圧構造領域40のFP(第1逆方向FP)55は、活性領域10側に張り出すように設けられている。順方向の電圧印加時、第1逆方向FP55は、分離領域30から伸びる空乏層を止める。逆方向の電圧印加時、第1順方向FP45は、活性領域10から伸びる空乏層を止める。

(もっと読む)

トレンチにより制限された分離拡散領域を備えた相補型アナログバイポーラトランジスタ

【課題】表面上に素子をより高密度に実装する。

【解決手段】第1のトレンチと第2のトレンチとの間の位置において、エピタキシャル層の表面から基板へと下方に延在するドーパントのウェルは、エピタキシャル層の背景ドーピング濃度とは異なるドーピング濃度を有し、エピタキシャル層の残りの部分と第1および第2の接合を形成する。第1の接合は、第1のトレンチの底部から基板に延在し、第2の接合は、第2のトレンチの底部から前記基板に延在する。ウェルおよび第1および第2のトレンチは分離構造を構成し、分離構造は、分離構造の一方側のエピタキシャル層に形成された第1の素子と分離構造の他方側のエピタキシャル層に形成された第2の素子とを電気的に分離する。分離構造による電気的分離は第1および第2のトレンチとPN接合とによってもたらされ、ウェルは第1の導電型の材料でドープされ、基板およびエピタキシャル層は、第1の導電型とは反対の第2の導電型の材料でドープされ、第1および第2の接合はPN接合である。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】微細化が進んだ場合であってもトランジスタのカットオフ特性を改善する。

【解決手段】半導体基板100上に形成されるp型ウェル2には、ビット線BLの長手方向に沿って形成されたトレンチ3に素子分離絶縁膜4が埋め込まれている。素子分離絶縁膜4によりp型ウェル2が分離され、メモリトランジスタが形成される素子形成領域2Aが形成される。素子分離絶縁膜4にはボロン等のp型不純物が注入されており、その不純物濃度は、p型ウェル2の不純物濃度よりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル電位固定用のウェル給電用素子を設ける際に、縦型MOSトランジスタ間に素子分離用の埋込絶縁層を必要とせず、素子分離用の埋込絶縁層の形成に必要な面積を削減して、半導体装置の高集積化を図る。

【解決手段】半導体基板1に形成された第1導電型のウェル2内に、ウェル給電用素子Xと縦型MOSトランジスタYとが備えられ、ウェル給電用素子Xは、ウェル2と同じ導電型のボディ領域からなるピラー部P1を有し、ピラー部P1の上部には、第1導電型のウェル2の濃度よりも高い濃度を有する第1導電型の第1不純物拡散層13を備え、縦型MOSトランジスタYは、ウェル2と同じ導電型のボディ領域からなるピラー部P2を有し、かつ縦型MOSトランジスタYのピラー部P2の上部には、第2導電型の第2不純物拡散層7を備えることを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置

【課題】誤動作や素子破壊が生じにくい高耐圧ドライバとして使用することができる半導体装置において、容易に製造が可能な構成とすること。

【解決手段】p+半導体基板1上に低濃度のpエピタキシャル層27を積層し、その表面層に浮遊電位基準回路形成領域21となるn半導体領域2と、GND基準回路形成領域22となるn半導体領域202と、高耐圧接合終端構造23としてn半導体領域2に接してn半導体領域2を囲むn半導体領域8を形成する。n半導体領域2およびn半導体領域202の周囲を囲むように、p+半導体基板1に達するトレンチ構造7を形成し、トレンチの側面および底面に沿って高濃度のトレンチ壁p+半導体領域51を形成し、その内側に電極16を形成する。電極16に接地電位GNDを印加し、トレンチ壁p+半導体領域51の電位を接地電位GNDとする。

(もっと読む)

半導体装置、及びその製造方法

【課題】、サイズを小さくできると共に、外部からのノイズに強く、漏洩電流が抑制された半導体装置及びその製造方法を提供すること。

【解決手段】 例えば、半導体基板10と、半導体基板10に形成されたP型のウェル10A(第1伝導型の第1領域)と、P型のウェル10A内に埋め込まれて形成されたN型のウェル10B(第2伝導型の第2領域)と、P型のウェル10A内であってN型のウェル10Bよりも上方に形成されたP型のウェル10C(第1伝導型の第3領域)と、P型のウェル10Cに形成された半導体素子20と、P型のウェル10CをN型のウェル10Bと共に取り囲むと共に、少なくとも底部がN型のウェル10Bと接触する深さを持って形成されたトレンチ型絶縁領域30と、を具備する半導体装置、及びその製造方法である。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体基板、および半導体基板の製造方法

【課題】化合物半導体と絶縁性材料との界面に形成される界面準位が低減した半導体装置を提供する。

【解決手段】閃亜鉛鉱型の結晶構造を有する3−5族化合物半導体と、3−5族化合物半導体の(111)面、(111)面と等価な面、または、(111)面もしくは(111)面と等価な面から傾いたオフ角を有する面に接する絶縁性材料と、絶縁性材料に接し、金属伝導性材料を含むMIS型電極とを備える半導体装置を提供する。

(もっと読む)

シリコン基板、デバイスの製造方法、デバイスおよびテスト方法

【課題】表面平坦性と金属汚染ゲタリング機能を確保しながら、STIと共存できる製造工程で500V以上の広い電圧領域の電気的アイソレイションを実現するとともに、貫通電極全体の深さにいたる物理的な金属移動の阻止のためのアイソレイシヨン構造を有する。

【解決手段】シリコン酸化膜を1um以上の幅で1um以上に深い溝を作り、溝の中にシリコン酸化膜を埋め、結晶欠陥のある基板でも500V以上に耐圧のあるアイソレイションを実現する。これによりシャロートレンチアイソレイションで高速で動作する既存デバイスと同一基板に電力デバイスを混載させることが可能となる。また、厚いアイソレイション材料で囲まれたシリコンを除去した空洞にメタルを埋め、金属汚染の拡散を防止した基板貫通電極を形成することにより、基板の積層を可能にする。これにより、電源からの配線を基板貫通で供給することで、ヒートシンクを兼ねた電力給電と、これにより動作する大電力デバイスと高速高集積のデバイスを積層させたデバイスを実現させる。

(もっと読む)

半導体装置の製造方法

【課題】拡散層の結晶欠陥を減少させることができ、さらにデッドエリアを減少させてチップサイズを小さくすることができる半導体装置の製造方法を提供する。

【解決手段】シリコンからなる基材1にトレンチ5を形成するトレンチ形成工程と、トレンチ5の内表面5a,5bに応力を緩和する緩衝層6を形成する緩衝層形成工程と、緩衝層6が形成されたトレンチ6に絶縁物7を充填する絶縁物充填工程と、基材1の絶縁物7が充填されたトレンチ5によって分離された領域P,Nに不純物を注入する不純物注入工程と、基材1を熱処理して、注入された不純物を熱拡散させる熱処理工程と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】拡散層の結晶欠陥を減少させることができ、さらにデッドエリアを減少させてチップサイズを小さくすることができる半導体装置の製造方法を提供する。

【解決手段】シリコンからなる基材1にトレンチ5を形成する工程と、トレンチ5の内表面5a,5bに、シリコンに対して電気的に不活性な元素のイオンを注入してアモルファス化し、応力を緩和する緩衝層6を形成する工程と、緩衝層6が形成されたトレンチ5に絶縁物7を充填する工程と、基材1の絶縁物7が充填されたトレンチ5によって分離された領域P,Nに不純物を注入する工程と、基材1を熱処理して、注入された不純物を熱拡散させる熱処理工程と、熱処理工程の後に、絶縁物7を除去する絶縁物除去工程と、絶縁物除去工程の後に、緩衝層6を酸化して酸化膜を形成する工程と、酸化膜を除去する酸化膜除去工程と、酸化膜除去工程により露出したトレンチ5の内側面を酸化する工程と、を有する。

(もっと読む)

1 - 20 / 46

[ Back to top ]