Fターム[5F033GG03]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930) | 絶縁性基板 (1,777)

Fターム[5F033GG03]の下位に属するFターム

透光性基板 (1,019)

Fターム[5F033GG03]に分類される特許

201 - 220 / 758

置換ゲート構造体を有するFET及びその製造方法

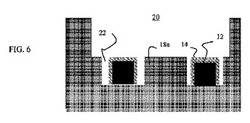

【課題】 マルチゲート型FETの置換ゲート構造体及びマルチゲート型FETの置換ゲート構造体の製造方法を提供する。

【解決手段】 MUGFET及びMUGFETを製造する方法が示される。MUGFETを製造する方法は、複数の活性領域の周りに一時的スペーサ・ゲート(図3の16)を形成することと、複数の活性領域の間を含む、一時的スペーサ・ゲートの上に誘電体材料(18a及び空間20内)を堆積させることとを含む。この方法は、誘電体材料(空間20内)の部分をエッチングして一時的スペーサ・ゲート(16)を露出させることと、一時的スペーサ・ゲートを除去して、活性領域と誘電体材料の残りの部分(18a)との間に空間を残すこととをさらに含む。この方法はさらに、活性領域と誘電体材料の残りの部分(18a)との間の空間(22)及び誘電体材料の残りの部分の上方をゲート材料で充填することを含む。

(もっと読む)

半導体素子及びその製造装置

【課題】汎用性が高く、低コストで省資源である方法を採用し、実用性に富み、任意の場所、任意の形状に金属又は半導体を二次元的又は三次元的に形成できる半導体素子及びその製造装置を提供する。

【解決手段】炭素材料と金属酸化物材料又は半導体酸化物材料とを有する還元反応構造1Aを持つ層構造30Aを準備し、還元反応構造1Aに対して局所的にエネルギーを集中することが可能で、かつ還元反応構造1Aに対して2次元的又は3次元的に走査することが可能な熱源を用い、この熱源によって酸化還元反応が起こる温度以上に還元反応構造1Aの一部を走査しつつ選択的に加熱して、炭素材料により金属酸化物材料又は半導体酸化物材料をそれぞれ金属又は半導体に還元し、所望の形状の金属領域又は半導体領域(金属層又は半導体層3A)を形成することによって製造されることを特徴とする半導体素子40Aとすることにより上記課題を解決する。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプス現象およびゲートリーク電流を抑制することが可能な電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ1は、基板10と、チャネル層11と、キャリア供給層12と、ソース電極21と、ドレイン電極22と、ゲート電極23と、ソース電極21とドレイン電極22との間でキャリア供給層12に積層されて電流コラプス現象を抑制する第1絶縁層31と、ドレイン電極22に対向する第1絶縁層31の端とドレイン電極22との間に形成された開口部40と、開口部40に露出したキャリア供給層12に積層された第2絶縁層32とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】実効誘電率を低減させて、高速かつ消費電力の低い半導体装置を実現する。

【解決手段】本発明の半導体装置は、基板と、基板上に形成された層間絶縁膜51、52と、層間絶縁膜51、52に埋め込まれたCu配線1と、Cu配線1上に形成された第二のバリア絶縁膜4と、を有する。第二のバリア絶縁膜4は、炭素二重結合、アモルファスカーボン構造及び窒素を含む有機シリカ膜である。

(もっと読む)

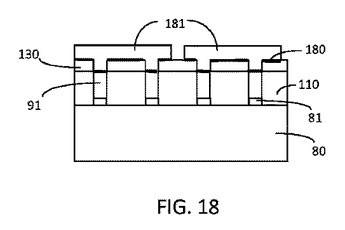

金属/有機誘電体界面でのクラックの低減

有機誘電体材料(110)中に埋め込まれた第2構造(91)への金属相互接続(181)を提供する方法であって、有機誘電体材料(110)中に埋め込まれた、例えば金属ピラー(91)のような第2構造を有する第1構造を得る工程と、少なくとも第1構造のいくつかの位置で、有機誘電体材料(110)の上に硬い層(130)を提供する工程であって、硬い層(130)は有機誘電体材料(110)の剛性より高い剛性を有する工程とを含む方法。この方法は、第1構造(91)と有機誘電体材料(110)との間の界面でクラックの無い相互接続構造を提供する。  (もっと読む)

(もっと読む)

電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器

【課題】絶縁層へのコンタクトホール形成時における、導電層の浸食や破損の抑制された電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器を提供する。

【解決手段】導電層形成工程によって形成されたソース電極20A、ドレイン電極20B、及び画素電極20Cを含む導電層20上に、該導電層20及び酸化物半導体層18を覆うように、無機材料を主成分とする無機絶縁層23を形成する。そして、この無機絶縁層23上にフォトレジスト膜30を形成してパターン状に露光した後に、現像工程において、現像液を用いて現像することでレジストパターン30B’を形成する。現像工程では、この現像液をエッチング液として用いて、無機絶縁層23の内のレジストパターン30B’から露出した領域を除去することによって導電層20の一部を露出させて、無機絶縁層22にコンタクトホール27を形成する。

(もっと読む)

薄膜トランジスタを備えた表示素子及びその製造方法

【課題】工程を単純化することのできる酸化物薄膜トランジスタを備えた表示素子及びその製造方法を提供する。

【解決手段】表示素子は、第1基板120及び第2基板140と、第1基板の画素領域に形成され、ゲート電極121、ゲート絶縁層126、酸化物半導体層122、並びにソース電極123及びドレイン電極124からなる薄膜トランジスタと、第1基板のゲートパッド領域に形成されたゲートパッド118、及び第1基板のデータパッド領域に形成されたデータパッド119と、ゲートパッド領域のゲート絶縁層上に形成され、コンタクトホールを介してゲート電極に接続する金属層155と、第1基板の全体にわたって形成された保護層128と、画素領域の保護層に形成された画素電極と、ゲートパッド領域に形成された第1透明導電層129a及びデータパッド領域に形成された第2透明導電層129bと、基板間に形成された液晶層130とから構成される。

(もっと読む)

自己整合ローカル・インターコネクト・プロセスにおけるゲートへの選択的なローカル・インターコネクト

【解決手段】

半導体デバイス生産プロセスは、ハードマスク(112)を用いて半導体基板上にトランジスタのゲート(102)を形成することを含む。ハードマスクは、ゲート上の1つ以上の選択された領域で選択的に除去される。選択された領域でのハードマスクの除去によって、実質的にトランジスタ上にある少なくとも1つの絶縁層を通してゲートが上部金属層に接続できる。導電性材料が、少なくとも1つの絶縁層を通して形成された1つ以上のトレンチ内に堆積される。導電性材料は、少なくとも1つの選択された領域内でゲートへのローカル・インターコネクトを形成する。

(もっと読む)

半導体発光デバイス上に誘電体層を形成する方法

n型領域とp型領域との間に配置された発光層を有する半導体構造が形成される。n型領域の一部上に第1のメタルコンタクトが形成され、p型領域の一部上に第2のメタルコンタクトが形成される。第1及び第2のメタルコンタクトは半導体構造の同一面上に形成される。第1のメタルコンタクトと第2のメタルコンタクトとの間の誘電体材料が配置される。該誘電体材料は、半導体構造の一部、第1のメタルコンタクトの一部、及び第2のメタルコンタクトの一部と直接的に接触する。第1のメタルコンタクトの表面と、第2のメタルコンタクトの表面と、該誘電体材料の表面とを含む平坦面が形成される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】新たな工程を追加することなく信頼性の高い半導体装置およびその製造方法を提供すること。

【解決手段】半導体素子を表面側に有する基板11と、半導体素子を覆うように基板11に積層された第1絶縁膜12と、第1絶縁膜12を厚さ方向に貫通する貫通孔の内面に積層されたバリア導電層13を介して貫通孔内に埋め込まれたコンタクトプラグ14と、第1絶縁膜12の表面に形成されてコンタクトプラグ14を介して半導体素子と電気的に接続された1種類以上の機能層とを備え、前記機能層は、バリア導電層13の材料と同じ材料からなり第1絶縁膜12の表面の所定領域に積層された第1バリア導電層13と、第1バリア導電層13上に、直接積層されるか、または第2絶縁膜15を介して積層されるか、またはそれらの両方の形態で積層された第2バリア導電層16と、第2バリア導電層16に積層された導電層17とを有してなることを特徴とする半導体装置。

(もっと読む)

導電膜パターン及び導電膜パターンの形成方法

【課題】膜厚のばらつき及び表面の平坦性に優れ、基材との十分な密着性を有する導電膜パターンを、複雑、高価な設備、工程を必要とせずに形成する導電膜パターン及びその形成方法を提供する。

【解決手段】金属微粒子含有インクを基材上に配置し、焼成することにより形成される導電膜パターンにおいて、前記基材のインク被配置面に、有機塩あるいは無機塩の含有されたプライマー層が形成されているものであることを特徴とする導電膜パターン。

(もっと読む)

半導体装置及びその製造方法

【課題】高温環境下での絶縁膜の腐食を抑制して、絶縁不良を回避した半導体装置及びその製造方法を提供することことを課題とする。

【解決手段】半導体基板11上にエピタキシャル成長により第1絶縁膜12が積層形成され、この第1絶縁膜12上には、耐熱性の電極13が選択的に形成され、この電極13の上部には、シリカガラスを主成分とする層間絶縁膜14が形成され、この層間絶縁膜14の表面には絶縁バリア膜15が形成され、この絶縁バリア膜15の上には、Alの配線16が形成され、絶縁バリア膜15は、絶縁性の窒化物、炭化物、窒化炭化物の単層膜、多層膜、または混合膜で構成されている。

(もっと読む)

ポリマの指向性自己組織化を利用するサブリソグラフィ構造の形成方法

【課題】 ポリマの指向性自己組織化を利用するサブリソグラフィ構造の形成方法を提供する。

【解決手段】 ブロック・コポリマの自己組織化を含む方法であって、目標とするCD(限界寸法)を有する開口部(1つ又は複数の基板内の)から開始して、ホールを規則的な配列又は任意の配列に形成する方法を説明する。重要なことに、形成されたホールの平均直径の百分率ばらつきは、最初の開口部の平均直径の百分率ばらつきより小さくなる。形成されたホール(又はビア)を下層の基板に転写することができ、次にこれらのホールを金属導体のような材料で埋め戻すことができる。本発明の好ましい態様は、22nm以下の技術ノードにおいても、より狭いピッチ及びより優れたCDの均一性を有するビアの作成を可能にする。

(もっと読む)

半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器

【課題】生産性に優れた半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板7の一方の面側に、トランジスタ4のゲート絶縁体層44を形成する第1の工程と、ゲート絶縁体層44上に、厚さ方向に貫通する貫通部91を備える絶縁体層9を形成する第2の工程と、貫通部91内の底部付近のゲート絶縁体層44上、および、貫通部91の周囲の絶縁体層9上に、気相成膜法により同時にかつ互いに接触しないようにそれぞれ電極を形成し、ゲート絶縁体層44上に形成された電極を用いて、ゲート電極45を形成するとともに、絶縁体層9上に形成された電極を用いて、画素電極6を形成する第3の工程とを有する。また、平面視で、貫通部91の開口部の縁が、当該貫通部91の底部の縁より内側に位置する。

(もっと読む)

半導体構造体及びその形成方法

【課題】 相互接続構造の信頼性及び拡張性を改善する相互接続構造のための冗長金属拡散バリア層を提供する。

【解決手段】 冗長金属拡散バリア層は、誘電体材料内に設けられた開口内に配置され、且つ開口内に存在する拡散バリア層及び導電性材料の間に配置される。冗長拡散バリア層は、Ru並びに純粋なCo若しくはN,B及びPのうちの少なくとも1つを含むCo合金からなる単層若しくは多層構造である。

(もっと読む)

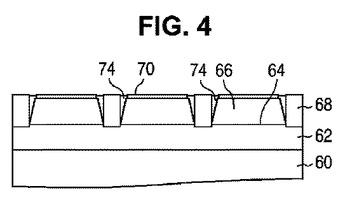

ブロック共重合体を用いてホール又はビアを有するデバイスを形成する方法

【課題】 ブロック共重合体を用いて所定の位置にホール又はビアを有するデバイスを形成する方法を提供する。

【解決手段】 例えば、光リソグラフィを用いて、輪郭を付けられた凸状のセグメントによって与えられる断面を有する開口部を基板内に形成する。開口部の断面は、例えば、重なった円形領域によって与えることができる。側壁は、種々の点で隣接し、そこで突起を画定する。ブロック共重合体を含むポリマーの層を開口部及び基板の上に塗布し、自己集合させる。開口部内に個別分離ドメインが形成され、これらを除去してホールを形成し、これを下層の基板に転写することができる。これらのドメイン及びこれらの対応するホールの位置は、側壁及びそれらに付随する突起によって所定の位置に誘導される。これらのホールを隔てる距離は、何も側壁がない場合にブロック共重合体(及び何れかの添加剤)が自己集合したとする場合よりも大きく又は小さくすることができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】

使用現場で使用者や顧客の要望に応じて、回路システムを形成することのできる薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】

薄膜トランジスタ装置において、TFTにより構成した複数の集積回路ブロック1,2と、これらの集積回路ブロックを相互に接続するための網目状に交差したマトリックス配線3、4、5、6を設ける。相互の集積回路ブロック間の接続は、使用現場で使用者や顧客の要望に応じて導電性材料を印刷等により、マトリックス配線の各々の配線交差部に選択的に設けることにより行い、所望の回路システムを構成する。

(もっと読む)

寄生容量が低減されたSOIボディ・コンタクト型FETのための方法

【課題】

ボディ・コンタクトを半導体オン・インシュレータ・デバイスに設け、それにより、デバイスに寄生容量の低減をもたらすこと。

【解決手段】

1つの実施形態において、本発明は、絶縁層の上を覆うように配置された半導体層を含む基板であって、半導体層は、半導体ボディと、半導体ボディの外周の周りに存在する分離領域とを含む基板と、基板の半導体層の上を覆うゲート構造体であって、半導体ボディの上面の第1の部分上に存在するゲート構造体と、非シリサイド半導体領域によって半導体ボディの第1の部分から分離される半導体ボディの第2の部分と直接物理的に接触しているシリサイド・ボディ・コンタクトとを含む、半導体デバイスの製造方法を提供する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

201 - 220 / 758

[ Back to top ]