Fターム[5F033GG03]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930) | 絶縁性基板 (1,777)

Fターム[5F033GG03]の下位に属するFターム

透光性基板 (1,019)

Fターム[5F033GG03]に分類される特許

141 - 160 / 758

結晶化シリコン層の製造方法、半導体装置の製造方法、電気光学装置の製造方法、半導体装置、電気光学装置および投射型表示装置

【課題】金属原子が内部に拡散、侵入せず、かつ、結晶化方位や粒径を制御することのできる結晶化シリコン層の製造方法、かかる方法を利用した半導体装置の製造方法、電気光学装置の製造方法、半導体装置、電気光学装置および投射型表示装置を提供すること。

【解決手段】結晶化シリコン層を形成するにあたって、基板本体10d上に金属触媒層8および第1非結晶シリコン層4xを形成した後、熱処理を行ない、第1非結晶シリコン層4xと金属触媒層8との間での相互拡散により、第1非結晶シリコン層4xと金属触媒層8とを入れ替える。その際、第1非結晶シリコン層4xは、多結晶シリコン層4yに変化する。金属触媒層8を除去した後、開口部15aを備えた絶縁層15、および第2非結晶シリコン層1xを形成した状態で熱処理を行ない、第2非結晶シリコン層1xを、開口部15aの底部で多結晶シリコン層4yと接している部分を起点にして結晶化させる。

(もっと読む)

窒素ドープされたアモルファスカーボンハードマスク

電界効果トランジスタを形成するための方法および電界効果トランジスタ・デバイス

3次元集積のための裏側ダミー・プラグを含む半導体構造およびこれを製造する方法

有機積層膜

【課題】複雑な工程を経ることなく、テトラチアフルバレン誘導体と電子受容性化合物とを積層させるだけで、簡便かつ高電気伝導度を有する積層膜を提供する。

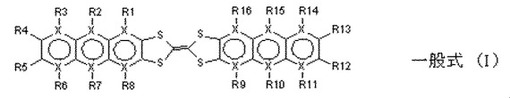

【解決手段】一般式(I)で表されるテトラチアフルバレン誘導体と電子受容性化合物の積層膜

(式(I)中、Xは炭素原子または硫黄原子または窒素原子から選択される原子であり同一でも異なっていても良い。Xに炭素原子及び窒素原子が選択される場合においてR1〜R16は水素原子、ハロゲン原子、置換および無置換のアルキル基またはアルコシキ基またはチオアルコキシ基から選択される基であり同一でも異なっていても良い。)。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

半導体装置および半導体装置の製造方法

【課題】ディッシングを抑制することができる半導体装置の構造を実現する。

【解決手段】半導体装置200は、基板(シリコン基板)と、基板上に設けられた絶縁層(層間絶縁膜201)と、層間絶縁膜201に設けられた第1の配線溝と(配線溝202)、配線溝202に埋め込まれた第1の金属膜(Cuめっき膜206)と、を備え、配線溝202の底部が、凸部形状を有する。

(もっと読む)

紫外線硬化型インクジェット記録用インク、それから得られた絶縁膜、電子素子及び電子素子の製造方法

【課題】 合成樹脂基板及び電極の両方に対するレベリング性に優れ、平滑性及び絶縁性に優れた硬化膜が得られる紫外線硬化型インクジェット記録用インク、それから得られた絶縁膜、電子素子及び電子素子の製造方法を提供する。

【解決手段】 エネルギー線硬化性化合物、光重合開始剤、及び表面張力調整剤を含有し、硬化性を有さないポリマーを含まず、25℃における粘度が100mPa・sec以下、表面張力が22〜35mN/m、かつインク硬化膜の体積抵抗率1013Ω・cm以上であり、絶縁破壊強度1.2MV/cm2以上である、絶縁膜を形成するためのソルベントフリー紫外線線硬化型インクジェット記録用インク、それを硬化してなる絶縁膜等を提供する。

(もっと読む)

新規有機導電性膜を使用した有機電極

【課題】複雑な工程を経ることなく、テトラチアフルバレン誘導体と電子受容性化合物とを積層させるだけで、簡便かつ高電気伝導度を有する積層膜を提供する。

【解決手段】一般式(I)で表されるテトラチアフルバレン誘導体と電子受容性化合物の積層膜

(式(I)中、Xは炭素原子または硫黄原子または窒素原子から選択される原子であり同一でも異なっていても良い。Xに炭素原子及び窒素原子が選択される場合においてR1〜R16は水素原子、ハロゲン原子、置換および無置換のアルキル基またはアルコシキ基またはチオアルコキシ基から選択される基であり同一でも異なっていても良い。)。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】W等の金属膜の酸化を防止しつつ、金属膜上に低温で酸化膜を形成することができる半導体装置の製造方法を提供する。

【解決手段】表面に金属膜が形成された少なくとも1枚のウエハ310を処理室318内に搬入する工程と、金属膜を含むウエハ310表面にシリコンを含む酸化膜を形成する工程と、を少なくとも備える半導体装置の製造方法であって、酸化膜の形成工程は、ウエハ310を所定の温度に加熱しながら、シリコン原子を含む第1の反応物質を処理室318内に供給する工程と、ウエハ310を所定の温度に加熱しながら、酸素原子を含む第2の反応物質と、水素とを処理室318内に供給する工程と、を有し、処理室318内の加熱温度と、水素に対する第2の反応物質の供給比を制御することにより、金属膜の酸化を制御する。

(もっと読む)

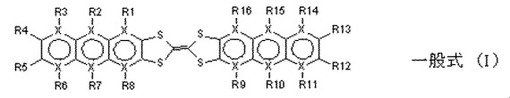

ビア及びエッチングされた構造におけるコンフォーマル絶縁層の形成方法及びパターン形成方法

マスク層の下にアンダーカット形状を形成するエッチングプロセスによって基板にビアが形成される。ビアはコンフォーマルな絶縁層で覆われ、この構造にエッチングプロセスを実施して水平面から絶縁層を取り除くと共にビアの垂直な側壁の絶縁層を残す。ビアの上部領域はエッチバックプロセスの際、アンダーカットハードマスクによって保護される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】低容量且つ高温特性が良好な素子分離領域を有する高速なMIS電界効果トランジスタを提供する。

【解決手段】半導体基板1にウエル領域2が設けられ、ウエル領域2内には上部、下部及び側面にシリコン酸化膜3を有し、内部が空孔4に形成されたトレンチ素子分離領域が選択的に設けられ、トレンチ素子分離領域により画定されたウエル領域2が設けられた半導体基板1上にゲート酸化膜9を介してゲート電極10が設けられ、ゲート電極10の側壁にサイドウォール11が設けられ、ウエル領域2が設けられた半導体基板1には、ゲート電極10に自己整合して低濃度のソースドレイン領域(6、7)及びサイドウォール11に自己整合して高濃度のソースドレイン領域(5、8)が設けられ、高濃度のソースドレイン領域にはそれぞれバリアメタル14を有する導電プラグ15を介してバリアメタル17を有する配線18が接続されている構造からなるMIS電界効果トランジスタ。

(もっと読む)

マンガン含有低誘電率膜及びその製造方法、半導体装置の製造方法並びに成膜装置

【課題】マンガン含有材料を利用して、低誘電率膜への銅の拡散を防止する。

【解決手段】成膜装置100では、制御部70の制御に基づき、処理容器1内を真空にして、ヒーター6によりウエハWを加熱しつつ、シャワーヘッド11のガス吐出孔13a,13bからウエハWへ向けて低誘電率材料とマンガン含有材料とを含む成膜ガスを供給する。高周波電源23からシャワーヘッド11に高周波電力を供給することにより、成膜ガスを解離させ、処理容器1内に成膜ガスのプラズマを生成させる。このプラズマによって、ウエハWの表面にMnを含有するSiCOH膜を成膜する。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】金属シリサイド膜と銅コンタクトプラグ本体との間の拡散バリア層として、薄膜の酸化マンガンで構成された拡散バリア層を用いてはいるものの、金属シリサイド膜への銅原子の拡散、侵入を確実に抑止することができるようにする。

【解決手段】本発明のコンタクトプラグ10は、半導体装置の絶縁膜4に設けられたコンタクトホール5に形成され、コンタクトホール5の底部に形成された金属シリサイド膜3と、コンタクトホール5内で金属シリサイド膜3上に形成され、非晶質でシリコンを含む第1の酸化マンガン膜6aと、その第1の酸化マンガン膜6a上に形成され、微結晶を含む非晶質の第2の酸化マンガン膜6bと、その第2の酸化マンガン膜6b上に、コンタクトホール5を埋め込むように形成された銅プラグ層7と、を備えることを特徴としている。

(もっと読む)

半導体装置、三次元集積回路およびその製造方法

【課題】回路動作時の基板での損失を低減し、表面および裏面の両面において多層配線を形成することで配線の自由度を向上させ、なおかつ貫通配線の配線長を短縮して信号の伝達を高速化する。

【解決手段】薄膜半導体素子2はSOIウェーハを用いて形成し、そのシリコン基板から取り外されているため、素子厚さは埋め込み酸化膜を含めても、例えば2μm以下である。また、貫通配線6は、装置の表面と裏面を貫通するのではなく、薄膜半導体素子に隣接して、コンタクトビア形成時に一括で形成するため、その直径が薄膜半導体素子のコンタクトビアと同程度で、長さが薄膜半導体素子の厚さと同程度である。

(もっと読む)

半導体装置の製造方法

【課題】 組み立て工程やCMP工程時における剥離を抑制した、低誘電率層間絶縁膜の製造方法とそれを用いた半導体装置を提供する。

【解決手段】低誘電率層間絶縁膜の成膜の際、高周波と低周波の2周波を切り替え、膜厚方向に膜特性の変調をかけることで、低誘電率を保持したまま密着強度を向上させる。プラズマ発生のための高周波と低周波が同一電極から印加される。そして絶縁膜の成膜開始時あるいは成膜終了時の少なくとも一方において、低周波の入力が成膜開始時及び成膜終了時を除いた他のタイミングより高い。例えば絶縁膜は、厚さ方向における少なくともどちらか一方の端部が、高周波と低周波の2周波により密着層となり、密着層以外の部分は低周波の入力を低下あるいは0にすることで低誘電率絶縁膜となる。

(もっと読む)

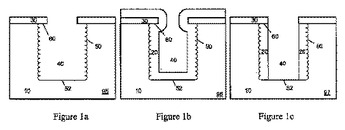

ICデバイスのエンハンストされた熱放散のための突出するTSV

集積回路デバイス(100)が、基板パッド(102)を含む上面を有する基板(110)、及び能動回路を含む上部半導体表面(107)と(底面)106とを含む半導体基板(105)を含む複数の基板貫通ビア(115)ダイを含む。上部半導体表面(107)は、基板の上面上の基板パッドに結合されるボンドコネクタ109を含む。複数の基板貫通ビア(TSV)が、底面から外に延びる突出するTSVティップ(121)に上側半導体表面から延びる内部金属コア(125)を含む。複数のTSVの少なくとも1つが、そこへの如何なる電気的接続もない、突出するTSVティップを有し、TSVダイの底面からの熱消散を可能にするための付加的な表面領域を提供するダミーTSV(120)である。

(もっと読む)

(もっと読む)

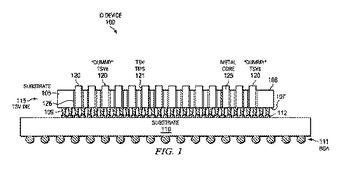

半導体装置の製造方法

【課題】 半導体装置を3次元実装するため、狭ピッチ、微小径、高アスペクト比の開孔に空隙を形成することなく導電性材料を埋め込み、低コストで貫通電極を形成する。

【解決手段】 半導体基板10上の絶縁膜層11、パッド電極12が形成された面に導電性の接着剤層13を用いて導電性のサポート基板14を貼り合わせする。この状態で半導体基板10の裏面を研磨して薄化した後、開孔15を形成する。さらにサポート基板14、接着剤層13を通じて複数のパッド電極12に同時に同電位を与え、ボトムアップ成長のメッキ法で開孔15に銅を埋め込み、Cuプラグ16、Cuポスト17からなる貫通電極を形成する。このようにすると開孔15のアスペクト比が極端に高くならないので銅が良好に埋め込まれ、また半導体基板10の表裏反転を伴う工程処理回数が低減できる。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

パッケージおよびその製造方法

【課題】工程時間を短縮し、平坦度(又は、ボンディングの均一性)を高め、絶縁層(絶縁基板)とチップとの間の接着力が向上したパッケージおよびその製造方法を提供することを目的とする。

【解決手段】本発明のパッケージは、パターニング層上に形成された第1導電層と、前記パターニング層上に前記第1導電層を埋め込むように形成された絶縁層と、前記絶縁層の外面に形成された第2導電層と、前記第1導電層と第2導電層とを電気的に接続するように前記絶縁層の内部に形成された第3導電層とを含むことを特徴とする。

(もっと読む)

141 - 160 / 758

[ Back to top ]