Fターム[5F033JJ04]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 半導体(基板を除く) (666) | 多結晶Si (516)

Fターム[5F033JJ04]に分類される特許

101 - 120 / 516

半導体装置の製造方法および半導体装置

【課題】縦型MOSトランジスタを備えた半導体装置を形成する際のゲート電極とコンタクトプラグとの短絡を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、前記半導体基板上にシリコン窒化膜(SiN膜)からなるマスク窒化膜のパターンを形成したのちに、溝および半導体ピラーを前記半導体基板に形成する第一工程と、前記マスク窒化膜を残存させたまま、前記溝を覆うゲート絶縁膜を形成したのちに前記半導体ピラーよりも低い高さのゲート電極を形成する第二工程と、前記溝を覆うように、シリコン酸窒化膜(SiON膜)からなるライナー膜を形成したのちに、前記ライナー膜上を覆い、かつ、前記溝内を充填するように層間膜(SOD膜)を形成する第三工程と、前記マスク窒化膜をエッチングにより選択的に除去する第四工程と、を採用する。

(もっと読む)

段階化キャップ層を有するパターニング可能low−k誘電体配線構造、エアギャップ包含配線構造、および製作方法

【課題】パターニングされた段階化キャップ層の表面上に配される少なくとも1つのパターニングされ且つ硬化されたlow−k物質を含む配線構造を提供する。

【解決手段】少なくとも1つの硬化され且つパターニングされたlow−k物質およびパターニングされた段階化キャップ層は、その中に組み込まれる導電的充填領域を各々有する。パターニングされ且つ硬化されたlow−k物質は、1つ以上の酸感受性イメージング可能基を有する機能性ポリマー、コポリマー、あるいは少なくとも2種の任意の組み合わせのポリマー類もしくはコポリマー類またはその両方を含むブレンドの硬化生成物であり、段階化キャップ層はバリア領域として機能する下部領域および恒久的な反射防止膜の反射防止特性を有する上部領域を含む。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】画素、メモリ部、又はCMOS回路等に配置されたトランジスタのチャネル形成領域213、214と重なる第1の配線(ゲート電極)の一部または全部と第2の配線(ソース線またはドレイン線)154、157とを重ねる。また、ゲート電極と第2配線154、157の間には第1の層間絶縁膜149及び第2の層間絶縁膜150cを設け、寄生容量を低減した半導体装置である。

(もっと読む)

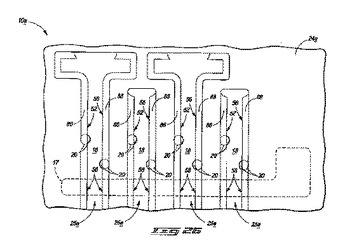

3次元半導体メモリ装置及びその製造方法

【課題】3次元半導体メモリ装置及びその製造方法を提供する。

【解決手段】本装置は、積層された導電パターン、導電パターンを貫通する活性パターン及び導電パターンと活性パターンとの間に介在される情報貯蔵膜を含む少なくとも1つのメモリ構造体を含み、活性パターンは積層された下部及び上部貫通ホールを各々満たす下部及び上部半導体パターンを含むことができる。1つのメモリ構造体を構成する情報貯蔵膜は同一の工程段階を利用して実質的に同時に形成され、1つのメモリ構造体を構成する下部及び上部貫通ホールは互いに異なる工程段階を利用して順に形成され得る。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、通常のコンタクトとシェアードコンタクトとを同時に形成することが難しくなり、接合リーク不良やコンタクト抵抗の上昇が発生する等の課題があった。

【解決手段】ロジックSRAM部のゲート配線6の側壁に形成するサイドウォール9と、拡散層11の表面に形成するシリサイド層13とゲート配線6のシリサイド層15とを電気的に接続するドープトポリシリコン18と、ドープトポリシリコン18と第1層アルミ配線とを電気的に接続するWプラグ26と、ロジックSRAM部の拡散層11の表面のシリサイド層と第1層アルミ配線とを電気的に接続するWプラグ25とを備えるものである。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、配線層の平坦性を保つためのダミーパターンを有する半導体装置とその製造方法を提供することを目的とする。

【解決手段】半導体装置の機能を実現するうえで必要な機能パターンと、半導体装置の所定の層に、前記機能パターンと共に複数のダミーパターンとを備え、第一の大きさの複数のダミーパターンが配置され、前記第一の大きさの複数のダミーパターンが配置されない領域に、第二の大きさの複数のダミーパターンが配置され、前記第一の大きさの複数のダミーパターンと前記機能パターンとの間に前記第二の大きさの複数のダミーパターンが配置され、第一所定方向に配置された前記第一の大きさの複数のダミーパターンと、第二所定方向に配置された前記第二の大きさの複数のダミーパターンとは隣り合い、前記第一の大きさのダミーパターン間の幅は、前記第二の大きさのダミーパターン間の幅よりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】貫通電極を有し縦方向に積層される半導体装置であって、設計の自由度を拡大することができる半導体装置およびその製造方法を提供することを目的とする。

【解決手段】半導体基板1と、相互に離間して第1の主表面10から半導体基板1の深さ方向に向かって設けられた電極30aおよび電極30bと、電極30aおよび電極30b同士の間を結び半導体基板1を貫通することなく第1の主表面10から半導体基板1の深さ方向に向かって設けられた配線部40aとを備えている。電極30aは、半導体基板1を貫通して第2の主表面20に達する貫通電極となっている。貫通電極を有し縦方向に積層される半導体装置において、配線部40aを備えていることにより設計の自由度を拡大することができる。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】35mmデジタル一眼レフ・カメラ用のCMOSイメージ・センサは、チップサイズが非常に大きく、200φウエハ上に20チップ程度しか配置できない。従って、ウエハあたり、ショート欠陥が数個存在しただけで、歩留まりが大きく低下する。そこで、これらの欠陥を一般的なレーザ・トリミング技術により、除去することを検討したが、サブ・ミクロン・オーダの加工は非常に困難であることが判明した。

【解決手段】本願発明は、ピクセル・アレイ、これを横断又は縦断する複数のグローバル配線、および、各ピクセル内に設けられたローカル配線を有する半導体集積回路装置であって、第1のグローバル配線と、第1のピクセル内にあるローカル配線との間のショート不良箇所が、そのローカル配線の機能を実質的に破壊し、前記第1のグローバル配線の機能を実質的に破壊しないように、レーザ・リペア処理された修正処理部を有するものである。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法及び電子機器

【課題】光電変換部の面積を縮小することなく、光電変換部から電荷電圧変換部への信号電荷の転送性を改善することができる仕組みを提供する。

【解決手段】本発明の固体撮像装置は、光電変換部に蓄積された信号電荷を電荷電圧変換部26に転送する転送ゲート32と、電荷電圧変換部26で生成された信号電圧を出力するための配線42と、電荷電圧変換部26と配線42との電気的な接続を中継する中継電極38とを備える。中継電極38は、電荷電圧変換部26に電気的に接続するコンタクト部38cと、プラグ41を介して配線42に電気的に接続するコンタクト部38fと、転送ゲート32の上面に絶縁膜35を介して対向することにより当該転送ゲート32と容量的に結合する容量結合部38a,38bとを有する。

(もっと読む)

半導体装置の製造方法

【課題】後続の工程に伴う埋め込みゲートの酸化を防止し、ビットラインコンタクト及びストレージノードコンタクトと基板との間のコンタクト面積を増加させ、コンタクト抵抗を低減し、ビットラインコンタクト及びストレージノードコンタクトと埋め込みゲートとの間のGIDLを低減し、自己整合コンタクト不良を防止することのできる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板の全面にプラグ導電膜を形成するステップと、前記プラグ導電膜をエッチングしてランディングプラグを形成するステップと、前記ランディングプラグ間の基板をエッチングしてトレンチを形成するステップと、前記トレンチの表面上にゲート絶縁膜を形成するステップと、前記ゲート絶縁膜上に前記トレンチの一部を埋め込む埋め込みゲートを形成するステップと、を含むことを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】LDMOSFETを有する半導体装置では、ソース電極が裏面にあることから、表面のソース・コンタクト領域と裏面のソース電極間の電気抵抗を低減するため、上面からP型エピタキシャル層を貫通してP+型基板内に伸びるボロンを高濃度にドープしたポリ・シリコン埋め込みプラグが設けられている。このポリ・シリコン埋め込みプラグの周辺のシリコン単結晶領域に転位が発生しており、これにより、リーク不良が誘発されていることが明らかとなった。

【解決手段】本願発明は、相互に不純物濃度の異なる第1及び第2の半導体層の境界面を貫通するシリコン系プラグを有する半導体装置であって、このプラグの少なくとも内部は多結晶領域であり、この多結晶領域表面の内、先の境界面の両側近傍は、固相エピタキシャル領域で覆われている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】回路部の上部にメモリ部を形成し、回路部が高温にさらされても回路部の配線層やコンタクトが劣化しない不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板11と、メモリ部MUと、半導体基板とメモリ部との間の回路部CUと、を備える。メモリ部は、半導体基板の主面11aに垂直な第1方向に交互に積層された複数の電極膜WLと複数の絶縁膜14とを有する積層構造体MLと、積層構造体を第1方向に貫通する半導体ピラーSPと、電極膜と半導体ピラーとの交差部に対応して設けられた記憶部43と、を有す。回路部は、それぞれ第1、第2導電型のソース/ドレイン領域を有する第1、第2トランジスタ51n、51pと、シリサイドを含む第1配線W1と、ソース/ドレイン領域と同じ導電型のポリシリコンからなるコンタクトプラグC1、C2と、を有す。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの下部電極のダメージを抑制することができる半導体装置およびその製造方法を提供するものである。

【解決手段】本発明の半導体装置は、立設する複数の電極と、前記電極の立設を保持する第1の絶縁膜と、前記電極が貫通するように前記第1の絶縁膜に形成され、各々の前記電極の外周側面の少なくとも一部に接触する複数の孔部と、前記第1の絶縁膜に形成され、前記複数の孔部のうちその一部の孔部に連結する第1の開口と、前記第1の絶縁膜に形成され、前記複数の孔部のいずれの孔部に対してよりも前記溝部に近接する位置に配置すると共に前記複数の孔部のいずれにも連結しない第2の開口とを、備えたことを特徴とすることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】導電層を自己整合的に形成する場合において、第1の拡散層コンタクトプラグのコンタクトマージンを比較的大きく取る。

【解決手段】半導体装置10は、第1のシリコンピラー14Aと、第1のシリコンピラー14Aの上面に設けられ、導電性材料が充填されたスルーホール30aを有する層間絶縁膜30と、スルーホール30aの上側開口部に設けられた第1の拡散層コンタクトプラグDC1とを備え、スルーホール30aの下側開口部の面積は前記第1のシリコンピラー14Aの上面の面積に等しくなっているとともに、スルーホール30aの上側開口部の面積はスルーホール30aの下側開口部の面積より大きくなっており、それによって、スルーホール30a内の導電性材料の第1の拡散層コンタクトプラグDC1との接続面の面積が第1のシリコンピラー14Aの上面の面積より大きくなっている。

(もっと読む)

離間された導電配線に電気的接続を提供する方法

集積回路及び形成方法は、少なくとも1つの直線的に延在する導電配線の斜端に形成されたコンタクト領域を提供する。実施形態では、コンタクトランディングパッドを有する導電配線は、マスク材料に配線をパターン化することと、材料配線の延在方向に対して角度を形成するために少なくとも1つの材料配線を切断することと、マスク材料の斜端面から拡張部を形成することと、前記材料配線及び拡張部をマスクとして用いてエッチングすることによって基本的な半導体をパターン化することとによって形成される。他の実施形態では、少なくとも1つの導電配線は、斜端面を作るように導電配線の延在方向に対して角度を付けて切断されるとともに、電気的コンタクトランディングパッドは、斜端面にコンタクトして形成される。 (もっと読む)

半導体装置およびその製造方法

【課題】写真製版プロセスのマージンを大幅に拡大でき、かつマイクロローディング効果を低減することによって「開口不良」を抑制できるとともに「ショート」のプロセス裕度を確保しやすくし、かつコンタクト抵抗を低減できる半導体装置の製造方法を提供する。

【解決手段】活性領域に対して傾斜して延びるようにゲート電極層50と窒素を含む絶縁膜2とが積層される。シリコン酸化膜5が形成される。活性領域の幅より大きくかつ互いに隣り合う活性領域のピッチより小さい帯状の開口パターンが絶縁膜2に形成され、開口パターンから1対の不純物拡散領域の各々が露出させられる。開口パターンが導電層23で埋め込まれる。導電層23から1対の不純物拡散領域の各々に電気的に接続されたプラグ導電層23a、23bが形成されるとともに、プラグ導電層23a、23bの各上面と絶縁膜2の上面とが同一平面とされる。

(もっと読む)

半導体構造体及びその形成方法

【課題】 相互接続構造の信頼性及び拡張性を改善する相互接続構造のための冗長金属拡散バリア層を提供する。

【解決手段】 冗長金属拡散バリア層は、誘電体材料内に設けられた開口内に配置され、且つ開口内に存在する拡散バリア層及び導電性材料の間に配置される。冗長拡散バリア層は、Ru並びに純粋なCo若しくはN,B及びPのうちの少なくとも1つを含むCo合金からなる単層若しくは多層構造である。

(もっと読む)

寄生容量が低減されたSOIボディ・コンタクト型FETのための方法

【課題】

ボディ・コンタクトを半導体オン・インシュレータ・デバイスに設け、それにより、デバイスに寄生容量の低減をもたらすこと。

【解決手段】

1つの実施形態において、本発明は、絶縁層の上を覆うように配置された半導体層を含む基板であって、半導体層は、半導体ボディと、半導体ボディの外周の周りに存在する分離領域とを含む基板と、基板の半導体層の上を覆うゲート構造体であって、半導体ボディの上面の第1の部分上に存在するゲート構造体と、非シリサイド半導体領域によって半導体ボディの第1の部分から分離される半導体ボディの第2の部分と直接物理的に接触しているシリサイド・ボディ・コンタクトとを含む、半導体デバイスの製造方法を提供する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート電極部と容量コンタクトプラグとのショートを防止する。

【解決手段】複数のゲート電極部10と該ゲート電極部10間を接続する配線部との上に、耐エッチング膜17を備えたゲートハードマスク20を形成後、前記配線部上の前記耐エッチング膜17を除去する。これにより、CMP処理を経てコンタクトプラグ22を形成し、さらに、エッチングにより容量コンタクトホール24を開口して容量コンタクトプラグ25を形成した場合に、ゲート電極部10と容量コンタクトプラグ25とのショートを防止することができる。

(もっと読む)

集積回路の製造において複数の導電線を形成する方法、導電線アレイを形成する方法、および集積回路

集積回路の製造において導電線対を形成する方法は、基板上に受けられるダマシン材料にトレンチを形成することを含み、導電性材料34a/35aが、そのダマシン材料を覆ってそしてトレンチ内へ蒸着されてそのトレンチを過充填する。その導電性材料は、少なくともダマシン材料へと戻すように除去されて、そのトレンチ内に残っている導電性材料の少なくともいくらかが残される。エッチングがトレンチ内で導電性材料を通って縦方向に処理されて、トレンチ内に少なくとも第1および第2の導電線の長さの大部分に沿って横断面図において互いにミラー像となる第1および第2の導電線が形成される。他の装いが考えられる。  (もっと読む)

(もっと読む)

101 - 120 / 516

[ Back to top ]