Fターム[5F033JJ04]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 半導体(基板を除く) (666) | 多結晶Si (516)

Fターム[5F033JJ04]に分類される特許

61 - 80 / 516

半導体装置、その製造方法、および半導体装置を含む半導体パッケージ

【課題】装置特性の低下を防止するとともに、半導体基板と貫通電極の短絡を防止する半導体装置を提供する。

【解決手段】第1面と、第1面と対向してトレンチが形成された第2面とを有する基板と、基板内に形成されたビアホールを充填し、ビアホールの内壁から順にビアホール絶縁膜、障壁膜、および導電性接続部を有してなる貫通ビアと、第2面上に形成されて貫通ビアの一部領域を露出する開口部を有する絶縁膜と、トレンチ内に埋め込まれ、貫通ビアと電気的に接続される再配線と、を有し、絶縁膜は導電性接続部の一部領域と重複する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】レンチ2内に埋め込まれた埋め込み絶縁膜3の一部を除去することで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1を形成し、空隙AG1は、制御ゲート電極8下に潜るようにしてトレンチ2に沿って連続して形成する。

(もっと読む)

多相超低誘電膜の形成方法

【課題】誘電率が2.7以下であり、弾性計数および硬度の改善等、機械的特性を向上させた超低誘電率(k)膜、および膜の製造方法を提供する。

【解決手段】多相超低k誘電膜44は、Si、C、O、およびHの原子を含み、誘電率が約2.4以下であり、ナノサイズの孔または空隙を有し、弾性係数が約5以上であり、硬度が約0.7以上である。好適な多相超低k誘電膜44は、Si、C、O、およびHの原子を含み、誘電率が約2.2以下であり、ナノサイズの孔または空隙を有し、弾性係数が約3以上であり、硬度が約0.3以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

半導体装置、半導体装置の製造方法およびデータ処理システム

【課題】本発明はコンタクト開口をエッチングにより形成した場合にその下に位置する埋込絶縁膜がエッチングされないようにした構造の提供を目的とする。

【解決手段】本発明は、半導体基板と、半導体基板の主面に形成され活性領域を横断して素子分離領域まで延在するトレンチと、トレンチの下部側に形成された埋込型ゲート電極と、活性領域において埋込型ゲート電極の上方のトレンチ内を充填し、かつ、素子分離領域において埋込型ゲート電極の上方のトレンチ内を完全には充填せずにトレンチの内側面に接して配置されるサイドウォールを構成するキャップ絶縁膜と、素子分離領域においてサイドウォールの内側のトレンチを埋めて埋込型ゲート電極に接続形成されたパッドコンタクトプラグと、パッドコンタクトプラグおよびキャップ絶縁膜上を覆う層間膜と、パッドコンタクトプラグに接続するゲートコンタクトプラグとを具備してなる。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】メモリセル領域に埋め込みゲート電極を有し、周辺回路領域にプレーナ型ゲート電極と貫通電極を有する半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板50のメモリセル領域の溝部内に第一のゲート絶縁膜を介して、ワード線を埋め込み形成する工程と、周辺回路領域の前記半導体基板50上に、第二のゲート絶縁膜を介して周辺ゲート電極を形成する工程と、前記半導体基板50の主面上に層間絶縁膜と金属膜とを形成したのちに、前記金属膜をパターニングして、前記メモリセル領域の容量コンタクトパッドと前記周辺回路領域の局所配線127とを同時に形成する工程と、前記局所配線127の下面127a側を露出する開口151を形成したのちに導電体を充填することにより貫通プラグを形成する工程と、を採用する。

(もっと読む)

半導体装置の製造方法

【課題】容量コンタクトパッドと容量コンタクトプラグが一体となった構造を形成する。これにより、従来は2回、必要だったフォトリソグラフィ工程を1回に削減して、製造コストを低減する。

【解決手段】半導体装置の製造方法では、層間絶縁膜上に、開口を有するマスクパターンを形成する。このマスクパターンを用いて、層間絶縁膜をエッチングすることにより、開口の下の層間絶縁膜内に容量コンタクトホールを形成する。湿式エッチングにより、マスクパターン内の開口を大きくした後、開口内に導電材料を埋め込むことにより、それぞれ容量コンタクトプラグ及び容量コンタクトパッドを形成する。この後、容量コンタクトパッド上にキャパシタを形成する。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で横方向に成長するシリコン膜が連結されることを防ぎつつ、活性領域上に十分な厚みのシリコン膜を形成可能とした半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上に第1のシリコン膜12aを選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に第1のシリコン膜12aを覆うのに十分な厚みでマスク絶縁膜を埋め込んだ後、このマスク絶縁膜を第1のシリコン膜12aの表面が露出するまでエッチングにより除去する工程と、第1のシリコン膜12a上に第2のシリコン膜12bを選択的にエピタキシャル成長させる工程とを含む。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、微細化された埋め込みビット線を容易に形成可能であると共に、埋め込みビット線の抵抗値を低くすることで高性能化を実現可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板13の主面13aに形成された第1の溝15と、第1の溝15の底面15a、及び第1の溝15の底部15Aに位置するピラー26の側壁面26a,26bに設けられ、側壁面26aを露出する第1の開口部16A、及び側壁面26bを露出する第2の開口部16Bを有した絶縁膜16と、第1の開口部16Aから露出された側壁面26aに形成された半導体基板と反対導電型の下部不純物拡散領域18と、絶縁膜16を介して、第1の溝15の底部15Aに設けられ、第1及び第2の開口部16A,16Bを埋め込むと共に、下部不純物拡散領域18及び側壁面26bと接触し、かつ金属膜よりなる埋め込みビット線21と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】メモリセル間の短絡を防止した上で、活性領域上にシリコン膜が十分に形成された半導体装置を提供する。

【解決手段】半導体基板2の表層に埋め込み形成された素子分離膜8によって、活性領域7が区画された半導体装置1であって、前記活性領域7の側面17が露出するように、前記素子分離膜8の上面の一部が除去されて設けられた凹部と、前記凹部を埋め込みつつ、前記活性領域7の上面7d及び前記側面17と接するように設けられたシリコン膜10と、を有することを特徴とする。

(もっと読む)

垂直型トランジスタと埋め込みビットラインとを有する半導体メモリ素子及びその製造方法

【課題】垂直型トランジスタのドレイン領域と埋め込みビットラインとの間に抵抗接点(ohmic contact)を形成しつつも、その製造工程が簡単な半導体メモリ素子及びその製造方法を提供すること。

【解決手段】基板に形成されたトレンチによって上部へ突出した形のアクティブ領域と、アクティブ領域の上部に配置される第1の不純物領域と、アクティブ領域の下部に配置される第2の不純物領域と、第1の不純物領域と第2の不純物領域との間のアクティブ領域の側面に沿って配置されるゲート絶縁膜と、ゲート絶縁膜上に配置されるゲート電極膜と、そして、トレンチの下部でライナー膜によって第2の不純物領域と離隔するように配置される金属膜と、金属膜上で前記第2の不純物領域と直接接触されるように配置されるポリシリコン膜とからなる埋め込みビットラインとを備えることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】高さのばらつきが低減された埋め込みビット線を有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板内にビット線とワード線を有する半導体装置の製造方法において、半導体基板をエッチングして第1の方向に延在する第1の溝を形成することによって、複数の第1の半導体ピラーを形成する工程と、第1の半導体ピラーの側面の一部に拡散層を形成する工程と、隣接する前記第1の半導体ピラー間の前記第1の溝に、拡散層に接続するビット線を形成する工程と、第1の半導体ピラーと前記ビット線を覆う第1の絶縁膜を形成する工程と、第1の半導体ピラーの少なくとも一部が露出するように前記第1の絶縁膜に、第1の方向に直交する第2の方向に延在する第2の溝を形成する工程と、露出した第1の半導体ピラー上にエピタキシャル層を成長させて第2の半導体ピラーを形成する工程と、を有することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】高い耐電圧特性、および耐リーク特性を有する配線構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体素子が設けられた基板と、前記基板上に形成された第1および第2の配線と、前記第1の配線の下面の前記第2の配線側に接続されたビアと、前記ビアを含むビア層絶縁膜と、を有する半導体装置を提供する。前記ビアは、前記第1の配線と前記第2の配線の間の領域である配線間領域下の上端に凹部を有する。前記ビア層絶縁膜は、前記第1および第2の配線の幅方向に前記ビアと隣接する領域を含む溝を前記配線間領域の下に有する。前記配線間領域および前記溝内にはエアギャップが含まれる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に形成された研磨後のキャップ絶縁膜の厚さを容易に推定できる半導体装置の製造方法を提供する。

【解決手段】半導体装置形成領域に第1の導電膜よりなるゲート電極15、半導体装置非形成領域に絶縁膜形成部16、及び絶縁膜よりなり、ゲート電極の上面及び絶縁膜形成部の上面を覆うキャップ絶縁膜17を形成し、次いで、キャップ絶縁膜を覆う層間絶縁膜28を形成し、次いで、キャップ絶縁膜上に形成された層間絶縁膜にゲート電極の延在方向と交差する方向に延在する溝47を形成すると共に、溝の下方に位置する層間絶縁膜に不純物拡散層を露出するコンタクトホール22,23を形成し、次いで、溝及びコンタクトホールを埋め込む第2の導電膜51を形成し、次いで、CMP法により第2の導電膜を研磨することでコンタクトプラグを形成し、その後、絶縁膜形成部に形成されたキャップ絶縁膜の厚さを測定する。

(もっと読む)

半導体装置及びその製造方法

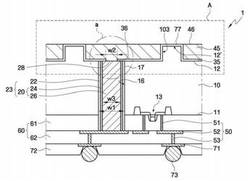

【課題】本発明ではフォトリソグラフィー技術解像限界付近のパターン形成を安定して形成すると共に、コンタクトプラグなどの構造物における目合わせずれや接触面積の縮小による接触電気抵抗の増大や接続不良を解決する。

【解決手段】半導体基板上に形成された絶縁材料層100に、第1の方向に延在し、底部の幅W1より上部の幅W2が広い第1の溝101を形成する工程と、第1の溝101内に、溝の上端より低い位置まで埋め込み層102を形成する工程と、埋め込み層102上に露出している第1の溝101の側壁を覆うサイドウォール103を形成する工程と、サイドウォール103をマスクとして埋め込み層102をエッチングして第1の方向に分離する工程と、

を含むことを特徴とする。

(もっと読む)

固体撮像装置およびその製造方法

【課題】高速動作に有利な固体撮像装置およびその製造方法を提供する。

【解決手段】固体撮像装置は、多層配線層73と、前記多層配線層上に設けられ、貫通トレンチを有する半導体層64と、前記貫通トレンチ内部に埋め込まれた第1導電層69と、前記第1導電層の周囲に形成された第1絶縁膜32と、前記第1絶縁膜の周囲に形成された第1導電型の第1不純物拡散層36とを備える。

(もっと読む)

半導体装置の製造方法

【課題】ビット線材料埋設体の形状のばらつきに起因するビット線の配線抵抗値のばらつきを防ぐ半導体装置の製造方法を提供する。

【解決手段】製造方法は、第一溝4内に第一のビット線材料埋設体6および第二のビット線材料埋設体10からなるビット線11を形成する第一工程と、ビット線11に含まれる不純物を拡散させて第一不純物拡散領域13を形成する第二工程と、ピラー部1bを形成する第三工程と、ピラー部1bに対向する配線17を第二溝15内に形成する第四工程と、ピラー部1bの先端部に、第二不純物拡散領域19を形成する第五工程と、を具備し、第一工程が、第一溝4を完全に埋め込むように第一ビット線材料を形成した後に第一ビット線材料表面を平坦化し、第一溝4底部に残るように第一ビット線材料をエッチバックする工程を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のコンタクトプラグのゲート電極への短絡を防止する。第1の不純物拡散層と第1のコンタクトプラグの接続抵抗、及び第1と第2のコンタクトプラグの接続抵抗を低減することにより、縦型MOSトランジスタのオン電流を増加させる。

【解決手段】シリコンピラー上部に、非晶質シリコン層及び単結晶シリコン層を形成する。次に、2度の選択エピタキシャル成長法により、シリコンピラー上に順に非晶質シリコン層、及び非晶質シリコンゲルマニウム層を形成する。この後、熱処理により、シリコンピラー上部に単結晶シリコン層を有する第1の不純物拡散層を形成すると同時に、シリコンピラー上に単結晶シリコン層及び多結晶シリコンゲルマニウム層を有する第1のコンタクトプラグを形成する。次に、第1のコンタクトプラグに接続されるように、金属から構成される第2のコンタクトプラグを形成する。

(もっと読む)

61 - 80 / 516

[ Back to top ]