Fターム[5F033JJ04]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 半導体(基板を除く) (666) | 多結晶Si (516)

Fターム[5F033JJ04]に分類される特許

501 - 516 / 516

半導体装置の配線構造体及びその形成方法

【課題】 半導体装置の配線構造体およびその形成方法を提供する。

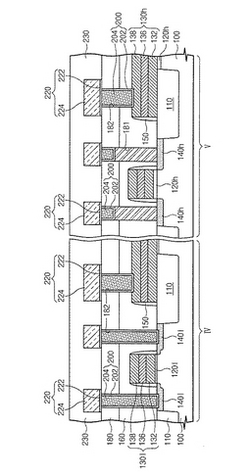

【解決手段】 この半導体装置は半導体基板100上に配置された層間絶縁膜、前記層間絶縁膜を貫通する第1コンタクト構造体181および第2コンタクト構造体182、前記層間絶縁膜上に配置されて前記第1コンタクト構造体と前記第2コンタクト構造体に連結される金属配線220を具備する。この際、前記第1コンタクト構造体は順次に積層された第1プラグおよび第2プラグ200を含み、前記第2コンタクト構造体は前記第2プラグを含む。

(もっと読む)

半導体装置の製造方法

【課題】 少ない工程でアライメントマークとして利用できる段差を形成することが出来る、半導体装置の製造方法を提供する。

【解決手段】 基板の表面又は基板上に形成した第1の膜の表面に、複数の凹部を形成する第1の工程と、凹部の内部に選択的に第2の膜を形成する第2の工程と、少なくとも1つの凹部及びその近傍を含む第1の領域に局所的エッチングを行って、第1の領域内の第2の膜の表面とその近傍との間に段差を形成する第3の工程とを備える。段差が形成された位置をアライメントマークとして利用する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の小型化を可能にする。

【解決手段】 基板21上のエピタキシャル層22に、ゲート電極32と、n-型オフセットドレイン領域35、n型オフセットドレイン領域39およびn+型ドレイン領域42からなるドレイン領域と、n-型ソース領域36およびn+型ソース領域43からなるソース領域とを有するLDMOSFEを形成するとともに、n型ウエル27上に複数のショットキ電極52を形成してショットキ電極52およびn型ウエル27間にショットキ接合を形成することでショットキダイオード素子を形成している。複数のショットキ電極52はプラグ63およびアノード電極74を介して互いに電気的に接続されている。複数のショットキ接合部の間および両側に設けられたn+型半導体領域44は、プラグ63およびカソード電極73を介して互いに電気的に接続されている。

(もっと読む)

シリコンゲルマニウム犠牲層を用いた半導体素子の微細パターンの形成方法及びそのパターンの形成方法を用いた自己整列コンタクトの形成方法

【課題】 シリコンゲルマニウム犠牲層を使用して半導体素子の微細パターンを形成する方法、及びそれを用いた自己整列コンタクトを形成する方法を提供する。

【解決手段】 基板上に導電性物質膜、ハードマスク膜及び側壁スペーサを含む導電ライン構造物を形成し、基板の全面に少なくとも導電ライン構造物の高さと同じであるか、またはそれ以上の高さにシリコンゲルマニウム(Si1−XGeX)犠牲層を形成し、犠牲層上にコンタクトホールを限定するフォトレジストパターンを形成した後、犠牲層を乾式エッチングすることで基板を露出させるコンタクトホールを形成し、ポリシリコンを使用してコンタクトホールを埋め込む複数のコンタクトを形成した後に残留する犠牲層を湿式エッチングした後、その領域にシリコン酸化物を満たして第1層間絶縁層を形成する半導体素子の自己整列コンタクトの形成方法。

(もっと読む)

半導体装置

【課題】 バイポーラトランジスタにおける高利得化および低雑音化を同時に実現できる技術を提供する。

【解決手段】 ベースパッド31およびコレクタパッド32の下部にエミッタ(基準(接地)電位)と電気的に接続された配線24が設けられた基板シールド構造とすることにより、ベースパッド31およびコレクタパッド32と配線24との間では容量が設けられた構造として電力消費をなくし、基板1からの熱雑音は、配線24を介して基準(接地)電位へと逃がし、ベースパッド31およびコレクタパッド32へは届かないようにする。

(もっと読む)

複数の半導体層を備えた半導体デバイス

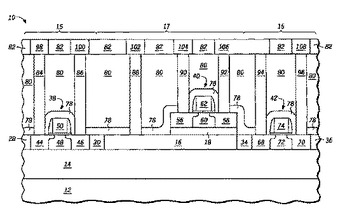

半導体デバイス構造(10)では、N及びPチャネルトランジスタキャリア移動度を別々に最適化するため、二つの半導体層(16、20)が使用される。これを決定する導電特性は、半導体の材料の種類、結晶面、配向性及び歪みの組み合わせである。シリコンゲルマニウムの半導体材料、圧縮性歪み、(100)の結晶面及び<100>の配向性を特徴とする導電特性の場合、Pチャネルトランジスタ(38)においてホール移動度が向上する。また、結晶面は(111)であってもよく、この場合、配向性は重要ではない。N型伝導に適した基板は、P型伝導に適した(又は最適)基板とは異なる。Nチャネルトランジスタ(40)は、好ましくは、引っ張り歪み、シリコン半導体材料及び(100)面を有する。別の半導体層(16、20)では、N及びPチャネルトランジスタ(38、40)はいずれもキャリア移動度に対し最適化される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 セルトランジスタの拡散層に接続された多結晶シリコン電極と、周辺回路トランジスタの拡散層に接続された金属電極とを備え、多結晶シリコン電極が形成された拡散層の接合リーク電流が抑制され、これによって、良好な情報保持特性を有する半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、多結晶シリコン電極に接続された拡散層を有するトランジスタを形成する工程と、980〜1020℃の基板温度で熱処理する第1の高温熱処理工程(工程A2)と、700〜850℃の基板温度で熱処理する第1の低温熱処理工程(工程A3)とをこの順に有する。

(もっと読む)

半導体デバイスにおけるレベル内またはレベル間誘電体としての超低誘電率材料を製造するための改良した方法およびこれによって作成される電子デバイス

【課題】 誘電率が低く、熱安定性を有する誘電材料を提供する。

【解決手段】 プラズマ化学気相成長(PECVD)プロセスを利用して、平行板化学気相成長プロセスにおいて、Si、C、O、およびH原子を含む熱的に安定した超低誘電率膜を製造するための方法を開示する。更に、この方法によって作成された熱的に安定した超低誘電率材料の絶縁層を含む電子デバイスを開示する。熱的に安定した超低誘電率膜の製造を可能とするため、例えばジエトキシメチルシラン(DEMS)のようなシラン誘導体、および、例えばビシクロヘプタジエンおよび酸化シクロペンテンのような有機分子等、特定の前駆物質材料を用いる。

(もっと読む)

パッド下に素子を備える手法によるウェハの有効利用

半導体構造(20)のパッドエリア(21)下に能動素子(25)を組み込むことにより、シリコンエリアのより効率的な利用を可能とする。パッドエリア(21)は、上方に第1の金属層(23)を備えた基板(22)を含む。第2の金属層(26)は第1の金属層(23)の下とする。能動素子(25)は基板内であって、第2の金属層(26)の下に備えられる。誘導体層(24)は第1の金属層(26)と第2の金属層(23)とを分離する。誘導体層(24)内のビア(27)は第1の金属層(23)と第2の金属層(26)とを電気的に接続する。ビア(27)は能動素子(25)と接続する。隣接金属層(424、425、426)を第1の金属層(23)と第2の金属層(26)の間に配置してもよい。  (もっと読む)

(もっと読む)

減少されたコンタクト高さでのバイポーラ及びCMOSの集積回路構造体

【課題】 複数の高さのデバイスを含む集積回路構造体であって、このようなデバイスに形成されたコンタクトの高さを減少させるために保護層の高さを減少させた、改善された構造体を提供すること。

【解決手段】 単一の基板上に配置された複数の相補型金属酸化膜半導体(CMOS)トランジスタ及び複数の垂直バイポーラ・トランジスタを含む集積回路構造体のための方法及び構造体が開示される。垂直バイポーラ・トランジスタは、CMOSトランジスタより高さのあるデバイスである。この構造体においては、保護層が、基板の上に、及び、垂直バイポーラ・トランジスタとCMOSトランジスタとの間に配置される。配線層は保護層の上にある。垂直バイポーラ・トランジスタは、配線層と直接接触しており、CMOSトランジスタは保護層を通って延びるコンタクトによって配線層に接続されている。

(もっと読む)

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

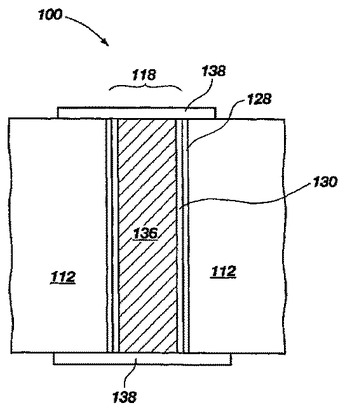

半導体構成部品に導電性ビアを形成するための方法が開示される。この方法は、第1の表面及び反対側の第2の表面を有する基板112を設けるステップを含む。この基板に、第1の表面と反対側の第2の表面の間に延びる少なくとも1つの穴118が形成される。基板のこの少なくとも1つの穴を画定している側壁にシード層128が形成され、導電層130でコーティングされ、この少なくとも1つの穴の内部の残りの空間に、導電性材料又は非導電性充てん材料136が導入される。基板を貫通した導電性ビアを、ブラインド・ホールを使用して形成する方法も開示される。本発明の導電性ビアを含む基板を有する半導体構成部品及び電子システムも開示される。  (もっと読む)

(もっと読む)

電子デバイス、アセンブリ、電子デバイスの製造方法

半導体基板は、共通の誘電層を有する垂直相互接続部および垂直キャパシタの両方を備えている。基板は、アセンブリを形成するために更なるデバイスと適切に組み合わせることができる。基板は、一方の面を第1のステップを含むエッチング処理で形成した後、基板の他方の面を第2のステップを含む処理で形成することができる。  (もっと読む)

(もっと読む)

化学機械研磨プレーナ化のためのデュアルシリコンゲート層を有するFINFET

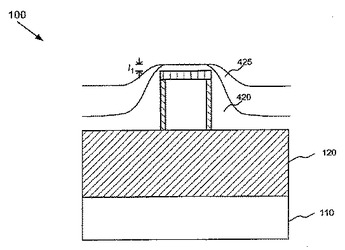

FinFETタイプの半導体デバイスは、フィン構造(210)を含んでいる。この上には、比較的薄いアモルファスシリコン層(420)を形成し、それから非ドープポリシリコン層(425)を形成する。この半導体デバイスは、アモルファスシリコン層(420)がフィン構造の損傷を防ぐ停止層として働く化学機械研磨(CMP)を使用してプレーナ化することができる。  (もっと読む)

(もっと読む)

配線構造

【課題】 銅を配線材として用いても、微細な配線構造の形成が可能で、製造の工程数が少なく、低コスト化が可能な配線構造を提供する。

【解決手段】 半導体素子が形成された基板上に絶縁膜103が多層形成され、絶縁膜103に形成された配線溝およびビアホールに金属配線剤が充填されて、配線および接続プラグが形成された配線構造において、絶縁膜103のうち少なくとも一層が対電子線感光性を有する材料から形成されており、絶縁膜103の層間にはバリア絶縁膜104を有し、前記金属配線剤は銅を含むものである。

(もっと読む)

配線構造の製造方法

【課題】 銅を配線材として用いても、微細な配線構造の形成が可能で、製造の工程数が少なく、低コスト化が可能な配線構造の製造方法を提供する。

【解決手段】 配線構造の製造方法が、半導体素子201の上にWプラグ203(下層配線)が形成された基板上に、対電子線感光性を有する材料を含む第二層間絶縁膜204(絶縁膜)を形成する工程と、第二層間絶縁膜204に電子線を照射して、第二層間絶縁膜204を露光する工程と、第二層間絶縁膜204を現像して未露光部を除去し、配線溝および/またはビアホールおよび/またはコンタクトホールを形成する工程とを有する。

(もっと読む)

フリップチップ用高性能シリコンコンタクト

本発明においては、前面(14)と背面(16)とを備える半導体基板(12)であって、基板を(12)通って前面(14)と背面(16)との間を延びる孔(18、20、22)を備える半導体基板(12)を用意する。孔(18、20、22)は、部分的に、内壁部分によって規定され、外側導電性シースを形成する。導電性材料(54)を、内壁部分の少なくとも一部に隣接して形成する。その後に誘電体材料層(56)を、孔内部に、導電性材料上であってそのラジアル方向内側に形成する。次に第2の導電性材料(60)を、孔内部に、誘電体材料層(56)上であってそのラジアル方向内側に形成する。後者の導電性材料は、内側導電性コアキシャル線要素を構成する。 (もっと読む)

501 - 516 / 516

[ Back to top ]