Fターム[5F033JJ15]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Co、Co合金 (211)

Fターム[5F033JJ15]に分類される特許

121 - 140 / 211

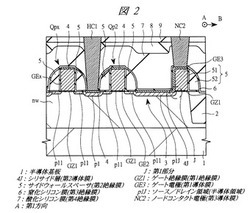

半導体装置およびその製造方法

【課題】複数の異なる配線箇所に単一のコンタクト電極を形成した構造を有する半導体装置において、製造歩留まりを向上させる。

【解決手段】半導体基板1の主面の第1方向Aに延在し、その主面上にゲート絶縁膜GZ1を介して形成され、側壁にサイドウォールスペーサ5を備えたゲート電極GE3と、その側方下部である第1部分Jに達するソース/ドレイン領域p1Jと、半導体基板1の主面を覆うようにして順に形成された、エッチング速度の異なる窒化シリコン膜6および酸化シリコン膜7を有する半導体装置であって、第1部分Jにおいて、ゲート電極GE3はサイドウォールスペーサ5に覆われておらず、ゲート電極GE3の上面、側面およびソース/ドレイン領域p1Jは、シリサイド層4Jによって覆われることで電気的に接続され、シリサイド層4Jにはノードコンタクト電極NC2が電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】バリアメタルが薄い場合でもAl配線のモフォロジ及びエレクトロマイグレーションを改善することができる半導体装置の製造方法を得る。

【解決手段】まず、半導体基板11上にSiO2層間膜13(酸化膜)を形成する。次に、SiO2層間膜13上にTi膜18を形成する。次に、Ti膜18上にTiN膜32を形成する。次に、TiN膜32上にAl配線33を形成する。ここで、Ti膜18を形成する工程において、圧力が0.3Pa以下の雰囲気中で物理気相成長法を用いる。これにより、Ti膜18とSiO2層間膜13との間にTiO2膜31が形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板に貫通配線層を形成する際の貫通孔底部での配線層の薄膜化が防止され、貫通接続部の接続不良が改善された半導体装置を提供する。

【解決手段】貫通孔3を有する半導体基板2の表面に、該貫通孔3と同径の開口4aを有する第1の絶縁層4が被覆され、その上に第1の配線層5が形成されている。また第1の配線層5の近傍に、貫通孔3とその内壁面等に形成された第3の絶縁層8および貫通孔3内に充填・形成された第3の配線層9から成る貫通接続部が形成されている。そして、この貫通接続部に内接された第2の配線層7と第1の配線層5とが電気的に接続され、貫通孔3の内壁面と第1の配線層5との間に第2の絶縁層6が介在し、第1の配線層5と貫通孔3内に充填・形成された第3の配線層9とが離間されるように構成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】抵抗素子による半導体装置の厚みの増加や立体構造による導通不良、および抵抗素子と電極との間の界面によって生じる導通性の低下などに囚われない、接続信頼性の高い抵抗素子を備えた半導体装置を提供する。

【解決手段】第一電極1を一面に備える半導体基板2、半導体基板2の一面にあり、第一電極1と整合して第一開口部を設けた第一絶縁層3、第一絶縁層3に積層し、第一開口部と連通する第二開口部を配した第二絶縁層4、前記第一開口部と、前記第二開口部と、第二絶縁層4とを覆うように配したシード層5、および第一電極1と電気的に接続し、前記第二開口部を覆うようにシード層5上に配した第二電極6、を少なくとも備える半導体装置であって、シード層5は多層をなし、少なくとも第二電極6に接したシード層5上部は第二電極6と同じパターンであり、シード層5下部は抵抗素子として機能することを特徴とする半導体装置を提供する。

(もっと読む)

層間導電性コンタクトを含む半導体素子及びその形成方法

【課題】半導体素子及びその形成方法を提供する。

【解決手段】半導体素子は、半導体素子の下部コンタクト領域(underlying contact region)上に配置され、上部面を有する第1層間絶縁膜と、前記第1層間絶縁膜を貫通する第1開口部110a、110b内に配置され、第1幅W1aの上部を有する第1導電パターン113a、113bと、第1導電パターン113a、113bの上部面と接触され、第1幅W1aより狭い第2幅W2aの下部を有する第2導電パターン125a、125bと、を含み、第1導電パターン113a、113bの上部面は、前記第1層間絶縁膜の上部面に対して相対的にリセスされて、第1導電パターン113a、113bの上部面の前記下部コンタクト領域に相対的な高さは、前記第1層間絶縁膜の上部面の前記下部コンタクト領域に相対的な高さより低い。第2導電パターン125a、125bが第1導電パターン113a、113bの上部面と接続される。第2導電パターンの下部は、第1幅より狭い第2幅を有する。

(もっと読む)

半導体装置

【課題】従来と異なる方法によりチャネル領域に歪みを発生させたMISFET構造を有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成された第1のソース・ドレイン領域および第1のチャネル領域を有するn型MISFETと、前記半導体基板上に形成された第2のソース・ドレイン領域および第2のチャネル領域を有するp型MISFETと、前記第1のソース・ドレイン領域に接続され、前記第1のチャネル領域に伸張歪みを与える第1のコンタクトプラグと、前記第2のソース・ドレイン領域に接続され、前記第2のチャネル領域に圧縮歪みを与える第2のコンタクトプラグと、を有する。

(もっと読む)

凹部充填方法

【課題】凹部を隙間無く充填する。

【解決手段】本発明は基板11の表面の凹部12が形成された面に、金属膜15を形成する成膜工程と、金属膜にエッチングガスのイオンを入射させるエッチング工程とを交互に繰り返す。成膜工程で凹部12に突き出すように形成されるオーバーハング部19はエッチング工程で除去されるので、次の成膜工程の時に凹部12の開口は塞がれておらず、凹部12内部の金属膜15を成長させることができる。

(もっと読む)

電子デバイス及びその製造方法

【課題】接続ブロックを用いたCNTによる横配線を有する電子デバイスであって、接続ブロックとカーボンナノチューブの接続を良好にすること。

【解決手段】側面に第1の面を有する導電性の第1の接続ブロック13aと、第1の面に対向する第2の面を有する第2の接続ブロックと、第1の面上に形成される触媒金属微粒子17a、触媒薄膜のいずれかを有する触媒領域17と、第2の接続ブロックの第2の面上に形成される炭素吸収金属18a、18bを有する炭素元素円筒型構造体吸収領域兼成長阻止領域18と、触媒領域17から炭素元素円筒型構造体吸収領域兼成長阻止領域18に伸びて第1の接続ブロック13aと第2の接続ブロック13bを電気的に接続する炭素元素円筒型構造体19bとを有する。

(もっと読む)

配線、電子装置及び電子装置の製造方法

【課題】性能劣化を抑制することが可能な高信頼性の配線を提供する。

【解決手段】第1導電膜に一端を接続し、第1導電膜と離間した第2導電膜に他端を接続する束状のカーボンナノチューブからなる複数の導電部材20と、導電部材20の間に分散されたダイヤモンド結晶構造を有する炭素粒子22とを備える。

(もっと読む)

電子デバイス及びその製造方法

【課題】カーボンナノチューブを用いた配線構造を備える電子デバイスの製造方法について、炭素元素円筒型構造体からなるビアを歩留まり良く形成すること。

【解決手段】基板1上の第1絶縁膜2上に導電パターン5を形成する工程と、第1絶縁膜2と導電パターン5を覆う第2絶縁膜7を形成する工程と、第2絶縁膜7のうち導電パターン5の上にホール7aを形成する工程と、少なくともホール7a内の底面と第2絶縁膜7の上面に金属膜9を形成する工程と、金属膜9の表面に触媒粒子又は触媒膜からなる触媒面10を形成する工程と、触媒面10から炭素元素円筒型構造体11の束を成長する工程と、炭素元素円筒型構造体の束10の間隙に埋込膜12を形成する工程と、炭素元素円筒型構造体の束11及び埋込膜12及び金属膜9を研磨して第2絶縁膜7の上面から除去するとともに、埋込膜12及び炭素元素円筒型構造体の束11をホール7a内に残してビア13を形成する工程とを含む。

(もっと読む)

配線、電子装置及び電子装置の製造方法

【課題】抵抗を低減することが可能な配線を提供する。

【解決手段】第1導電膜12と第1導電膜12の上層の第2導電膜26とを電気的に接続する配線24であって、第1導電膜12の上の複数の第1金属粒子16と、複数の第1金属粒子16のそれぞれを介して第1導電膜12の表面に一端を接続する複数の導電部材18と、複数の導電部材18のそれぞれの他端側の側面上の複数の第2金属粒子20と、複数の第2金属粒子20のそれぞれを介して複数の導電部材18のそれぞれの表面に一端を接続し、第2導電膜26にそれぞれ接続する複数の導電部材22とを備える。

(もっと読む)

半導体装置、およびその製造方法

【課題】配線間絶縁膜からビア間絶縁膜への水分の移動を抑制し、配線間の実効誘電率に与える影響の少ない絶縁膜を有する半導体装置、およびその製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置1は、表面に半導体素子を有する半導体基板と、前記半導体基板上に形成された配線2bと、前記配線2bと同じ層に形成された配線間絶縁膜4bと、前記配線2bの下面に接続された第1のビア7aと、前記第1のビア7aと同じ層に形成された第1のビア間絶縁膜8aと、前記配線2bの上面に接続された第2のビア7bと、前記第2のビア7bと同じ層に形成された第2のビア間絶縁膜8bと、前記配線間絶縁膜4bと前記第1のビア間絶縁膜8aとの間、および前記配線間絶縁膜4bと前記第2のビア間絶縁膜8bとの間の少なくともいずれか一方に形成されたCuSiN膜9と、を有する。

(もっと読む)

半導体装置の製造方法および記録媒体

【課題】半導体装置を構成する金属に残留するフッ素を低減して、信頼性の高い半導体装置を提供する。

【解決手段】被処理基板に形成される半導体装置の電極あるいは配線を形成している金属に生成した金属フッ化物を除去する処理を行うフッ化物除去工程を有する半導体装置の製造方法であって、前記フッ化物除去工程では、前記被処理基板に気体状態の蟻酸を供給し、前記金属フッ化物を除去することを特徴とする半導体装置の製造方法。

(もっと読む)

集積回路の修正配線形成方法

【課題】 カーボンナノチューブ配線を用いた集積回路の修正配線形成方法を提供する。

【解決手段】 電子ビーム化学気相成長法で配線修正が必要なところに成長の触媒となる金属を含む微粒子10を堆積し、炭化水素系ガスやエタノールを原料とした化学気相成長法でカーボンナノチューブ配線11を成長させる。配線修正が必要なところへの触媒金属の供給は走査マイクロピペットプローブ顕微鏡による電気化学反応による析出または集束イオンビーム化学気相成長法でも行うことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性が高くかつ初期のビア抵抗値のばらつきが小さい半導体装置およびその製造方法を提供する。

【解決手段】本発明にかかる半導体装置は、第1の絶縁層10内に形成されている第1の配線12と、第1の絶縁層10および第1の配線12上に形成されている第2の絶縁層20内に形成されている第2の配線12とを有する半導体装置である。ここで、第1の配線12および第2の配線22の少なくともいずれかはCuAl配線である。また、第2の配線22は、そのビアプラグ部22vで、複数のバリア層24を介在して、第1の配線12に電気的に接続している。また、バリア層において、CuAl配線と接触するCuAl接触バリア層は、窒素原子含有量が10原子%未満である。

(もっと読む)

半導体装置およびその製造方法

【課題】多層配線構造の作製において、すべての多層配線用ビア・配線・電極および放熱用ビアなどを、相互の接続特性を良好に保って、カーボンナノチューブ(CNT)束により形成する半導体装置を提供する。

【解決手段】電導素材である、柱状構造をもったカーボンナノチューブ(CNT)束2の少なくとも一つの表面に、Au膜など金属膜を形成後、下地層を積層し、その上に触媒金属層を形成して、CVD法により柱状構造をもったカーボンナノチューブ(CNT)束7を成長することで、二つの柱状構造体カーボンナノチューブ(CNT)束を低抵抗で接続して形成する。この基本構成方法の組合せで、多層配線用の各種電導構成要素を作製する。また、成長条件によりCNTの成長先端部が平坦となることを用いて、Au膜など金属膜を利用せずに、成長方向に多段に、長いカーボンナノチューブ(CNT)束を作製でき、特に放熱用ビアなどへの適用が可能である。

(もっと読む)

半導体装置の製造方法

【課題】抵抗が小さく信頼性の高いCu配線またはCuプラグを備えた半導体装置を提供することにある。

【解決手段】基板上に形成された層間絶縁膜4に溝部10を形成した後、溝部10の内壁を含む層間絶縁膜3上にバリアシード膜6を形成し、バリアシード膜6を電極として、電解メッキ法により溝部10内に銅7を埋め込む。バリアシード膜6は、絶縁体または半導体の特性を有する高融点金属の酸化物または窒化物からなる単層の膜であって、該膜に銅以外の低抵抗金属が含有されている。

(もっと読む)

メモリデバイス、特に、トランジスタを備えた相変化ランダムアクセスメモリデバイス、およびメモリデバイスを形成する方法

【課題】メモリセルの寸法を微細化し、メモリセルでの動作を改善するための、トランジスタを備えた相変化ランダムアクセスメモリデバイス、およびメモリデバイスを形成する方法を提供する。

【解決手段】抵抗スイッチングメモリデバイスは、非導電性材料からなるナノワイヤ1010が、導電性材料からなるナノチューブ1110を形成するためのモールドとして機能するように形成される。ナノチューブ1110の輪状面が、相変化を起こす切り替え活性材料1320に結合され、これによって下部電極コンタクトが形成されるように、切り替え活性材料のバルク1320がナノチューブ1110の最上部に堆積される。ストライプ1410は、切り替え活性材料のバルク1320との上部電極コンタクトになり、ビット線1460がビット線コンタクト1450に接続される。

(もっと読む)

不均一窒化金属膜を用いる電気的接続構造物の形成方法およびこの方法によって製造された接続構造物

【課題】集積回路素子の電気的接続構造物の形成方法を提供する。

【解決手段】半導体基板100上に第1絶縁層200を形成し、第1絶縁層に開口を形成する。開口の側壁を不均一の窒素濃度を有する窒化第1金属層312でライニングする。開口の内部に導電パターン410が形成される。導電パターンと窒化第1金属層との間に第2金属窒化膜320が形成される。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】Al膜の埋め込み性を向上させた半導体装置の製造方法、及び半導体装置の製造装置に関するものである。

【解決手段】制御部が、ビアホールVHを有したシリコン基板の表面に金属膜BM1(Ti膜)と金属窒化膜BM2(TiN膜)を被覆させ、金属窒化膜BM2に被覆されたビアホールVHの内部にCVD法を用いてAl−CVD膜P1を形成させた。そして、制御部が、成膜条件データに対応する成膜条件の下で金属窒化膜BM2を被覆させ、ビアホールVHの底部に位置する金属窒化膜BM2の膜厚を基準膜厚よりも薄く形成し、かつ、ビアホールVHの上部に位置する金属窒化膜BM2の膜厚を基準膜厚よりも厚く形成させた。

(もっと読む)

121 - 140 / 211

[ Back to top ]