Fターム[5F033JJ15]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Co、Co合金 (211)

Fターム[5F033JJ15]に分類される特許

141 - 160 / 211

半導体装置の製造方法及び半導体装置の製造装置

【課題】Al膜の埋め込み性を向上させた半導体装置の製造方法、及び半導体装置の製造装置に関するものである。

【解決手段】制御部が、ビアホールVHを有したシリコン基板の表面に金属膜BM1(Ti膜)と金属窒化膜BM2(TiN膜)を被覆させ、金属窒化膜BM2に被覆されたビアホールVHの内部にCVD法を用いてAl−CVD膜P1を形成させた。そして、制御部が、成膜条件データに対応する成膜条件の下で金属窒化膜BM2を被覆させ、ビアホールVHの底部に位置する金属窒化膜BM2の膜厚を基準膜厚よりも薄く形成し、かつ、ビアホールVHの上部に位置する金属窒化膜BM2の膜厚を基準膜厚よりも厚く形成させた。

(もっと読む)

表示装置の作製方法、及びエッチング装置

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。

【解決手段】チューブを絶縁層の開口形成領域上に絶縁層に接して配置し、そのチューブを通して処理剤(エッチングガス又はエッチング液)を絶縁層に吐出する。吐出(された処理剤(エッチングガス又はエッチング液)によって、絶縁層を選択的に除去し、絶縁層に開口を形成する。従って、導電層上に開口を有する絶縁層が形成され、絶縁層下の導電層が開口の底面に露出する。露出された導電層と接するように開口に導電膜を形成し、導電層と導電膜を絶縁層に設けられた開口において電気的に接続する。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。

【解決手段】導電層上にマスクを設け、マスクを設けた導電層上に絶縁膜を成膜し、マスクを除去することで開口を有する絶縁層を形成する。露出した導電層と接するように開口に導電膜を形成することによって、導電層及び導電膜は絶縁層を介して電気的に接続することができる。開口の形状はマスク形状を反映し、柱状(角柱、円柱、三角柱など)、針状などを用いることができる。

(もっと読む)

半導体装置

【課題】 銅と銅以外の異種材料を使用した配線とプラグ等の配線導電体間において、銅の拡散を効果的に防止することにより、信頼性を向上した半導体装置を提供することを目的とする。

【解決手段】 半導体基板上の第一の層間絶縁層100内に形成されたタングステンプラグ101aと、タングステンプラグ101a上に形成された導電性かつ薄膜のコバルト含有キャップ膜103と、第一の層間絶縁層100の上層層間絶縁層である第二の層間絶縁層104内において、タングステンプラグ101a上にキャップ膜103を介して形成された銅配線105aを備える。

(もっと読む)

相互接続構造内におけるカーボンナノ構造成長の制御

基板上の相互接続構造が提供される。この相互接続構造は、基板レベルの上又は上方の少なくとも2つの相互接続レベルに導電性の相互接続素子を具える。本発明の相互接続構造では、少なくとも1つの導電性のビアが一つの相互接続レベルにおける第1の相互接続素子を異なる相互接続レベルにおける第2の相互接続素子に接続する。このビアは、第1の誘電体層のビア開口内を延びる導電性の円筒状カーボンナノ構造を含む導電性ビア材料を具える。少なくとも1つのカバー層部分がビア開口の横方向広がり内まで延在してビアアパーチャを規定し、このアパーチャはカーボンナノ構造がこのビアアパーチャを貫通するのを阻止するに十分なほど小さい。この構造によれば相互接続構造の製造中における高さ方向のカーボンナノ構造成長の制御が向上する。  (もっと読む)

(もっと読む)

コンタクトエリアに金属シリサイド領域が局所的に設けられたトランジスタ及び該トランジスタを形成するための方法

誘電材料層などのパターニングされた誘電層に基づいてシリサイデーションプロセスを実行することによって、各々の金属シリサイド部位を各々のコンタクト領域に非常に局所的なやり方で供給することができ、一方で、全体の金属シリサイド量を著しく減らすことができる。このようにして、金属シリサイドが電界効果トランジスタのチャネル領域に及ぼす悪影響を著しく減らすことができ、なおかつコンタクト抵抗を小さく維持することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】配線溝および接続孔の内部に、良好な埋め込み形状を有するCu膜を電解めっきにより形成する。

【解決手段】半導体装置の製造方法であって、半導体基板上に絶縁膜11を形成する工程と、絶縁膜11に配線溝および接続孔の少なくとも一方の被埋め込み領域12を形成する工程と、被埋め込み領域12上に、導電性を有し、かつ被埋め込み領域12の内部を埋め込まない厚さの非晶質膜15を形成する工程と、非晶質膜15上に被埋め込み領域12の内部を埋め込む厚さの導電膜16をめっきにより形成する工程と、を有する。

(もっと読む)

半導体素子及びその製造方法

【課題】本発明は、半導体素子の層間接続のための金属の拡散を効率よく防止できる半導体素子及びその製造方法を提供する。

【解決手段】本発明は、半導体基板1;前記半導体基板1上にダマシンパターンが形成された層間絶縁膜2、3;前記ダマシンパターン内に形成され、三元系物質であるCoFeBからなる拡散防止膜4;前記拡散防止膜上に形成されるシード膜5;及び、前記シード膜上に充填される銅配線7を含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造過程において、コンタクトホールの底面に残る不要残存膜の厚さまたは抵抗値を高速、かつ高精度に推定する。

【解決手段】検査用標準試料1のコンタクトホール7を被検査対象のコンタクトホールとほぼ同じ材質および構造により構成し、電子線を照射して検査用標準試料1の二次電子画像の電位コントラストを測定し、検査用標準試料1の擬似欠陥部4におけるコンタクトホール7の電位コントラストとコンタクトホール7の底面に形成した擬似残存膜8の厚さまたは抵抗値との関係をあらかじめ取得しておく。その後、被検査対象のコンタクトホールへ電子線を照射して被検査対象の二次電子画像の電位コントラストを測定し、検査用標準試料1の電位コントラストと被検査対象の電位コントラストとを比較することにより、被検査対象のコンタクトホールの底面に残る不要残存膜の厚さまたは抵抗値を推定する。

(もっと読む)

半導体装置の製造方法

【課題】犠牲層残渣の発生や配線細りなどの不具合を抑制する、エアギャップ構造を有する半導体装置の製造方法を提供する。

【解決手段】基板1上に複数の配線を形成する半導体装置の製造方法であって、基板1上に、複数の配線と、複数の配線に対して選択してエッチングできる金属からなり、複数の配線の間隙に埋め込まれている犠牲層とを形成する工程と、犠牲層を複数の配線に対して選択比を有するエッチングにより除去して、複数の配線の間隙にエアギャップ構造を形成する工程とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】例えば全体の製造コストを低減できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置200は、半導体基板110と、ポリシリコン層30と、サイドスペーサ40と、第1シリサイド層262と、第2シリサイド層263と、金属膜261とを備える。半導体基板110は、拡散層14を有する。ポリシリコン層30は、半導体基板110の上において、拡散層14の付近に形成されている。サイドスペーサ40は、半導体基板110の上において、拡散層14とポリシリコン層30との間に形成されている。第1シリサイド層262は、拡散層14の上に自己整合的に形成されている。第2シリサイド層263は、ポリシリコン層30の上に自己整合的に形成されている。金属膜261は、第1シリサイド層262と第2シリサイド層263とを接続するように連続して延びている。

(もっと読む)

位置合せおよびフィーチャの成形に対してフレキシビリティが向上したナノインプリント技術

ビア開口部とトレンチとが共通に形成されるインプリント技術に基づいてメタライゼーションを形成することによって、従来のプロセス技術に求められたような少なくとも1つのさらなる位置合せプロセスを省略することができることから、プロセスの複雑性を実質的に軽減することができる。さらに、適切に設計されたインプリントモールドを提供することによりインプリントリソグラフィのフレキシビリティおよび実効性が向上し、これにより、信頼性、エレクトロマイグレーションに対する抵抗などの点から、最終的に得られるメタライゼーション構造のパフォーマンスもまた向上する。  (もっと読む)

(もっと読む)

半導体装置

【課題】増幅回路内の寄生抵抗を、補正抵抗を設置することで調整し、増幅回路を安定に動作させる。

【解決手段】カレントミラー回路において、カレントミラー回路内の寄生抵抗に対して、寄生抵抗を補正する補正抵抗が設置されている半導体装置であり、カレントミラー回路は、少なくとも2つの薄膜トランジスタを有するものである。薄膜トランジスタのそれぞれは、チャネル形成領域、ソース領域またはドレイン領域を有する島状半導体膜、ゲート絶縁膜、ゲート電極、ソース電極またはドレイン電極を有しており、補正抵抗は、ゲート電極、ソース電極、もしくはドレイン電極のいずれか1つの寄生抵抗を補正するものである。また補正抵抗はそれぞれ、ゲート電極、ソース電極またはドレイン電極、もしくはソース領域またはドレイン領域と同じ材料を含む導電層を有するものである。

(もっと読む)

固体及び気体誘電体の組み合わせによって離間された相互接続した導電性配線及びビアを含む多層相互接続構造を形成する方法、及び、空隙を含む複数レベルの相互接続構造(空隙を含む多層相互接続構造及びその製造方法)

【課題】本発明は、空隙を含む複数レベルの相互接続構造及びその製造方法を提供する。

【解決手段】空隙を含む複数レベルの相互接続構造は、散在したライン・レベル及びビア・レベルの集合を含み、ビア・レベルは、1つ以上の誘電体層に埋め込まれた導電性ビアを含み、ビア・レベルの誘電体層は、隣接レベルのライン機構の上下に位置する固体であり、ライン機構の間でミシン目が入れられている。ライン・レベルは導電性ラインと、空隙を含む誘電体とを含む。導電性接点を含み、有孔誘電体層内に充填することによって形成された固体誘電性ブリッジ層は、散在したライン及びビア・レベルの集合上に配置されている。

(もっと読む)

電気接続体、電気接続体の形成方法及びカートリッジ

【課題】基板に形成されたスルーホール内に金属超微粒子分散液を充填させて基板間の配線を行う場合に、数μmの微細なスルーホール径に対してスルーホールの高さ方向の長さが長くなってもスルーホール内に金属超微粒子分散液を充填することができ、よってスルーホール内の断線を防止することができる電気接続体、電気接続体の形成方法及びカートリッジを提供する。

【解決手段】液滴吐出装置10の直径約5μm以下、好ましくは約1μm以下のノズル12から基板22に向けて液滴24を噴射させ堆積する。液滴24を複数堆積して形成された液滴堆積体において、最初の液滴34a上の成長起源液滴層34bの固化した直径をRm1、着弾後の液滴を複数堆積して形成された液滴堆積体の最上層の液滴34dの最大直径をRm2としたときに、Rm1とRm2との比が2:1〜1:1となる。

(もっと読む)

半導体接合部に薄膜物質を選択的に堆積させる方法

本発明の実施形態は、基板上に形成されたデバイスに高品質コンタクトレベル接続部を形成するプロセスを提供する。一実施形態において、基板上に物質を堆積させるための方法であって、基板を酸化物エッチング緩衝液にさらして、前処理プロセスで水素化シリコン層を形成するステップと、基板上に金属シリサイド層を堆積させるステップと、金属シリサイド層上に第一金属層(例えば、タングステン)を堆積させるステップと、を含む前記方法が提供される。酸化物エッチング緩衝液は、フッ化水素とアルカノールアミン化合物、例えば、エタノールアミン、ジエタノールアミン、又はトリエタノールを含有することができる。金属シリサイド層は、コバルド、ニッケル、又はタングステンを含有することができ、無電解堆積プロセスによって堆積させることができる。一例において、基板は、溶媒と金属錯体化合物を含有する無電解堆積溶液にさらされる。 (もっと読む)

電着されたコンタクトを形成する構造体及び方法

【課題】 既存のCVDタングステン・プラグ金属化技術と比べて減少したプラグ抵抗を示し得る構造体を提供すること。

【解決手段】 基板上に配置されたキャビティを有するパターン形成された誘電体層と、キャビティの底部に配置された、コバルト及び/又はニッケルのようなシリサイド又はゲルニウム化物層と、誘電体層の上部及びキャビティの内部に配置され、前記底部においてシリサイド又はゲルニウム化物層に接触する、Ti又はTi/TiNを含むコンタクト層と、コンタクト層の上部及びキャビティの内部に配置された拡散バリア層と、バリア層の上部に配置された、めっきのための随意的なシード層と、ビア内の金属充填層とを含むコンタクト金属(メタラジ)構造体が、その製造方法と共に提供される。金属充填層は、銅、ロジウム、ルテニウム、イリジウム、モリブデン、金、銀、ニッケル、コバルト、カドミウム、亜鉛、及びこれらの合金から成る群から選択される少なくとも1つの部材を用いて電着される。金属充填層がロジウム、ルテニウム、又はイリジウムである場合、金属充填物と誘電体との間に有効な拡散バリア層を必要としない。バリア層が、ルテニウム、ロジウム、又はイリジウムのようにめっき可能である場合、シード層を必要としない。

(もっと読む)

障壁冗長構成要素を有する相互接続構造体および相互接続構造体を形成する方法

【課題】障壁冗長構成要素を有する相互接続構造体と、相互接続構造体を形成する方法とを提供する。

【解決手段】導電性ライン20の部分の上にバイア拡散障壁30が存在する。導電性ライン20の上で障壁30がない部分に存在する導電性材料54は、導電性ライン拡散障壁22とバイア拡散障壁30との間の電気的経路を提供する。従って、導電性材料54、導電性ライン拡散障壁22およびバイア拡散障壁30を用いて、内部障壁冗長構成要素が形成される。障壁冗長構成要素によって提供されるこの電気的経路によって、バイア底部のEM不良から生じる突然の回路開放を回避することができる。従って、監視デバイスによってEM不良が検出された後、チップ交換またはシステム操作調節のために十分な時間を提供する障壁冗長構成要素が相互接続構造体に提供される。

(もっと読む)

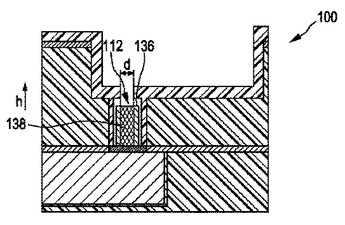

ミドル・オブ・ザ・ライン(MOL)用途のための無電解コバルト含有ライナ

【課題】 従来技術のMOLメタラジを用いてその欠点を回避する新しいMOLメタラジとその製造方法を提供すること。

【解決手段】 酸素ゲッター層と金属含有導電性材料との間に配置されたCo含有ライナを含む半導体構造が提供される。Co含有ライナ、酸素ゲッター層及び金属含有導電性材料は、Co含有ライナが従来のTiNライナと取って代わるMOLメタラジを形成する。「Co含有」とは、ライナが、元素状Coのみを含むか、又は元素状CoとP又はBの少なくとも1つを含むことを意味する。高アスペクト比のコンタクト開口部内により良好な段差被覆性の本発明のCo含有ライナを提供するために、Co含有ライナが、無電解蒸着プロセスによって形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に貫通孔を形成する際の、貫通孔の底部での絶縁層のノッチの発生を抑制し、絶縁層のノッチによる電気的絶縁性の低下や貫通孔の配線層の接続不良を低減することができる半導体装置およびその製造方法を提供する。

【解決手段】 この半導体装置1は、第一の面と第二の面を有する半導体基板2と、半導体基板2に設けられ、第一の面と前記第二の面とをつなぎ、半導体基板2の第一の面に対して、ほぼ垂直な側面を有する貫通孔5と、第一の面に設けられ、貫通孔5を覆うと共に貫通孔5の開口径よりも小さい開口径を有する第一の絶縁層3と、第一の絶縁層3上に設けられ、貫通孔5を覆う第一の配線層4と、貫通孔5の内壁部から半導体基板2の第二の面を覆うように設けられた第二の絶縁層6と、第一の絶縁層6の開口部を介し第一の配線層4と内接すると共に貫通孔5および半導体基板2の第二の面の第二の絶縁層6上に亘って設けられた第二の配線層7を備える。

(もっと読む)

141 - 160 / 211

[ Back to top ]