Fターム[5F033JJ15]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Co、Co合金 (211)

Fターム[5F033JJ15]に分類される特許

81 - 100 / 211

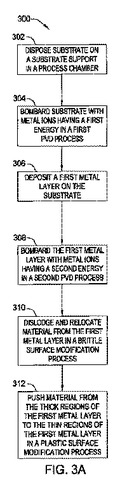

強化された銅のイオン化を伴うPVD銅シードオーバーハング再スパッタ

パターンが形成された基板上に金属を堆積させる方法および装置を提供する。金属層が,第1のエネルギーを有する物理蒸着工程で形成される。第2のエネルギーを用いて金属層上に第2の物理蒸着工程が行われ、ここで、堆積層は、脆性および塑性表面修正工程の相互作用を受け、基板上にほぼ同形の金属層が形成される。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

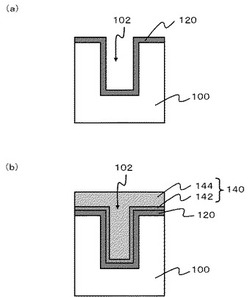

【課題】配線とバリア膜との密着性の低下、エレクトロマイグレーション耐性の低下、及び工程数の増加を抑制しつつ、めっき膜の膜厚がウェハ中心部とウェハ周辺部で異なることを抑制できる半導体装置の製造方法を提供する。

【解決手段】絶縁膜100に形成された溝102の側面及び底面に、添加元素を含む金属バリア膜120を形成する。次いで、金属バリア膜120上にシード膜142を形成し、さらにシード膜142をシードとしてめっき層(Cu膜144)を形成することにより、溝102内に金属膜140を埋め込む。次いで、金属バリア膜120及び金属膜140を熱処理することにより、金属バリア膜120と金属膜140の間に、金属バリア膜120を構成する金属、添加元素、及び金属膜140を構成する金属を含む合金層を形成し、かつ添加元素を金属膜140中に拡散させる工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板に形成される貫通孔底部での絶縁層のノッチの発生、貫通孔下の配線層へのダメージを抑制し、電気的絶縁性の低下や配線層の接続不良を低減できる半導体装置及びその製造方法を提供する。

【解決手段】第一の絶縁層203と、第一の絶縁層上の第一の配線層204と、半導体基板201を貫通し、底部に第一の絶縁層を厚さ方向に除去した部分的なエッチ部を備えた貫通孔201aと、貫通孔の部分的なエッチ部の底部を除く内壁部から半導体基板の第二の面までを覆う第二の絶縁層206と、貫通孔の底部に、第一の配線層が露出するように第一の絶縁層に形成された開口部203aと、該開口部で第一の配線層と接すると共に貫通孔の第二の絶縁層上から半導体基板の第二の面の第二の絶縁層上に亘る第二の配線層202とを有し、開口部に接する第一の絶縁層が、半導体基板に接する第一の絶縁層より小さい厚さを有する。

(もっと読む)

集積回路装置及びその製造方法

【課題】絶縁体上にもグラファイト層を容易に形成することができる集積回路装置及びその製造方法を提供する。

【解決手段】絶縁基板1上に触媒層2を形成し、その上にサポート層3を形成しておく。触媒層2としてCo層を形成し、サポート層としてTiN層を形成する。これらは、例えばスパッタリング法により形成する。次いで、アセチレンを含む原料ガスを用いて熱CVD処理を行う。この結果、触媒層2が絶縁基板1及びサポート層3に挟み込まれているが、カーボン原料はサポート層3を透過して触媒層2まで到達するので、グラファイト11が絶縁基板1と触媒層2との間に成長する。

(もっと読む)

有機化合物含有絶縁層の異方性エッチング

【課題】半導体加工において有機化合物含有絶縁層に小さな穴を形成する方法を提供する。

【解決手段】有機化合物含有絶縁層12を、この有機化合物含有絶縁層12上に形成されたレジストハードマスク層13とこのレジストハードマスク層13上に形成されたレジスト層14からなる2重層で覆い、次に、この2重層をパターニングする。そして、反応チャンバー内に、自然エッチングが実質的に避けられるように選ばれる、あらかじめ決められた割合で存在する酸素ガスと窒素ガスとからなる混合気体を流入し、有機化合物含有絶縁層12をプラズマエッチングする。これにより、レジスト層14を部分的に除去しつつ少なくとも一つの穴を形成する。

(もっと読む)

導電性保護膜を有する貫通電極構造体及びその形成方法

【課題】半導体基板の歪みを抑制することができ、低い接触抵抗を有する貫通電極構造体及びその形成方法を提供する。

【解決手段】貫通電極(Through−Silicon−Via:TSV)構造体は、基板の上部表面から該上部表面に対向する基板の下部表面に延長されて基板を貫通する導電性ビアと、導電性ビアの底部に形成されてNi及びCoのうちのすくなくともいずれかを有する導電性保護膜と、導電性保護膜に接触して基板の下部表面に形成される分離ポリマー絶縁膜と、を備える。

(もっと読む)

半導体装置とその製造方法

【課題】半導体基板の表裏両面間を貫通電極で接続するにあたって、貫通孔底部の角部におけるリーク電流の発生や絶縁膜のクラック等を抑制する。

【解決手段】半導体装置1は貫通孔3を有する半導体基板2を備える。貫通孔3は半導体基板2の第1の面2aに開口された第1の開口3aの開口径が第2の面2bに開口された第2の開口3bに近い側の内径より大きくなるように、第1の面2aの近傍を拡張させる拡張部4を備える。半導体基板2の第1の面2aには第1の絶縁層5と第1の配線層6とが設けられている。貫通孔3には拡張部4を充填しつつ内壁面を覆う第2の絶縁層7が設けられており、さらに第1および第2の絶縁層5、7の開口を介して第1の配線層6と接続された第2の配線層8が設けられている。

(もっと読む)

成膜方法及び処理システム

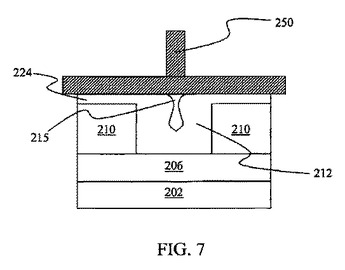

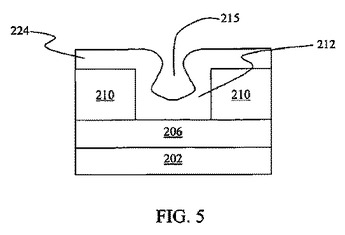

【課題】例えばCu膜に対するバリヤ性及び密着性を高く維持することができる層構造を形成する成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器132内で、表面に凹部2を有する被処理体Wの表面に成膜処理を施す成膜方法において、遷移金属含有原料ガスを用いて熱処理により遷移金属含有膜210を形成する遷移金属含有膜形成工程と、元素周期表のVIII族の元素を含む金属膜212を形成する金属膜形成工程とを有するようにする。これにより、例えばCu膜に対するバリヤ性及び密着性を高く維持する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】基板に発生する応力を低減できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体素子が形成される素子領域を有する基板と、素子領域の隣接部分の基板に形成されるビアホールと、ビアホール内に絶縁層を介して設けられる導通部と、基板と絶縁層との間に設けられる緩衝層とを備え、緩衝層は、基板の熱膨張係数と緩衝層の熱膨張係数との差が、基板の熱膨張係数と絶縁層の熱膨張係数との差より小さい材料から形成される。

(もっと読む)

カーボンナノチューブ系材料の先端部形成方法

【課題】CNT系材料と他の導電体との低接触抵抗を実現でき、あるいは他の導電体との接触に高い信頼性が確保できる技術を提供する。

【解決手段】凹所に設置され、その凹所上の空間にその先端部が突き出たCNT系材料のその突き出た先端部に、酸化性物質であるまたは酸化性物質を発生しうるガス状物質を接触させつつ、活性エネルギー線を照射する。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜を介して隣接し、それぞれ低い抵抗値を有する複数のシリサイド層を備え、かつ複数のシリサイド層間の耐電圧特性の劣化および短絡を抑えた半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板上に、絶縁膜を介して前記半導体基板の表面に略平行な方向に隣接する複数のSi系パターン部を形成する工程と、前記複数のSi系パターン部および前記絶縁膜上に、前記複数のSi系パターン部に接するように金属膜を形成する工程と、熱処理により前記複数のSi系パターン部と前記金属膜とをシリサイド反応させ、前記複数のSi系パターン部の全部または上側の一部をそれぞれシリサイド層に加工する工程と、前記複数のシリサイド層に平坦化処理を施し、前記絶縁膜上に形成されたシリサイド層を除去する工程と、を含む。

(もっと読む)

パターン形成キャップを用いるエアギャップ形成と一体化

【課題】 膜をパターン形成する方法及びこれらの得られた構造を提供する。

【解決手段】 実施形態において、基板、例えば、ダマシン層の上にアモルファス炭素マスクを形成する。アモルファス炭素マスクの上にスペーサ層を堆積させ、スペーサ層をエッチングして、スペーサを形成するとともにアモルファス炭素マスクをさらす。アモルファス炭素マスクを選択的にスペーサまで除去して、基板層をさらす。ギャップ充填層がスペーサの周りに堆積されて、基板層を覆うがスペーサをさらす。スペーサを除去して、選択的に基板の上にギャップ充填マスクを形成する。ギャップ充填マスクのパターンは、一実施態様においては、ダマシン層に転写されて、IMDの少なくとも一部を除去するとともにエアギャップを形成する。

(もっと読む)

半導体装置の製造方法、半導体装置、電気光学装置、および電子機器

【課題】三次元半導体装置における特性を向上させることができる製造方法および装置構成を提供する。

【解決手段】第1半導体膜(9)上にカーボンナノチューブを備えるプラグ電極(15)を形成する工程、形成されたプラグ電極(15)の周囲に層間絶縁膜(16,18)を形成する工程、層間絶縁膜の表面を平滑化してプラグ電極(15)の頂部を露出させる工程、層間絶縁膜およびプラグ電極の頂部上に非晶質の第2半導体膜を形成する工程、非晶質の第2半導体膜にエネルギーを供給して露出したプラグ電極(15)を触媒として機能させて非晶質の第2半導体膜を結晶化させ結晶化した第2半導体膜(23)とする工程を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】Cuを含む配線について、配線抵抗を低く維持しつつ、しかも、ストレスマイグレーション耐性の劣化を伴うことなく、エレクトロマイグレーション耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上方に形成された層間絶縁膜36と、層間絶縁膜36内に形成されたCuより成る配線50と、層間絶縁膜36と配線50の間に形成され、Ti膜42とTa膜44との積層膜より成るバリアメタル膜46とを有し、配線50表面に、TiとSiとを含む界面層54が形成されている。

(もっと読む)

導電性コンタクトの組み込みのための構造体及びプロセス

【課題】 キーホール・シームの形成を排除した信頼性が高い高アスペクト比のコンタクト構造体を含む半導体構造を提供する。

【解決手段】 キーホール・シームの形成は、本発明においては、誘電体材料内部に存在する高アスペクト比のコンタクト開口部内に高密度化貴金属含有ライナを設けることによって排除される。高密度化貴金属含有ライナは拡散バリアの上に配置され、これら両方の要素は、本発明のコンタクト構造体の導電性材料を、下層の半導体構造体の導電性材料から分離する。本発明の高密度化貴金属含有ライナは、第1の抵抗率を有する貴金属含有材料の堆積、及び、堆積した貴金属含有材料の抵抗率をより低い抵抗率に減少させる高密度化処理プロセス(熱又はプラズマ)を、堆積した貴金属含有材料に施すことによって形成される。

(もっと読む)

半導体装置、およびその製造方法

【課題】配線間をCuプラグによって電気的に接続する構成において、Cuプラグとの電気的接続の信頼性が高く、リーク電流が少ない半導体装置、およびその製造方法を提供することを目的とする。

【解決手段】本発明における半導体装置100は、拡散層43およびゲート電極42を形成した半導体基板1と、半導体基板1上に形成された層間絶縁膜5と、層間絶縁膜5を貫通し、拡散層43およびゲート電極42上に形成されたコンタクトホール61と、コンタクトホール61の内面に形成されたTiバリアメタル層62と、バリアメタル層62上に形成されたW、Co、Ru、Ptのいずれかを含むシード層63と、シード層63上であってコンタクトホール61を充填するように形成されたCuプラグ64と、Cuプラグ64上に形成された配線層7と、を備える。

(もっと読む)

相変化メモリデバイスに電極を形成する方法

サブリソグラフィックな寸法又は高アスペクト比を含む、小寸法の開口内に電極材料を均一に形成する方法を提供する。この方法は、内部に形成された開口を有する絶縁層を提供するステップと、開口の上部及び内部に非等質的導電又は準抵抗性材料を形成するステップと、導電材料を移動化して開港内に圧縮するステップとを有する。この方法は、導電又は準抵抗性材料における空孔又は欠陥密度を堆積されたままの状態に対して低減する。移動化するステップは、押出又は熱的リフローによって達成され、空隙又は欠陥を合体、崩壊、染み透り又は他の方法によって堆積したままの導電又は準抵抗性材料から除去する。  (もっと読む)

(もっと読む)

相変化メモリデバイスに電極を形成する気相法

サブリソグラフィック寸法又は高アスペクト比を含む小寸法を有する開口内に均一で均質に電極材料を形成する方法を提供する。この方法は、内側に形成された開口を有する絶縁層を提供し、開口上及び開口内に均質な導電又は準抵抗材料を形成するステップを含んでいる。この方法は、金属窒化物、金属アルミニウム窒化物及び金属ケイ素窒化物電極組成を形成するCLD又はALDプロセスである。この方法は、アルキル、アリル、アルケン、アルキン、アシル、アミド、アミン、イミン、イミド、アジド、ヒドラジン、シリル、アルキルシリル、シリルアミン、キレーティング、ヒドリド、サイクリック、カルボサイクリック、シクロペンタジエニル、ホスフィン、カルボニル又はハライドから選択された1以上のリガンドを含む金属前駆体を利用する。公的な前駆体は、一般式MRnを有し、Mは金属、Rは上述のリガンド、nは主要な金属原子に結合したリガンドの数に対応している。Mは、Ti、Ta、W、Nb、Mo、Pr、Cr、Co、Ni又は他の遷移金属である。  (もっと読む)

(もっと読む)

基板貫通バイアの作製方法

基板貫通バイア(75)を作製する方法であって、バイアは基板(5)の裏面からSTI(14)またはPMD(13)までエッチングされる。金属1コンタクトパッド(55)と基板貫通バイア(75)との間の追加のコンタクト(50)は、基板貫通バイア(75)と半導体チップ(11)のバックエンドオブライン(3)との間のコンタクトを実現するために作製される。  (もっと読む)

(もっと読む)

三次元構造体の製造方法および三次元構造体

【課題】導電体内の欠陥の発生を抑制し、導電体が連続的に形成される三次元構造体の製造方法および三次元構造体を提供する。

【解決手段】第1の導電体上に、絶縁体と、この絶縁体内に、第1の導電体と異なる第2の導電体で構成される縦構造体と横構造体が組み合わされた三次元の擬似導電体構造とを形成する工程と、擬似導電体構造を溶解除去して三次元の空洞を形成し、第1の導電体を露出させる工程と、第1の導電体をシード層として、電解めっき法により第3の導電体を空洞に充填し、三次元の導電体構造を形成する工程を有することを特徴とする三次元構造体の製造方法およびこれによる三次元構造体。

(もっと読む)

81 - 100 / 211

[ Back to top ]