Fターム[5F033JJ15]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Co、Co合金 (211)

Fターム[5F033JJ15]に分類される特許

41 - 60 / 211

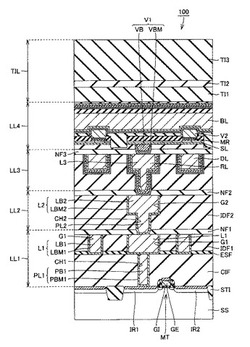

半導体装置および半導体装置の製造方法

【課題】上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板SSと、半導体基板SS上に形成され、周辺配線P1および配線L2が形成された配線層LL1,LL2と、配線層LL2に形成され、配線L3を含む配線層LL3と、配線層LL3上に形成され、磁気記憶素子MRを含む配線層LL4とを備え、配線L1,L2上に形成された拡散防止膜NF1,NF2は、SiCN膜またはSiC膜から形成され、配線L3上に形成された拡散防止膜NF3は、SiNから形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を有する半導体装置において、貫通電極によって被覆された貫通孔の内部を充填する保護層にクラック等が発生する不具合を防止する。

【解決手段】

貫通電極9を被覆するとともに、貫通孔6内を充填する保護層10を備える半導体装置1において、保護層10が複数層11、12からなり、複数層の保護層のうち最も半導体基板2の一面2aに近い層が、少なくとも貫通電極の底面9aと側面9bの交差部を被覆し、かつ、ポジ型感光性樹脂を用いて形成されることを特徴とする半導体装置を提供する。

(もっと読む)

薄膜の形成方法

【課題】埋め込み金属との密着性及び埋め込み特性の改善を図ることができるのみならず、エレクトロマイグレーション耐性も向上させることが可能な薄膜の形成方法を提供する。

【解決手段】表面に凹部8を有する被処理体Wの表面に薄膜を形成する形成方法において、被処理体の表面に埋め込み用の金属膜16して凹部を埋め込む埋め込み工程と、金属膜を覆うようにして被処理体の表面の全面に拡散防止用の金属膜18を形成する拡散防止膜形成工程と、被処理体をアニールするアニール工程とを有する。これにより、埋め込み金属との密着性及び埋め込み特性の改善を図ることができるのみならず、エレクトロマイグレーション耐性も向上させる。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

半導体装置及びその製造方法

【課題】ビアホール内のコンタクト材料としてカーボンナノチューブ(CNT)を用いつつ、ビア抵抗の低減及びプロセスの容易化をはかる。

【解決手段】配線層間のビアにCNTを用いた半導体装置であって、表面にCu配線17を有する基板上に設けられた層間絶縁膜19と、層間絶縁膜19に形成されCu配線17に接続されるビアホールと、ビアホール内に露出するCu配線17上に選択的に形成され、Cu配線17に対するバリアとなり、且つCNTの成長の助触媒となる第1の金属膜21と、ビアホール内の少なくとも第1の金属膜21上に形成された、CNTの成長の触媒となる第2の金属膜22と、第1及び第2の金属膜21,22が形成されたビアホール内に形成されたCNT23と、を備えた。

(もっと読む)

半導体装置及びその製造方法

【課題】ボイドやシームが発生しにくい構造体とする。

【解決手段】本発明の半導体装置は、半導体基板101に形成された層間絶縁膜103と、層間絶縁膜103に形成されたコンタクト孔104と、コンタクト孔104を埋め込むCu膜107と、コンタクト孔104の内部の側壁に形成され、Cu膜107の下地となる金属含有下地膜13と、を備える。コンタクト孔104の開口に接続している側壁の一部を含む第一の領域11において、金属含有下地膜13は、Cu膜107との界面に金属窒化層106を有する。第一の領域11よりも半導体基板101側の側壁を含む第二の領域12において、金属含有下地膜13は、Cu膜107との界面に金属層105を有する。金属層105の表面におけるCu膜107の成膜速度は、金属窒化層106の表面におけるCu膜107の成膜速度よりも大きい。

(もっと読む)

表示装置

【課題】TFTと接続するソース電極あるいはドレイン電極のスルーホールにおけるコンタクト抵抗を減少させ、表示装置の動作効率を向上させる。

【解決手段】スルーホールにおいて、TFTのソース部とソース電極8が接続している。ソース電極8は、バリヤメタル、Al合金82、キャップメタル83の3層から形成されている。バリヤメタルは半導体層と接触する下層81aとAl合金と接触する上層81bとに分かれている。バリヤメタルの下層81aをスパッタリングして形成した後、熱処理し、その後、ベースメタルの上層81b、Al合金82、キャップメタル83を連続してスパッタリングによって形成する。Al合金82と接触するバリヤメタルの上層81bは酸化されていないので、スルーホールにおけるコンタクト抵抗の上昇を防止することが出来る。

(もっと読む)

半導体装置及びその製造方法

【課題】ポーラス絶縁層を用いた半導体装置において、当該ポーラス絶縁層を覆うポアシール絶縁層を良好に形成すること。

【解決手段】本発明に係る半導体装置の製造方法は、(A)ポーラス絶縁層の表面にトレンチを形成する工程と、(B)ビニル基を含み−Si−O−を含む構造を備える化学物質を、ポーラス絶縁層の表面上あるいはポーラス絶縁層中に導入する工程と、(C)当該化学物質の重合を行うことにより、ポーラス絶縁層よりも高密度のポアシール絶縁層をトレンチの表面上に形成する工程と、を含む。

(もっと読む)

表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】表示装置の形成方法は、基板上に下地絶縁層を設け、その層上に配線パターンに沿った第1の銅拡散防止層を設ける。次に、その第1の銅拡散防止層上面に第1の銅拡散防止層の幅より僅かに狭い銅配線層を積層し、銅配線層の全表面を覆うように、第2の金属拡散防止層を設ける方法である。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の銅配線の信頼性をTDDB寿命とEM寿命との双方に関して向上させる。

【解決手段】 半導体装置の配線層30は、配線溝が形成された絶縁膜32、35と、配線溝の内面に形成されたバリアメタル層41と、バリアメタル層41を介して配線溝内に形成された銅配線膜43とを有する。バリアメタル層41は、配線溝の内壁面側から順に形成された第1乃至第3のバリアメタル膜41−1、2、3を有する。第2のバリアメタル膜41−2は、第3のバリアメタル膜41−3側の表面部分において、クラスタイオン照射によって形成された、その他の部分より高い密度の緻密層41−2aを有する。第3のバリアメタル膜41−3は、例えばルテニウム等、銅配線膜43との密着性に優れた材料を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 層間絶縁膜内の水分などによるバリアメタルの腐食を防止し、銅配線の信頼性の低下及び抵抗値の上昇を抑制し得る半導体装置、及びその製造方法を提供する。

【解決手段】 メチル基を含有する層間絶縁膜32内に配線溝37を形成する。配線溝37が形成された絶縁膜32に紫外線又は電子線を照射した後に、メチル基を有するガスを用いて絶縁膜の露出面を疎水化する。配線溝37の疎水化された内面に沿ってバリアメタル層41を形成し、該バリアメタル層41を介して配線溝37を銅配線43で充填する。一実施形態において、配線溝37はメタルハードマスク47を用いて絶縁膜32をエッチングすることにより形成され、絶縁膜32への紫外線又は電子線の照射は、メタルハードマスク47を残存させた状態で行われる。

(もっと読む)

半導体装置およびその製造方法

【課題】研磨時にバリア膜が溶解することを抑制することができるような半導体装置及びその製造装置を提供する。

【解決手段】半導体基板上に形成された、溝109を有する絶縁膜107と、溝109に形成された第1のバリア膜111と第2のバリア膜112とを有する配線115とを備えている。第1のバリア膜111は、溝109の側壁及び底面上に形成され、第2のバリア膜112は、第1のバリア膜111を覆うように溝109に形成されている。さらに、第2のバリア膜112は、配線115の上面よりも下側に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィ法の露光解像限界未満のラインアンドスペースパターンとなる被加工膜のパターンの上層に、その被加工膜のパターンと接続するコンタクトを容易に形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に形成された第2の膜14を、複数の線状部とそれぞれの線状部の一端に形成された線状部よりも幅の広い端部を有するパターンへと加工し、このパターンをスリミングして第1のパターン16を形成し、第1のパターン16の端部141a上を横断する第1の開口180を有する第2のパターンを形成し、第1の開口180内に露出する第2の膜14をエッチングし、端部141aを線状部140aに近い第1の端部142aと、線状部140aと遠い第2の端部143aとに分割することを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】グラフェンのバリスティック伝導性を利用した低抵抗配線を備え、配線と配線接続部材の接続部分の構成の複雑化を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、基板と、基板の上方に設けられ、積層された複数のグラフェンナノリボンシート122からなるグラフェンナノリボン層121を含む下層配線12と、複数のグラフェンナノリボンシート122の少なくとも1枚を貫通し、下層配線12と上層配線13とを接続するビア14およびバリアメタル15と、を有する。

(もっと読む)

銅プラグを有する半導体デバイスおよびデバイスを形成するための方法

【課題】絶縁層がデバイスの最終配線層と接触する銅プラグを有する、半導体デバイスを提供する。

【解決手段】銅プラグと絶縁層とを分離する障壁層も存在可能である。他の実施形態では、絶縁層と銅プラグとの間にアルミニウム層も存在可能である。半導体デバイスを生成するためのプロセスも開示される。

(もっと読む)

無電解銅めっき液、無電解銅めっき方法、及び埋め込み配線の形成方法

【課題】孔の内径の大小にかかわらず、該孔の奥まで均一な無電解銅めっき層を形成しうる無電解銅めっき液および無電解銅めっき方法を提供する。また、該無電解銅めっき層を形成することにより孔の内部に信頼性の高い埋め込み配線を形成することのできる埋め込み配線の形成方法を提供する。

【解決手段】チオール基又はジスルフィド結合を有するポリエチレングリコール化合物、及び銅イオンを含有することを特徴とする無電解銅めっき液、さらに、該無電解銅めっき液に、孔2の形成された基板1を浸漬し、該孔の内部に無電解銅めっき層6を形成することを特徴とする無電解銅めっき方法、及び、該無電解銅めっき液に、孔2の形成された基板1を浸漬し、該孔の内部に無電解銅めっき層6からなる埋め込み配線を形成することを特徴とする埋め込み配線の形成方法。

(もっと読む)

相互接続構造およびこれを形成する方法(細い相互接続開口のための導電性構造)

【課題】電気的抵抗が低い相互接続構造、および、かかる相互接続構造を形成する方法を提供する。

【解決手段】相互接続構造は、少なくとも1つの開口を含む誘電物質を含む。少なくとも1つの開口内には、任意のバリア拡散層、結晶粒成長促進層、凝集めっきシード層、任意の第2のめっきシード層、および導電性構造が配置される。典型的にはCuである金属含有導電性物質を含む導電性構造は、バンブー微細構造を有し、平均グレイン・サイズが0.05ミクロンよりも大きい。いくつかの実施形態では、導電性構造は、(111)結晶方位を有する導電性結晶粒を含む。

(もっと読む)

カーボン・ナノチューブを選択的に成長させる方法

【課題】1つ以上のカーボン・ナノチューブを選択的に成長させる方法を提供する。

【解決手段】本方法は、上面を有する絶縁層を基板上に形成するステップと、絶縁層内にビアを形成するステップと、ビアの側壁及び底面を含め、絶縁層上に活性金属層を形成するステップと、ビアの内部での1つ以上のカーボン・ナノチューブの選択的な成長を可能にするために、イオン・ビームを用いて上面の部分にある活性金属層を除去するステップとを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の再配線層において配線を狭ピッチ化して隣接する配線間距離が著しく近接しても、配線間でイオンマイグレーションを効果的に抑制する。

【解決手段】一方の主面11aに半導体デバイスおよび電極11cが設けられた半導体基板11と、一方の主面11aの上に形成された層間絶縁層12と、層間絶縁層12上において個々の配線パターンに沿って複数形成されたポリイミドからなる樹脂パターン部13と、樹脂パターン部13の上にそれぞれ形成された再配線層14と、再配線層14の上を封止する封止絶縁層15とを有し、樹脂パターン部13の側面13aが、配線パターンの長手方向に垂直な断面において凹凸状とされている。

(もっと読む)

41 - 60 / 211

[ Back to top ]