Fターム[5F033JJ29]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | シリサイド (585) | 高融点金属のシリサイド (433) | MoSi (28)

Fターム[5F033JJ29]に分類される特許

1 - 20 / 28

半導体装置及びその製造方法

【課題】占有面積の小さい抵抗体を有する半導体装置を提供する。

【解決手段】半導体基板上のフィールド酸化膜の上に導電性多結晶シリコンを形成し、その上を覆う絶縁膜に多結晶シリコン5に達するコンタクトホールを形成する。コンタクトホールの中にはタングステンサイドウォール9、シリコン酸化膜サイドウォール10、抵抗体11があり、抵抗体の上には電極12を配置することで上下方向に縦長の抵抗体11とする。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

金属の付着

システム及び方法が、電圧切り換え可能な誘電体材料に1つ以上の材料を付着させることを含む。特定の態様では、電圧切り換え可能な誘電体材料が、導電バックプレーン上に配置される。いくつかの実施形態では、電圧切り換え可能な誘電体材料が、付着に関する特性電圧が相違する複数の領域を含む。いくつかの実施形態は、マスキングを含み、取り除くことが可能なコンタクトマスクの使用を含むことができる。特定の実施形態は、電気グラフトを含む。いくつかの実施形態は、2つの層の間に配置される中間層を含む。 (もっと読む)

半導体装置及びその製造方法

【課題】導電プラグの酸化を抑止し、コンタクト抵抗の安定化された信頼性の高い半導体装置を実現する。

【解決手段】下部電極101と上部電極103とで強誘電体膜102を挟持してなる強誘電体キャパシタ構造100と、導電プラグ110との間に、酸化しても導電性を有する導電材料(例えば金属)からなる導電層112を形成し、ここでは、導電プラグ110の下地膜を導電層112(Ag,Ni,Cu,Zn,In,Sn,Ir,Ru,Rh,Pd,Osから選ばれた少なくとも1種を材料として形成される。)とする。

(もっと読む)

半導体装置の製造方法および固体撮像装置の製造方法

【課題】本発明は、コンタクト抵抗の安定性を確保して、コンタクト抵抗にばらつきを抑えることを可能にする。

【解決手段】基板11のシリコン領域12上に第1金属シリサイド層13を形成する工程と、前記基板11上に前記第1金属シリサイド層13を被覆する絶縁膜14を形成する工程と、前記絶縁膜14に前記第1金属シリサイド層13に通じるコンタクトホール15を形成する工程と、前記コンタクトホール15の内面および前記絶縁膜14上にシリサイド化される第2金属層16を形成する工程と、前記第2金属層16と前記コンタクトホール15の底部のシリコンとを反応させて前記第1金属シリサイド層13上に第2金属シリサイド層17を形成する工程とを有する。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 微細化に伴うコンタクト抵抗の増加を防止した、信頼性の高い素子特性を有する薄膜半導体装置を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、及び前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成された第1及び第2のコンタクト孔内にそれぞれ埋め込まれた第1導電型の不純物を含む凸型ソース多結晶半導体層並びに第1導電型の不純物を含む凸型ドレイン多結晶半導体層を具備することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】上層側と下層側の導電プラグの接続抵抗が低減された、形成が容易な積層プラグ構造を有する半導体装置を提供する。

【解決手段】不純物含有多結晶シリコンからなる第1の導電プラグと、金属からなる第2の導電プラグと、第1の導電プラグと第2の導電プラグを接続する接続導電層とを有する半導体装置であって、前記接続導電層は、第1の導電プラグの端部に接続する金属シリサイド層と、この金属シリサイド層に積層され、第2の導電プラグの端部に接し且つ第2の導電プラグを構成する金属と同種の金属からなる金属層とを有する。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】Oリングをシール部材に用いた処理室で、半導体基板上の金属シリサイド形成を行う熱処理工程において、処理室に酸素等不純物ガスを引込まない半導体装置の製造方法及び半導体製造装置を提供する。

【解決手段】処理室20に連通する第1の排気管32と、第1の排気管32の排気を遮断するためのバルブ33と、第1の排気管32より排気量の小さな第2の排気管34と、を有し、第2の排気管34をバルブ33と処理室20との間に前記第1の排気管32から分岐して設け、バルブ33を閉じることにより、処理室20を大気圧より高い圧力の状態に維持する。

(もっと読む)

シード印刷及びめっきによるコンタクト金属及び相互接続金属の印刷

シリサイド形成金属を含むインクを用いて、コンタクト形成方法、そのコンタクト及び局所相互接続を含むダイオード及び/又はトランジスタ等の電気デバイスとその形成方法に関する。コンタクト形成方法は、露出したシリコン表面上にシリサイド形成金属インクを堆積させるステップと、インクを乾燥させ、シリサイド形成金属前駆体を形成するステップと、シリサイド形成金属前駆体及びシリコン表面を加熱して、金属スイサイドコンタクトを形成するステップとを含む。任意選択的に、露出したシリコン表面に隣接する誘電体層上に、金属前駆体インクを選択的に堆積させて、金属含有相互接続を形成できる。更に、1つ又は複数のバルク導電性金属を、残りの金属前駆体インク及び/又は誘電体層上に堆積させてもよい。かかる印刷したコンタクト及び/又は局所相互接続を用いて、ダイオード及びトランジスタ等を作製できる。 (もっと読む)

半導体装置の製造方法

【課題】プラグまたは局所配線による接続で低い接続抵抗と十分に小さい拡散層リーク電流を実現し、更に深さが異なる接続孔や開口断面の断面の形状や大きさが異なる接続孔または局所配線穴を用いる場合でも、十分に小さい拡散層リーク電流と低い接続抵抗を実現する製造方法を提供する。

【解決手段】基体上の絶縁膜に開口した、表面がシリコンを主成分とする層が底部に露出している第1の開口部(接続孔または局所配線穴)の群と、表面が第1の金属珪化物を主成分とする層が底部に露出している第2の開口部の群と、表面が第1の金属を主成分とする層が底部に露出している第3の開口部の群のうちの、少なくとも2群の各開口部の底部に、第2の金属珪化物を主成分とする層また第2の金属を主成分とする層を、化学気相成長法によって同時に形成する。

【効果】従来以上に高集積、高性能の半導体装置が実現される。

(もっと読む)

半導体装置およびその作製方法

【課題】無線信号から生成できる電流値及び電圧値の範囲内で駆動できるメモリを搭載した半導体装置を提供することを課題とする。また、半導体装置製造後にデータの書き込みを行える追記型のメモリを提供することも課題とする。

【解決手段】絶縁表面を有する基板上にアンテナと、アンチヒューズ型のROMと、駆動回路とを形成する。アンチヒューズ型のROMを構成する一対の電極の間に、シリコン膜とゲルマニウム膜との積層を設ける。この積層を有するアンチヒューズ型のROMは、書き込み電圧のバラツキを低減することができる。

(もっと読む)

集積回路デバイスとその製造方法

【課題】基板と複数のマイクロ電子デバイスを備える集積回路デバイス及びその方法を提供する。

【解決手段】少なくとも一つのマイクロ電子デバイス150に電気的に接触する導電性相互接続部を備える第1の層と、第1の層のラインに対して直角に整列された導電性のラインを備える第2の層であってかつ第2の層のラインが第1の層のラインと電気的に接触している第2の層と、第2の層のラインに対して直角に整列された導電性のラインを備える第3の層であってかつ第3の層のラインが第2の層のラインと電気的に接触している第3の層とを備え、第1の層を第2の層に相互接続し、かつ第3の層を第2の層に相互接続する複数のバイア224等を備える。

(もっと読む)

半導体装置

【課題】外部から曲げ等の物理的な力が加わり応力が生じた場合であってもトランジスタ等の素子の損傷を抑制する半導体装置を提供することを目的とする。

【解決手段】基板上に設けられ、チャネル形成領域と不純物領域とを具備する半導体膜と、チャネル形成領域の上方にゲート絶縁膜を介して設けられた第1の導電膜と、第1の導電膜を覆って設けられた第1の層間絶縁膜と、第1の層間絶縁膜上に、少なくとも不純物領域の一部と重なるように設けられた第2の導電膜と、第2の導電膜上に設けられた第2の層間絶縁膜と、第2の層間絶縁膜上に、開口部を介して不純物領域と電気的に接続するように設けられた第3の導電膜とを設ける。

(もっと読む)

炭素ナノチューブ配線の形成方法及びこれを用いる半導体素子配線の形成方法

【課題】界面破壊現象が発生しない炭素ナノチューブ配線の形成方法及びこれを利用した半導体素子配線の形成方法が開示されている。

【解決手段】基板上に酸化金属膜を形成した後、前記酸化金属膜上に前記酸化金属膜の表面を露出させる開口を含む絶縁膜パターンを形成する。前記開口に露出された前記酸化金属膜を炭素ナノチューブの成長が可能な触媒金属膜パターンに形成する。前記触媒金属膜パターンから炭素ナノチューブを成長させて炭素ナノチューブ配線を形成する。前述した炭素ナノチューブ配線の形成方法は、前記絶縁膜パターンと触媒金属膜パターンとの間で炭素ナノチューブが成長する現象を防止することができる。

(もっと読む)

相変化メモリ装置およびその製造方法

【課題】相変化メモリ装置のメモリセル部における、相変化領域の上側ならびに下側の金属からの放熱を共に抑制し、熱効率の低下を最小限化して、大規模な相変化メモリ装置の量産を可能とすること。

【解決手段】相変化層の下側のコンタクトプラグからの放熱は、異種材料コンタクトプラグ104を採用して抑制する。すなわち、第2の導電材料に比べて比抵抗が大きい(逆に、熱伝導率は小さい)第1の導電材料からなる第1の導電材料プラグ106にヒータ電極110を接続することによって、放熱を抑制する。相変化層の上側の電極からの放熱は、引き出し電極116を用いた、相変化領域(ヒータ電極110の上面112の近傍)の直上に電極を設けない電極構造の採用によって抑制する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体プロセスの微細化に伴い、信頼性の高い微細なゲート電極の形成がより困難なものとなっている。

【解決手段】ゲート電極105の上面に加え、ゲート電極105の側面に対しても金属シリサイド110を形成することで、ゲート電極105を所望の太さの幅に拡大しなくても、信頼性の高いゲート電極105を形成することができる。

(もっと読む)

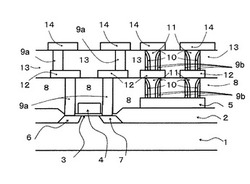

電気光学装置及びその製造方法、並びに導電層の接続構造

【課題】画素の開口率を高める。

【解決手段】液晶装置1は、TFTアレイ基板10上の互いに異なる層に夫々形成されており、第2層間絶縁膜42を介して互いに電気的に絶縁された上部容量電極300及び下部容量電極71、サイドウォール91、接続用導電膜93、誘電体膜75及びコンタクトホール85を備えている。接続用導電膜93によれば、コンタクトホールを形成する際のマージンを確保するために広げざるを得なかった下部容量電極71及び上部容量電極300の面積を低減でき、画素毎の開口領域の間隙に位置する非開口領域を低減することが可能である。これにより、画素における非開口領域の幅W1をサイドウォール91の幅W2に応じて低減でき、非開口領域を狭めることによって画素における開口率を高めることが可能である。

(もっと読む)

相変化メモリ装置および相変化メモリ装置の製造方法

【課題】相変化メモリ装置における良好な電気特性と良好な熱特性を両立させ、電極や配線の材料選択の自由度も高めて、大規模な相変化メモリ装置の量産を可能とすること。

【解決手段】ヒータ電極110と相変化層114の接触界面112の近傍で発生するジュール熱が、ヒータ電極110を介して下方に伝達され、下地の良導電性の金属コンタクトプラグから放熱されることを抑制するために、異種材料コンタクトプラグ104(106,108)を採用する。ヒータ電極110に接触する第1の導電材料プラグ106は、ヒータ電極110の構成材料と同種または同じ金属材料からなり、第2の導電材料プラグ108は、接地電位用プラグ100や接地配線102と同種あるいは同じ金属材料からなる。両プラグ106,108は、共通のコンタクトホール内に積層形成される。

(もっと読む)

半導体装置

【課題】導電プラグの酸化を抑止し、コンタクト抵抗の安定化された信頼性の高い半導体装置を実現する。

【解決手段】下部電極101と上部電極103とで強誘電体膜102を挟持してなる強誘電体キャパシタ構造100と、導電プラグ110(プラグを構成する導電物は例えばタングステン(W))との間に、シリサイド膜111を形成する。ここでは、導電プラグ110の下地膜をシリサイド膜111とする場合を例示する。

(もっと読む)

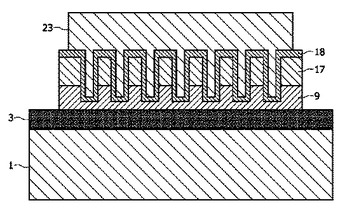

改良された接触パッドを有する半導体デバイスとその製造方法

半導体デバイスおよびその製造方法が開示される。このデバイスは、1以上の導電性ゲート(11)を具えた活性半導体領域(1A)と、前記活性半導体領域(1A)の周辺に位置し主としてフィールド酸化領域(3)よりなるコンタクト領域(1B)とを具える。周辺コンタクト領域(1B)上、および、少なくとも一部の活性半導体領域(1A)上に、導電性ゲート(11)の間にコンタクト窓(19a)が形成された絶縁層(17)が積層される。絶縁層(17)上に積層された金属コンタクトパッド(23)が、前記コンタクト領域(1B)に設けられる。この金属コンタクトパッド(23)は、導電性のパターンを介して、絶縁層(17)の下に埋設されているコンタクトストリップ(15)に接触し、この導電性のパターンは、コンタクト窓(19b)充填物の複数個で構成されており、コンタクトパッド(23)の実質的な領域を横切って延びている。このパターンは平行な一連のトレンチに充填されたもので構成されているのが好ましい。  (もっと読む)

(もっと読む)

1 - 20 / 28

[ Back to top ]