Fターム[5F033KK00]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020)

Fターム[5F033KK00]の下位に属するFターム

半導体基板 (2,232)

半導体(基板を除く) (1,188)

金属及びその合金(シリサイドを除く) (9,842)

シリサイド (1,324)

化合物 (2,201)

透光性導電膜材料 (79)

超伝導材料 (11)

Fターム[5F033KK00]に分類される特許

121 - 140 / 143

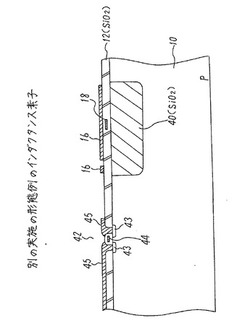

半導体基板状に形成されるインダクタンス素子

【課題】半導体基板上に形成されるインダクタンス素子の特性損失を少なくする。

【解決手段】インダクタンス素子を構成する巻き線状の帯状導電膜の下の半導体基板表面に、酸素のイオン注入法により形成される厚い絶縁領域を形成する。この絶縁領域は、通常の集積回路素子領域上に形成される配線用の薄い絶縁膜より大きな膜厚を有する。かかる構成にすることにより、帯状導電膜内に発生する渦電流の経路をなくし、渦電流を抑制して特性損失を抑えることができる。

(もっと読む)

膜パターンの形成方法、半導体装置、電気光学装置、及び電子機器

【課題】 バンクに撥液化処理を行う際の、機能膜へのダメージを解消した膜パターンの形成方法と、これによって得られた膜パターンを備えた半導体装置、電気光学装置、及び電子機器を提供する。

【解決手段】 基板Pに設けられたゲート絶縁膜28(機能膜)上に機能液を配置して膜パターンを形成する方法である。基板Pにゲート絶縁膜28を設け、ゲート絶縁膜28上にポリシラザン液、ポリシラン液またはポリシロキサン液のいずれかを塗布し乾燥してバンク膜31を形成する。そして、マスクMを用いてバンク膜31を選択的に露光し、バンク膜31に撥液処理を施す。バンク膜31を現像処理することでゲート絶縁膜28を露出させ、パターン形成領域を区画するバンクを形成する。パターン形成領域に前記機能液を配置し、膜パターンを形成する。少なくとも、バンク膜31に撥液処理を施す工程は、バンク膜31を現像処理しバンクを形成する工程より前の工程で行う。

(もっと読む)

電子部品

【課題】 高信頼かつ低電気抵抗で、コスト面でも有利な電子部品を提供する。

【解決手段】 チップサイズパッケージの電子部品2は、a)導電パターン11が形成された基板10と、b)一部分が導電パターン11に接続され、他の部分が、大略、基板10と間隔を設けて基板10に沿って延在する内部配線14,15と、c)内部配線14,15に関して基板10とは反対側に配置され、基板10の表面を保護する保護膜16とを備える。内部配線14,15は、複数層からなり、その保護層16側の最表層15の主材料がPtである。

(もっと読む)

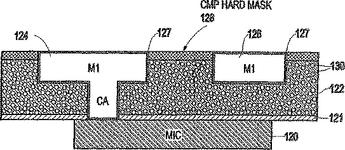

半導体装置およびその製造方法

【課題】 層間絶縁膜の表面に埋込配線を形成する場合に、研磨面の平坦性を保つことができる半導体装置の製造方法を提供すること。

【解決手段】 基板200上に、層間絶縁膜203と、この層間絶縁膜を保護する絶縁性材料からなる第1のハードマスク204と、第2のハードマスク205とを成膜する。第2のハードマスク205を開口し、第2のハードマスク205をマスクとして、層間絶縁膜203に埋込配線が埋め込まれるべき凹溝207を形成する。埋込配線の材料209が層間絶縁膜203へ拡散するのを防止する拡散防止膜208Bを成膜する。第2のハードマスク205と拡散防止膜208Bとが同じ材料で、金属元素を組成に含む導電性材料からなる。埋込配線の材料となる導電性金属209を堆積する。導電性金属209の表面側から第1のハードマスク204が露出するレベルまで研磨を行う。

(もっと読む)

膜パターンの形成方法、アクティブマトリクス基板、電気光学装置、及び電子機器

【課題】 分断されたパターン形成領域にキャップ層を有した膜パターンを形成する際に、その形成工程を簡略化することにより、膜パターンの生産性を向上した、膜パターンの形成方法、アクティブマトリクス基板、電気光学装置、及び電子機器を提供する。

【解決手段】 基板P上に、第1のパターン形成領域52,53と、交差部56で分断される第2のパターン形成領域55とを備えるパターン形成領域を区画するバンク51を形成する。そして、第1のパターン形成領域52,53に第1の膜パターンを、第2のパターン形成領域に第2の膜パターンを形成した後、基板の全面に撥液処理を施す。その後、第2の膜パターンの各所定の位置の撥液性を選択的に保持させたまま、基板上の撥液性を低下させる。第1の膜パターン、及び第2の膜パターン上にキャップ層を積層し、第2の膜パターンの各所定の位置における撥液性を除去し、各所定の位置間に導電膜により接続する。

(もっと読む)

積層構造を備えた集積回路構造およびその製造方法

【課題】銅または銅合金からなる導電性のダマシン構造を含んだ集積回路構造のバリア層の形成方法を提供する。

【解決手段】導電構造(16、22)の側壁には、金属層、中間層が交互に積層され、少なくとも3つの層を含んだ積層構造(32)が設けられている。積層構造(32)の中に非常に薄い層があるにもかかわらず、外部電流を用いて銅を電解析出するために必要な導電率の高さに起因した銅の拡散に対する、高い障壁作用が得られる。

(もっと読む)

半導体デバイスのローカル及びグローバル配線の形成方法

【課題】 異なる回路に対する異なる後工程(BEOL)配線を同一の半導体デバイス、即ちウェハ又はチップの上に形成する方法を開示する。

【解決手段】 1つの実施形態において、この方法は、第1誘電体層(110)内のデュアル・ダマシン構造体(124)を用いて第1回路(102)の上のBEOL配線と、第1誘電体層(110)内のシングル・ダマシン・ビア構造体(126)を用いて第2回路(104)の上のBEOL配線とを同時に形成するステップを含む。次に、この方法は、第2誘電体層(150)内のデュアル・ダマシン構造体(220)を用いて第1回路(102)の上のBEOL配線と、第2誘電体層(150)内のシングル・ダマシン・ライン配線構造体(160)を用いて第2回路(104)の上のBEOL配線とを同時に形成するステップを含む。シングル・ダマシン・ビア構造体は、デュアル・ダマシン構造体のビア部分の約2倍の幅を有し、シングル・ダマシン・ライン配線構造体は、デュアル・ダマシン構造体のライン配線部分の約2倍の幅を有する。異なる回路に対する異なる幅のBEOL配線を有する半導体デバイスもまた開示される。

(もっと読む)

半導体装置

【課題】 半導体形成プロセスによって形成してある抵抗体装置において、抵抗値の変更のための修正にかかる時間と費用の削減を図れるようにすることを目的とする。

【解決手段】 抵抗体22上にその長手方向に沿って全長に亘ってN個のコンタクト23−1〜23−Nが等間隔で分散して形成してあり、アルミ配線パターン24、25がN個のコンタクト23−1〜23−Nのうちから選択した二つのコンタクト23−1と23−Nとに接続してある。抵抗値を変更する場合には、アルミ配線パターンだけを変更して、目的とする抵抗値に対応した別のコンタクトに接続して形成される。

(もっと読む)

膜パターンの形成方法、デバイスの製造方法、電気光学装置、並びに電子機器

【課題】隔壁により区画領域を設けて液滴塗出法により液滴を配置する際に、区画領域端部で液滴が十分に塗れ広がらず空隙が残ったり、局所的に膜厚が薄くなったりしてしまう、という課題を解決することを目的とする。

【解決手段】本発明の膜パターンの形成方法は、機能液の液滴を基板上に配置することにより膜パターンを形成する膜パターンの形成方法であって、前記基板上に前記膜パターンに応じた隔壁を形成する工程と、前記隔壁によって区画された領域に前記機能液の液滴を配置する工程とを有し、前記区画領域の端部は曲率を持たせて形成し、液滴が塗れ広がる距離を短くして機能液の充填性を向上させる。

(もっと読む)

半導体装置およびその製造方法

【課題】配線の引き出し性が向上されているとともに、配線間の短絡などの電気的問題が生じるおそれが抑制されており、かつ、配線が形成される領域の省スペース化が図られた半導体装置を提供する。

【解決手段】半導体装置1が備える基板4上の所定の層内に、第1の配線3が複数本並べられて設けられている。各第1の配線3は、それらの並べられた方向に沿って一方の側から他方の側へ向かうに連れて長く延ばされて形成されているか、あるいは短く縮められて形成されている。それとともに、各第1の配線3は、隣接するそれぞれの一端部3aが並べられた方向と直交する方向において互いにずれた位置に配置されている。

(もっと読む)

半導体集積回路

【課題】 標準的なロジック半導体集積回路製造工程において高密度コンデンサを形成した半導体集積回路を提供する。

【解決手段】 各同電位の電極、灰色部どうし、斜線部どうしはコンタクトホールによって接続され、M(1)層では灰色部分の電極が格子パターンとなり外周部から電極端子を引き出すことが可能となっている。また、M(2)層では斜線部分の電極が格子パターンとなり外周部より電極端子を引き出すことができる。このように構成することによって矩形電極と格子電極により効率よくコンデンサを形成できる。また、これらを形成するのに通常の製造工程から特別の工程を追加することなく製造することができる。

(もっと読む)

配線パターン形成方法および配線パターン

【課題】液滴吐出装置から液滴を吐出してTFT用ソース電極またはドレイン電極を設けること。

【解決手段】基板10Aの表面Sにヘキサメチルシラザンを基板10Aの表面Sに塗布し、HMDS層12を形成するヘキサメチルシラザン層形成工程と、HMDS層12上に、有機感光性材料層を形成する有機感光性材料層形成工程と、前記有機感光性材料層をパターニングしてバンクパターン18を形成する工程と、バンクパターン18によって縁取られた領域に、インクジェット法を用いて、導電性材料を付与する導電性材料付与工程と、を含んでいる。

(もっと読む)

薄膜パターン形成方法、半導体装置、電気光学装置、及び電子機器

【課題】 薄膜形成領域の断面全域に機能液を充填することにより、形成される薄膜の機能を実現するために充分な断面積と必要な断面形状を有する薄膜を形成することができる、薄膜パターン形成方法、半導体装置、電気光学装置、及び電子機器を実現する。

【解決手段】 薄膜パターン形成方法は、第1の薄膜を構成する材料を含む機能液に対して親液性を有する第2の薄膜を形成するステップと、第2の薄膜の表面に、機能液に対する撥液性を付与する処理を行うステップと、第2の薄膜の一部を取り除いて、第1の薄膜のパターン形状を規定する凹部を形成するステップと、凹部に向けて機能液を吐出するステップと、凹部に吐出された機能液を乾燥させて第1の薄膜を形成するステップとを有する。半導体装置の回路配線は、上記薄膜パターン形成方法を用いて形成されており、電気光学装置は当該半導体装置を備え、電子機器は上記電気光学装置を備える。

(もっと読む)

パターン形成構造、パターン形成方法、デバイス及び電気光学装置、電子機器

【課題】パターン形成時に、微細パターンと他のパターンとの各々の高さを同じくすることにより、パターンを含む領域の上面に平坦領域を形成するバンク構造体、パターン形成方法、及び電気光学装置、電子機器を提供する。

【解決手段】機能液により形成するパターンに対応した凸部35が設けられた隔壁構造体であって、第1パターンに対応して設けられた第1凹部55と、第1パターンに接続され、かつ、第1パターンよりも幅が狭い第2パターンに対応して設けられた第2凹部56と、第1凹部55に少なくとも1以上設けられた凸部35と、を備えることを特徴とする。

(もっと読む)

CMP後のポロゲン・バーンアウト・プロセス

【課題】 ライナによって確実に導体が低k誘電体内に拡散するのを防ぐ集積回路構造を提供する。

【解決手段】 論理および機能デバイスを含む少なくとも第1の層を形成し、第1の層の上に少なくとも1つの相互接続層を形成する集積回路構造を形成するための方法および構造を開示する。相互接続層は、論理および機能デバイス間に電気的接続を形成するように構成されている。相互接続層は、まず誘電体層を形成することによって作成される。誘電体層は、第1の材料および第2の材料を含み、第2の材料は、製造環境条件(例えば以下で論じる処理条件)における安定性が第1の材料よりも低い。「第2の材料」はポロゲンを含み、「第1の材料」はマトリックス・ポリマを含む。そして、本発明は、誘電体層における導電性フィーチャを形成し、誘電体層から第2の材料を(例えば加熱によって)除去して、相互接続層内で第2の材料が位置していた場所に空気ポケットを生成する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】タングステン層の抵抗値の上昇を抑えることができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、半導体基板(1)上に層間絶縁膜(2)を形成するステップと、前記層間絶縁膜(2)の内部に延びるコンタクトホールを形成するステップと、前記コンタクトホールの底面部及び側壁部にバリアメタル層(4)を形成するステップと、前記バリアメタル層(4)が形成された前記コンタクトホールに、フッ素を含む材料からタングステン層(5)を形成するステップと、ポストパージにより前記タングステン層(5)から前記フッ素を除去するステップとを具備している。

(もっと読む)

電源配線構造、該電源配線構造を備えた半導体集積回路、電源配線方法ならびに該電源配線方法を用いる半導体集積回路設計方法

【課題】エレクトロマイグレーションの発生を抑制できる電源配線構造を提供すること。

【解決手段】本電源配線構造は、互いに異なる配線層である第1、第2の電源配線1010,1030を備え、かつ、前記両電源配線1010,1030が互いの交差領域でビア1060により電気的に接続されている電源配線構造であって、前記交差領域から第1の電源配線1010の配線方向1020に第2の電源配線1030が延長されて第3の電源配線1070が構成され、かつ、第1および第3の電源配線1010,1070がビア1060により電気的に接続されている。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】 溝とビアを有する低誘電率絶縁膜上にバリアメタルを成膜する前のビア底の高抵抗層の除去手段として、プラズマによる絶縁膜ダメージのない半導体装置の製造方法及び製造装置を提供する。

【解決手段】 溝とビアを有する低誘電率絶縁膜102上にバリアメタルを成膜する前に、ビア底の高抵抗層104を、還元性のガスを用いた熱還元法にて除去し、真空保持のまま、バリアメタル105、めっきのシード層としての銅を形成する。

(もっと読む)

多孔性ダイヤモンド・フィルムの製造

マイクロエレクトロニック構造を形成する方法が記述される。それらの方法は、基板上にダイヤモンド層を形成し、そこではダイヤモンド層の一部が欠陥を含み、その後、ダイヤモンド層から欠陥を除去することによってダイヤモンド層内に空孔を形成する。 (もっと読む)

アモルファス炭素膜のCVD堆積用の液体前駆体

アモルファス炭素材料を堆積するための方法が提供される。一態様では、本発明は、処理チャンバに基板を位置決めするステップと、該処理チャンバに処理ガスを導入するステップであって、該処理ガスがキャリアガス、水素および1つ以上の前駆体化合物を含むステップと、二重周波数RF源から電力を印加することによって該処理ガスのプラズマを生成するステップと、該基板上にアモルファス炭素層を堆積するステップとを含む基板処理方法を提供する。 (もっと読む)

121 - 140 / 143

[ Back to top ]