Fターム[5F033KK00]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020)

Fターム[5F033KK00]の下位に属するFターム

半導体基板 (2,232)

半導体(基板を除く) (1,188)

金属及びその合金(シリサイドを除く) (9,842)

シリサイド (1,324)

化合物 (2,201)

透光性導電膜材料 (79)

超伝導材料 (11)

Fターム[5F033KK00]に分類される特許

21 - 40 / 143

半導体装置およびその製造方法

【課題】高い耐電圧特性、および耐リーク特性を有する配線構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体素子が設けられた基板と、前記基板上に形成された第1および第2の配線と、前記第1の配線の下面の前記第2の配線側に接続されたビアと、前記ビアを含むビア層絶縁膜と、を有する半導体装置を提供する。前記ビアは、前記第1の配線と前記第2の配線の間の領域である配線間領域下の上端に凹部を有する。前記ビア層絶縁膜は、前記第1および第2の配線の幅方向に前記ビアと隣接する領域を含む溝を前記配線間領域の下に有する。前記配線間領域および前記溝内にはエアギャップが含まれる。

(もっと読む)

基板の製造方法、半導体装置の製造方法、電気光学装置

【課題】任意の方向に傾斜した開口部を形成可能な基板の製造方法、半導体装置の製造方法、およびこれを適用した半導体装置を備えた電気光学装置を提供すること。

【解決手段】本適用例の素子基板101の製造方法は、素子基板101上に設けられた半導体装置としてのTFT110を覆うと共に第1開口部としての孔104aが設けられた第2絶縁膜としての層間絶縁膜104をマスクとして、素子基板101の面法線101aと交差する一の方向からドライエッチングを第1絶縁膜としてのゲート絶縁膜103に施して、孔104aに連通すると共にTFT110のドレイン電極110dに開口する第2開口部としての孔103aを形成する。

(もっと読む)

半導体装置及びその製造方法

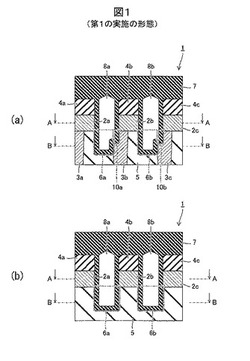

【課題】外力を受けても変形あるいは破壊しにくい半導体装置の構造及びその製造方法を提供する。

【解決手段】半導体基板1表面に第1の掘り込み部を形成する。複数の配線電極3は第1の掘り込み部に埋め込まれた埋め込み部と半導体基板1上に露出する露出部とからなる。複数の配線電極のうち所定の配線電極3間にエアーブリッジ電極6が設けられている。配線電極3とエアーブリッジ電極6との接続は、配線電極3の露出部に第2の掘り込み部を形成し、エアーブリッジ電極6の脚部の接続部を第2の掘り込み部に埋め込むことによって行う。

(もっと読む)

回路基板の製造方法、タッチパネル、電気光学装置、電子機器

【課題】互いに交差し、絶縁膜を介して前記絶縁膜上を配線するブリッジ配線の導通不良の原因の絶縁膜のしみ上がりを防ぐ。

【解決手段】互いに交差する複数の配線と、前記複数の配線の交差部において、前記配線間に形成される絶縁層とを含む回路基板の製造方法であって、基板配線形成工程と、絶縁層を形成する絶縁層形成工程と、前記絶縁層の表面に前記基板配線に交差するブリッジ配線を形成するブリッジ配線形成工程とを含み、前記絶縁膜形成工程は、前記絶縁膜の材料を含む機能液を液滴として吐出する液滴吐出工程を含み、前記機能液はレベリング剤を含む。

(もっと読む)

電子デバイスの製造方法

【課題】カーボン膜の抵抗率を低減することができる電子デバイスの製造方法を提供する。

【解決手段】基板11が載置されたチャンバ4内に炭素を含有する原料ガスを供給する。基板11の周囲からチャンバ4内のアノード1に向けて電子を放出させてチャンバ4内にプラズマ14を発生させ、基板11上にグラファイト、グラフェン等のカーボン膜を形成する。

(もっと読む)

導体層の形成方法及び半導体装置の製造方法

【課題】レジスト残滓を確実に除去する。

【解決手段】基板10上の一部にレジスト20を用いて導体層19をパターニングした後、レジスト20を剥離するレジスト剥離工程と、基板10の導体層19が形成された面に対して、第一ノズル103から第一噴射圧で溶剤を噴射することによりレジスト20の残滓20bをふやかし、第二ノズル104から第一噴射圧よりも高圧の第二噴射圧で溶剤を噴射することによりレジスト20の残滓20bを物理力で除去するレジスト残滓除去工程と、を備える導体層の形成方法である。

(もっと読む)

方向転換されたカーボンナノチューブで作られた相互接続構造

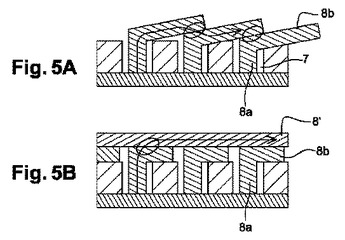

本発明は、少なくとも2つの異なる方向に沿って伸びる電気接続を含む電子デバイスであって、前記接続は本質的にカーボンナノチューブの束(CNT)(8)を用いて形成され、少なくとも2つのCNT束は、第1方向に沿った軸を有する部分(8a)と、第2方向に沿って方向転換された軸を有する部分(8b)とを含み、前記CNT束間の接続は前記少なくとも2つの束の一部分(8b)の重なりによって達成され、接続ライン(4)を形成する、電子デバイスに関する。  (もっと読む)

(もっと読む)

半導体装置、三次元集積回路およびその製造方法

【課題】回路動作時の基板での損失を低減し、表面および裏面の両面において多層配線を形成することで配線の自由度を向上させ、なおかつ貫通配線の配線長を短縮して信号の伝達を高速化する。

【解決手段】薄膜半導体素子2はSOIウェーハを用いて形成し、そのシリコン基板から取り外されているため、素子厚さは埋め込み酸化膜を含めても、例えば2μm以下である。また、貫通配線6は、装置の表面と裏面を貫通するのではなく、薄膜半導体素子に隣接して、コンタクトビア形成時に一括で形成するため、その直径が薄膜半導体素子のコンタクトビアと同程度で、長さが薄膜半導体素子の厚さと同程度である。

(もっと読む)

パターン形成方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等のパターンを作製する方法、さらには、層間絶縁膜、平坦化膜、ゲート絶縁膜等の絶縁膜、配線、電極、端子等の導電膜、半導体膜等の半導体素子の各部位の膜、良好なマスクパターン、及びコンタクトホールを形成する方法を提案し、更には低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】本発明の一は、膜上にぬれ性の低い1のマスクパターンを形成した後、第1のマスクパターンを介して、膜上にぬれ性の高い材料を塗布又は吐出して第2のマスクパターンを形成し、第1のマスクパターンを除去して、第2のマスクパターンをマスクとして第1の膜の一部を除去する。

(もっと読む)

半導体装置

【課題】ダイシングブレードでダイシングする際の層間絶縁膜間の密着性を良好にしつつ、層間絶縁膜の層間クラックを防ぐ。

【解決手段】スクライブライン領域202において、ダイシング工程においてダイシングブレードが通るブレード領域204およびブレード領域204の両側に形成され、ダイシングブレードが通らない非ブレード領域206にそれぞれダミー配線が形成され、非ブレード領域206においては上下に隣接するダミー配線106bとダミー配線110bとがダミービア108bで接続され、ブレード領域204においては、上下に隣接するダミー配線106aとダミー配線110aとがダミービアで接続されていない。

(もっと読む)

半導体装置およびその製造方法

【課題】グラフェンのバリスティック伝導性を利用した低抵抗配線を備え、配線と配線接続部材の接続部分の構成の複雑化を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、基板と、基板の上方に設けられ、積層された複数のグラフェンナノリボンシート122からなるグラフェンナノリボン層121を含む下層配線12と、複数のグラフェンナノリボンシート122の少なくとも1枚を貫通し、下層配線12と上層配線13とを接続するビア14およびバリアメタル15と、を有する。

(もっと読む)

電極基板の製造方法、電極基板、及び薄膜トランジスタ

【課題】製造工程の複雑化と製造コストの高価格化を招くことなく、多層電極間の接続を容易に行うことが可能な電極基板の製造方法、電極基板、及び薄膜トランジスタを提供する。

【解決手段】下地層の上に、下層電極、層間絶縁膜、上層電極がこの順番で積層され、下層電極と上層電極とが層間絶縁膜に形成された開口部を介して電気的に接続された電極基板の製造方法であって、下地層の上に、電極材料を含有する溶液を塗布した後、乾燥させて下層電極を形成する工程と、下層電極が形成された下地層の上に、開口部を有する層間絶縁膜を形成する工程と、開口部に溶液の溶媒を滴下し、開口部に位置する下層電極を溶解した後、乾燥させることにより、電極材料を開口部の内壁に沿ってコーヒーステイン形状に形成する工程と、電極材料が開口部の内壁に沿ってコーヒーステイン形状に形成された層間絶縁膜の上に上層電極を形成する工程と、を有する。

(もっと読む)

3次元半導体装置および3次元半導体装置の冷却方法

【課題】回路設計に対する制限を低減するか解消し3次元回路内のホットスポットを効率的に冷却する3次元半導体装置。

【解決手段】 チップを貫通する貫通電極を有する複数の半導体チップ1を積層してなる3次元半導体装置であって、前記貫通電極として、異種の第1、第2の材料で構成された第1、第2の貫通電極(4、5)を備え、前記第1、第2の貫通電極とそれぞれ電気的に接続され、前記第1、第2の貫通電極とそれぞれ同種の材料からなり、チップの回路面上に配置され、前記回路面上で接続された第1、第2の表面配線を有し、前記第1の貫通電極、前記第1の表面配線、前記第2の表面配線、前記第2の貫通電極に沿って電流を流すことにより、前記回路面上の前記第1の表面配線と前記第2の表面配線との接合部(2)でペルチェ吸熱が行われる。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】バンプを介した接合部分の強度を確保可能とすることで高い信頼性を備える半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板10に形成された電極パッド12と、電極パッド12の位置に形成されたパッド開口を備える保護層を構成するパッシベーション膜13及び緩衝層14と、パッド開口に形成され、電極パッド12に電気的に接続されたバンプ21と、バンプ21との間に間隔が設けられ、金属層である通電層16を介して保護層上に形成された樹脂層18と、を有し、樹脂層18は、接着性樹脂材料を用いて構成される。

(もっと読む)

基板の処理方法及び基板の処理装置

【課題】 層間絶縁膜にLow−k材を使用した基板であっても、層間絶縁膜の経時劣化や変質の可能性を低くできる基板の処理方法を提供すること。

【解決手段】 シリコン酸化膜よりも低い誘電率の誘電体層を含む基板を処理する基板の処理方法であって、不活性ガスの雰囲気中で、前記誘電体層を脱水縮合処理するために加熱する脱水工程と、少なくとも水素原子を含むガスの雰囲気中で、前記基板をアニールする工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】下層金属膜上の絶縁性保護膜に貫通部を形成した後の残渣処理を簡単かつ確実に行い、下層金属膜の露出面を良好な状態に維持することによって上層金属膜の形成を確実に行うこと。

【解決手段】ウェハ表面の下層金属膜上に絶縁性保護膜を形成する。その絶縁性保護膜上にマスクを形成し、このマスクを用いて絶縁性保護膜を選択的に除去して下層金属膜の一部を露出させる。薬液によるウェット処理を行ってマスクを除去する。その後、その露出した下層金属膜の表面に存在する残渣を酸素系プラズマ処理により除去する。酸素系プラズマ処理によって下層金属膜の露出面にできたダメージを、水素系プラズマ処理を行って取り除く。そして、下層金属膜の露出面上に上層金属膜をメッキ等により積層する。

(もっと読む)

半導体装置及びその製造方法

【課題】実用上十分なエレクトロマイグレーション耐性及び動作速度を有する半導体装置を得られるようにする。

【解決手段】半導体基板1の上に第1の絶縁膜2を形成し、第1の絶縁膜2に配線溝3を形成し、配線溝3の内部に金属膜5を埋め込んで第1の配線6を形成し、第1の絶縁膜2及び第1の配線6の上に保護膜7を形成し、第1の配線6と保護膜7との界面に反応層8を形成する。

(もっと読む)

半導体装置の製造方法

【目的】キャップ成膜時に起因するlow−k膜の絶縁性劣化を低減する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜上に絶縁材料を用いたキャップ膜を形成する工程(S106)と、前記キャップ膜を形成した後に、前記キャップ膜を介して前記前記キャップ膜の下層のシリル化処理を行なう工程(S108)と、前記シリル化処理の後、エッチング法を用いて、前記キャップ膜上から前記絶縁膜内へと続く開口部を形成する工程(S114)と、前記開口部に導電性材料を堆積させる工程(S124)と、を備えたことを特徴とする。

(もっと読む)

電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器

【課題】絶縁層へのコンタクトホール形成時における、導電層の浸食や破損の抑制された電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器を提供する。

【解決手段】導電層形成工程によって形成されたソース電極20A、ドレイン電極20B、及び画素電極20Cを含む導電層20上に、該導電層20及び酸化物半導体層18を覆うように、無機材料を主成分とする無機絶縁層23を形成する。そして、この無機絶縁層23上にフォトレジスト膜30を形成してパターン状に露光した後に、現像工程において、現像液を用いて現像することでレジストパターン30B’を形成する。現像工程では、この現像液をエッチング液として用いて、無機絶縁層23の内のレジストパターン30B’から露出した領域を除去することによって導電層20の一部を露出させて、無機絶縁層22にコンタクトホール27を形成する。

(もっと読む)

自己整合ローカル・インターコネクト・プロセスにおけるゲートへの選択的なローカル・インターコネクト

【解決手段】

半導体デバイス生産プロセスは、ハードマスク(112)を用いて半導体基板上にトランジスタのゲート(102)を形成することを含む。ハードマスクは、ゲート上の1つ以上の選択された領域で選択的に除去される。選択された領域でのハードマスクの除去によって、実質的にトランジスタ上にある少なくとも1つの絶縁層を通してゲートが上部金属層に接続できる。導電性材料が、少なくとも1つの絶縁層を通して形成された1つ以上のトレンチ内に堆積される。導電性材料は、少なくとも1つの選択された領域内でゲートへのローカル・インターコネクトを形成する。

(もっと読む)

21 - 40 / 143

[ Back to top ]