Fターム[5F033KK00]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020)

Fターム[5F033KK00]の下位に属するFターム

半導体基板 (2,232)

半導体(基板を除く) (1,188)

金属及びその合金(シリサイドを除く) (9,842)

シリサイド (1,324)

化合物 (2,201)

透光性導電膜材料 (79)

超伝導材料 (11)

Fターム[5F033KK00]に分類される特許

61 - 80 / 143

半導体装置および半導体装置の製造方法

【課題】内層配線が薄くても内層配線とビアとの間の優れた電気伝導性を得ることができる半導体装置およびその製造方法を提供する。

【解決手段】第1層と第2層との間に介在した所定の厚みの第1金属層と、前記第2層の表層に配置された第2金属層と、前記第1金属層、前記第1層及び前記第2層を貫通するビアホールと該ビアホールに形成された導電性組成物とからなるビアと、を具備し、前記ビアホールの外周に沿った第1金属層の端部は前記ビアホールの側面に接するように折れ曲がった形状であり、前記第1金属層の折れ曲がった表面で前記導電性組成物に導通している半導体装置である。

(もっと読む)

半導体デバイスの製造方法およびビア不良率予測システム

【課題】半導体デバイスのビアの不良率を高精度に予測するモデル、ならびにこの不良率予測モデルに基づく不良率予測工程を有する半導体デバイスの製造方法および不良率予測システムを提供する。

【解決手段】ビア不良率予測工程を有する半導体デバイスの製造方法であって、前記ビア不良率予測工程は、複数のビアチェーンTEGの不良率を計測するステップS101と、前記ビアチェーンTEGのビア間距離と前記不良率との関係に基づいてビア不良率予測モデル関数を算出するステップS102と、前記半導体デバイスの実際のレイアウトにおいて、各ビアについて最短隣接ビアを決定し、前記各ビアと前記各ビアに対応する前記最短隣接ビアとの間の最短隣接距離を算出するステップS110と、前記ビア不良率予測モデル関数と前記最短隣接距離とに基づいて前記各ビアの不良率を予測するステップS115とを有する。

(もっと読む)

レジスト下層膜形成用組成物及びそれを用いたデュアルダマシン構造の形成方法

【課題】ビアもしくはトレンチへの埋め込みに好適であり、所望のパターンに基づいた形成が容易であり、エッチング耐性に優れるレジスト下層膜を与えるレジスト下層膜形成用組成物及びこの組成物を用いたデュアルダマシン構造の形成方法を提供する。

【解決手段】本レジスト下層膜形成用組成物は、(A)アリール基を有する重合体、(B)アセチレン基を有する界面活性剤、及び、(C)溶剤を含有する。更に、(D)酸発生剤、(E)架橋剤等を含有することができる。

(もっと読む)

コンタクトホールの形成方法、パターン形成方法、及び電気光学装置の製造方法

【課題】エッチング時におけるホール径が小さく、アスペクト比が高い場合においても、テーパ角を良好にコントロール可能なコンタクトホールの形成方法、パターン形成方法、及び電気光学装置の製造方法を提供する。

【解決手段】基材1上に形成された膜2上に金属膜3を形成する。そして、金属膜3上にレジストマスク4を形成する。このレジストマスク4を用い、金属膜3をドライエッチングするとともに、ドライエッチングによるレジストマスク4の後退量を制御して、開口側面5aが膜に対して第1の傾斜角度を有する金属マスク5を形成する。第1の傾斜角度を有する金属マスク5を用いて膜をドライエッチングすることで、基材1の表面に形成された導電部6を露出させるとともに、開口側面5aが導電部6に対して第1の傾斜角度に応じた第2の傾斜角度を有する孔を形成する。そして、金属マスク5を除去するコンタクトホールの形成方法である。

(もっと読む)

半導体装置のマスク層および二重ダマシーン相互接続構造

【課題】トレンチがミスアライメントされていても、バイアの寸法が低減されない相互接続構造を形成する方法を提供する。

【解決手段】4つのマスク・フィルムを有するマスク層が、半導体装置の相互接続構造の製造で使用される。第1のマスク・フィルムおよび第3のマスク・フィルムは、実質的に等しいエッチング速度を有する。第2のマスク・フィルムおよび第4のマスク・フィルムは、実質的に等しいエッチング速度のフィルムを有し、このエッチング速度は、第1および第3のマスク・フィルムのエッチング速度とは異なる。バイアが、第1のマスク・フィルムにエッチングされる。その後、トレンチが、マスク層の第3のマスク・フィルムにエッチングされる。バイアおよびトレンチは、その後、誘電体材料にエッチングされる。第2、第3および第4のマスク・フィルムは取り除かれ、第1のマスク・フィルムは、誘電体材料のためのパッシベーション層として残る。導電金属が、バイアおよびトレンチに堆積される。

(もっと読む)

半導体記憶装置

【課題】配線コンタクトの配置領域を削減し、チップ面積を縮小する。

【解決手段】半導体基板と、前記半導体基板上に形成されて、複数の第1の配線、これら複数の第1の配線と交差する複数の第2の配線、並びに前記第1及び第2の配線の交差部で両配線間に接続されたメモリセルを有するセルアレイからなるセルアレイ層を複数積層したメモリブロックと、前記各セルアレイの前記第1の配線と前記半導体基板とをそれぞれ接続する、前記セルアレイ層の積層方向に延びる複数の配線コンタクトとを備え、所定の前記セルアレイ層は、これよりも前記半導体基板に近い下層の前記セルアレイ層よりも、前記第1の配線の分割数及び接続される配線コンタクト数が少ない。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、電気的接続について信頼性を向上させることを目的とする。

【解決手段】集積回路12及び集積回路12に電気的に接続された電極14を有する半導体基板10に、熱硬化性樹脂前駆体24を設ける。電極14上から、熱硬化性樹脂前駆体24の表面に至るように、配線20を形成する。熱硬化性樹脂前駆体24を、熱によって硬化収縮させて表面積を小さくし、配線20に凸部22となるしわを形成する。

(もっと読む)

半導体集積回路装置

【課題】良好に接続できるようにする。

【解決手段】層間絶縁膜22,29に形成された1つのコンタクトホール51、53につき複数のボトムゲートライン41の配線端子がそのコンタクトホール51,53内にあり、1つのボトムゲートライン41につき1つの中継パッド52,54が被覆し、1つのコンタクトホール56につき1つの中継パッド54がそのコンタクトホール56内にあり、1つの中継パッド54につき1つの表面パッド56がコンタクトホール56内で接している。

(もっと読む)

薄膜の形成方法、プラズマ成膜装置及び記憶媒体

【課題】被処理体の表面の凹部の開口部近傍にオーバハング部が形成されることを防止し、この結果、ピンチオフやボイドを発生させることなく凹部内を埋め込むことが可能な薄膜の形成方法を提供する。

【解決手段】高融点金属よりなる金属ターゲット96をスパッタしつつ発生した金属粒子をプラズマでイオン化し、載置台60上に載置された表面に凹部を有する被処理体2の表面に前記イオン化された金属粒子をバイアス電力により引き込んで高融点金属を含む薄膜を堆積する成膜工程を有する薄膜の形成方法において、被処理体を、堆積されつつある薄膜がフローを生ずるようなフロー温度に加熱した状態に維持するようにする。これにより、表面拡散を生ぜしめて被処理体の表面の凹部の開口部近傍にオーバハング部が形成されることを防止する。

(もっと読む)

コンタクトを一体化した集積回路システム

集積回路システム(1000)を形成するための方法は、集積回路デバイス(104)を提供するステップと、前記集積回路デバイス(104)の上に一体化コンタクト(102)を形成するステップと、を有し、該一体化コンタクト(102)を形成するステップは、前記集積回路デバイス(104)の上にビア(112)を提供するステップと、前記ビア(112)内に選択的金属(114)を形成するステップと、前記選択的金属(114)の上に少なくとも1のナノチューブ(116)を形成するステップと、前記ナノチューブ(116)の上にキャップ(118)を形成するステップと、を有する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】所望のエッチングレートでシリコンリッチ膜をエッチングすることが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板10上に、トンネル絶縁膜14、電荷蓄積層16、トップ絶縁膜18からなるONO膜20が形成されている半導体装置の製造方法は、ワードライン22上に、層間絶縁膜24、紫外線吸収膜26、反射防止膜28、キャップ層30を形成する工程と、シリコンリッチ膜である紫外線吸収膜26の紫外線に対する消衰係数を測定する工程と、消衰係数に対応した酸素ガス流量を用いたエッチング条件により、シリコンリッチ膜である紫外線吸収膜26をエッチングする工程と、を有する。

(もっと読む)

半導体装置

【課題】非接触の検査に関して、検査時に必要なインダクタと、ボンディング時に必要なボンディングパッドの両方が、各端子に必要であり、従来のボンディングパッドだけで十分であった場合と比較して、チップ面積の増大を招いてしまう。

【解決手段】半導体装置100は、半導体基板2と、半導体基板2上に設けられたインダクタ4と、インダクタ4上に、インタクタ4と接触するように設けられた金属ボール8と、金属ボール8に電気的に接続されたボンディングワイヤ10を含み、インダクタ4と、金属ボール8とを介して、外部との信号のやりとりを行なう。インダクタ4が、ボンディングパッドの機能を兼ねているので、インダクタとボンディングパッドを対にして配置する必要がない。

(もっと読む)

低誘電率の絶縁膜の成膜方法及び低誘電率の絶縁膜

【課題】良質な低誘電率の絶縁膜を成膜することができる方法を提供する。

【解決手段】先ず、Si、N、C、O及びHの少なくとも1つ以上の元素からなる中空構造体群を絶縁膜形成材料である溶液に分散させて得た塗布液Rを基板上に塗布して塗布膜4を形成する。続いて前記基板を加熱して前記塗布膜をベーキングすることにより、多孔質の低誘電率の絶縁膜を得る。この方法では、元々空隙を有する材料を絶縁膜形成材料である溶液に分散させているので低密度化を図ることができ、低誘電率の絶縁膜が得られる。また当該絶縁膜は、化学結合を有する殻を持つ空隙でポアが形成されているため、膜の機械的強度が高い。

(もっと読む)

半導体装置

【課題】正常な切断を実現できるレーザー光照射条件範囲を、従来のヒューズ層に比べて拡大することができるヒューズ層を有する半導体装置を提供する。

【解決手段】層間絶縁膜3上に平行に配置された複数のヒューズ層5と、互いに隣接するヒューズ層5の間に、ヒューズ層5と平行に設けられたダミーヒューズ層15とを備える。ヒューズ層5を切断するためのレーザー光照射の際、ダミーヒューズ層15が横方向へ拡散する熱エネルギーを吸収するため、隣り合うヒューズ層5へのダメージを抑制することができる。また、ヒューズ層5が密集して配置された状況下であっても、レーザー光のエネルギーやビーム径を大きくすることが可能となるため、ヒューズ層を安定して切断することが可能になる。

(もっと読む)

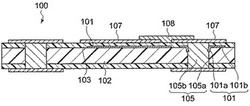

貫通配線基板及びその製造方法

【課題】貫通配線基板を他基板に実装する際には圧力と熱が掛かる場合でも、貫通配線基板及び被実装物の耐久性を向上せしめた貫通配線基板及びその製造方法を提供する。

【解決手段】基板に設けられた貫通孔に貫通配線を備える貫通配線基板において、基板部材7に設けられた貫通孔3と、基板部材7の貫通孔3を除く両面および貫通孔3の内周面に形成された絶縁層9と、少なくとも前記貫通配線基板の一方の面において、基板部材7の貫通孔3を除く部分の絶縁層9上に形成される絶縁樹脂層14と、貫通孔3内周面の絶縁層9上に設けられたバリアメタルシード層12と、貫通孔3に充填されると共に、貫通孔3から所定距離離れた位置まで前記貫通配線基板の一方の面上の絶縁樹脂層14上に伸延して形成される貫通伸延配線13と、貫通孔3の位置を除く貫通伸延配線13上に形成された導電性を有するバンプ15と、を具備している。

(もっと読む)

積層配線構造体及びその製造方法並びに半導体装置及びその製造方法

【課題】積層した導電体層を駆動回路などに接続する部分の製造効率を向上し、且つ信頼性を向上させること。

【解決手段】本発明の積層配線構造体は、導電体層と絶縁層とが交互に積層された積層部と、最上層の絶縁層から形成され導電体層それぞれに達し、側面が導電体層と絶縁膜を介して形成された複数のコンタクトと、を有している。また、コンタクトのうち少なくとも1つは、導電体層で区切られた複数の部分を有し、

上層の導電体層に区切られるコンタクトの内径より、下層の導電体層に接続されるコンタクトの開口部の内径が小さいことを特徴とすることもできる。

(もっと読む)

低誘電率の誘電性材料の表面調整

誘電性領域および導電性領域を含む、パターン化半導体基板表面を提供することと、両親媒性表面調整剤を誘電性領域に塗布し、誘電性領域を調整することと、を含む、パターン化半導体基板を調整する方法が提示される。いくつかの実施形態では、誘電性領域を調整することは、誘電性領域のぬれ角を調整することを含む。いくつかの実施形態では、ぬれ角を調整することは、誘電性領域の表面を親水性にすることを含む。いくつかの実施形態では、方法は、水溶液をパターン化半導体基板表面に塗布することをさらに含む。いくつかの実施形態では、導電性領域は、水溶液によって、選択的に増強される。いくつかの実施形態では、方法は、低誘電率材料から形成される誘電性領域を提供することをさらに含む。いくつかの実施形態では、両親媒性表面調整剤を塗布することは、低誘電率領域の後続プロセスとの相互作用を調整する。  (もっと読む)

(もっと読む)

半導体装置

【課題】基板上にCMISFETを備えた半導体装置において、Global Strainによる応力印加を有効に活用しつつ、回路のスイッチ動作速度の低下を生じさせない半導体装置を提供する。

【解決手段】基板の一方の面に形成される第1の素子領域と、基板の他方の面に形成される第2の素子領域と、第1の素子領域と第2の素子領域との間の、比誘電率が3.9よりも低い絶縁層とを備え、第1の素子領域にn型MISFETが形成され、第2の素子領域にp型MISFETが形成され、絶縁層中を貫通する配線によって、第1の素子領域と第2の素子領域とが電気的に接続され、第1の素子領域が形成される面が凸形状、第2の素子領域が形成される面が凹形状となるように基板が湾曲していることを特徴とする半導体装置。

(もっと読む)

自己整合ウェハまたはチップ構造、自己整合積層構造およびそれを製造する方法

【課題】基板、少なくとも1つの第1のくぼんだ基部、少なくとも1つの第2のくぼんだ基部、少なくとも1つの接続構造および少なくとも1つのバンプを備える自己整合ウェハまたはチップ構造を提供する。

【解決手段】基板100は第1の表面101aおよび第2の表面101bを有し、少なくとも1つのパッド102は第1の表面101a上に形成されている。第1のくぼんだ基部116は、第1の表面101a上に配置されるとともに、パッド102に電気的に接続されている。第2のくぼんだ基部120は第2の表面101b上に配置されている。接続構造は、第1および第2のくぼんだ基部116、120に電気的に接続するために、基板100を貫通するとともに、第1および第2のくぼんだ基部116、120間に配置されている。バンプ122は、第2のくぼんだ基部120に充填され、第2の表面101bから突出する。

(もっと読む)

ポリマー薄膜における自己整合ビアホールの形成

【課題】低コストで効率的なプロセスで、トップ導体とボトム導体との間に電気的接続をもたらす誘電ポリマー薄膜における自己整合ビアを形成する方法の提供。

【解決手段】このプロセスは、第1のパターン化された導電層上に導電ポスト205を印刷し、次にパターン化されていない誘電層207を堆積させ、次に第2のパターン化された導電層を堆積させることによりなし得る。ビア208は、誘電体を堆積した後、第2の導電層を堆積する前に、ポストをフラッシュアニールする間に形成される。このプロセスでは、ポスト材料は閃光によってアニールされ、その結果、ポスト上部の誘電体を除去するエネルギーが放出される。

(もっと読む)

61 - 80 / 143

[ Back to top ]