Fターム[5F033KK01]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 半導体基板 (2,232)

Fターム[5F033KK01]に分類される特許

161 - 180 / 2,232

半導体装置の製造方法、半導体装置

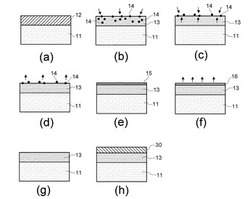

【課題】Niシリサイドを用いてSiC上で信頼性の高い低抵抗の電極を低コストで得る。

【解決手段】n型SiC層11上にNi層12が形成される(図1(a))。熱処理を行うことによってNi層12のNiとn型SiC層11のSiとを反応させ、Niシリサイド層13を形成させる(図1(b))。この状態で酸化雰囲気中で熱処理を行う(図1(d))。還元雰囲気中で例えば300〜400℃で熱処理を行う(図1(f):還元処理工程)。これにより、酸化層15は還元され、Ni等で構成された還元層16となる。この還元層16は、ウェットエッチングで除去することができる(図1(g):エッチング工程)。その後、Niシリサイド層13の上に配線層となるTi/Al層30を形成する(図1(h))。

(もっと読む)

光電変換装置、撮像システム及びその製造方法

【課題】 フローティングディフュージョン部の容量の増大を抑制することが可能な光電変換装置を提供する。

【解決手段】 光電変換素子と、フローティングディフュージョン部と、転送トランジスタと、増幅トランジスタとが配された半導体基板と、第1の配線層と、第2の配線層とを含む複数の配線層と、を有する光電変換装置において、転送トランジスタのゲート電極と、前記第2の配線層とがスタックコンタクト構造で接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置を構成する配線の信頼性向上を図る。

【解決手段】テトラメチルシランガスの流量を通常条件よりも下げて形成したSiCN膜SCN1(4MS↓)と、このSiCN膜SCN1(4MS↓)上に形成され、通常のテトラメチルシランガスの流量で形成したSiCN膜SCN2と、このSiCN膜SCN2上に形成されたSiCO膜SCOからバリア絶縁膜を構成する。これにより、耐透水性の向上と低誘電率化をバランス良く実現することができる。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】小型化を実現し得る半導体装置を提供することにある。

【解決手段】半導体基板に形成され、素子分離領域により画定された第1の素子領域12bと、第1の素子領域上に形成された第1のゲート電極21bと、第1のゲート電極の第1の側における第1の素子領域に形成された第1のソース領域32Sと、第1のゲート電極の第2の側における第1の素子領域に形成された第1のドレイン領域32Dとを有する第1のトランジスタ36と、第1のゲート電極の第1の側における素子分離領域上に、第1のゲート電極と並行するように形成された第1のパターン38aと、第1のソース領域に接続された第1の導体プラグ44cとを有し、第1の導体プラグは、接地線及び電源線のうちの一方に電気的に接続されており、第1のパターンは、接地線及び電源線のうちの他方に電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い歩留りで製造し得る半導体装置の製造方法を提供する。

【解決手段】ゲート配線16aを形成するのと同時に形成された位置合わせマーク16fに対して位置合わせして、コンタクトホールの第1の部分パターン61a1をゲート配線の一部と重なり合うようにフォトレジスト膜に露光する工程と、活性領域11bを形成するのと同時に形成された位置合わせマーク11fに対して位置合わせして、コンタクトホールの第2の部分パターン61a2を活性領域の一部と重なり合うようにフォトレジスト膜に露光する工程と、フォトレジスト膜を現像し、第1の部分パターンと第2の部分パターンとが露光された箇所に開口部を形成する工程と、フォトレジスト膜をマスクとして絶縁膜をエッチングし、ゲート配線とソース/ドレイン拡散層20とに達するコンタクトホールを形成する工程とを有している。

(もっと読む)

連結導体及びこれを用いた半導体装置

【課題】トレンチゲートを有する半導体装置に関して、ゲートの取り出し抵抗の低減を図り、動作速度の高速化をはかる。

【解決手段】この半導体装置は、リードフレーム30のリード端子30Rの一端に連結導体15を介して電気的に接続されている。この連結導体は、Cu箔で構成され、本体部15Mと、リード端子30Rに当接し、リード端子30Rに接続されるリード接続部15Rと、トレンチMOSFET(チップ)のソースパッドに当接するフィンガー部15Fと、フィンガー部15Fの先端を空間部で一体化する連結部15Bとで構成されている。この連結導体を用いることで、第1の外部取り出し電極を構成するソース電極35s間に第2の外部取り出し電極としてのゲートパッド35gが伸張して形成されている場合にも、低抵抗で信頼性の高い実装が実現される。

(もっと読む)

半導体装置

【課題】高い耐電圧特性、および耐リーク特性を有する配線構造を備える半導体装置、およびその製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置は、半導体素子が設けられた半導体基板と、前記半導体基板上に形成された、上下層の導電部材を電気的に接続する接続部材と、前記接続部材と同じ層に形成された第1の絶縁膜と、前記接続部材の上面の一部と接する第1の領域、および前記第1の領域上に位置し、前記第1の領域よりも幅の広い第2の領域を含む配線と、前記第1の絶縁膜上に、前記配線の前記第1の領域の側面の上側から少なくとも一部、および前記第2の領域の底面に接して形成された第2の絶縁膜と、を有する。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法

【課題】ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法を提供する。

【解決手段】特に分子の特性評価に適用される本発明によると、以下を備える素子が作られる:ナノ物体(2)に接続される上部接触パッド(8)を備えた上部層(16);外部電気システム(4)に接続される下部接触パッド(12)を備えた下部層(18);前記下部層上にあり、前記下部パッドと接触する電気的貫通ビア(22)を備えた接着層(20);前記接着層と前記上部層の間にあり、前記上部パッドを前記下部パッドに接続するための導電ライン(25)及び電気的ビア(26)を備えた少なくとも2つの層(22、24)。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コンタクトとアクティブエリアとの間のショートマージンを確保できる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板の上層部分に形成され、前記上層部分を第1方向に延びる複数本のアクティブエリアに区画する複数本の素子分離絶縁体と、前記アクティブエリアに接続されたコンタクトと、を備える。そして、各前記アクティブエリアの上面のうち、前記第1方向における一部の領域には、前記第1方向に対して直交する第2方向において前記アクティブエリアの全体にわたって凹部が形成されている。前記第1方向において、隣り合う前記アクティブエリアにそれぞれ接続された2本の前記コンタクトの位置は相互に異なる。前記コンタクトは前記凹部の側面に接し、底面には接していない。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

半導体集積回路装置用バリア材の探索方法及び当該探索方法によって探索される半導体集積回路装置用バリア材

【課題】従来のルテニウムバリア材と同様に優れた銅拡散の抑制効果を有し、供給性の点で問題がなく、比較的低コストの金属又はその金属を含む金属間化合物からなる新規な半導体集積回路装置用バリア材の探索方法及び当該探索方法によって探索される半導体集積回路用バリア材を提供する。

【解決する手段】バリア膜若しくはバリア膜とシード膜からなる複合膜の上に銅配線層を有する半導体集積回路装置の前記バリア膜を構成するバリア材として、単位結晶格子の最近接原子間距離(DM)がルテニウムの単位結晶格子の最近接原子間距離(DRu)に近い領域、具体的には、オングストローム(Å)単位で−0.200Å<(DM―DRu)<0.12Åの関係にあって、かつ融点若しくは変態点が650ケルビン(K)以上である金属又は金属間化合物を選択することを特徴とする。

(もっと読む)

半導体素子及びその製造方法

【課題】絶縁膜を貫通するコンタクトプラグの抵抗を改善させられる半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグと、前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】 簡単な工程で半導体装置を製造することが可能となる。

【解決手段】 半導体基板101の撮像領域103及び周辺領域104の上に第5層間絶縁膜113eが配される。第5層間絶縁膜113eの光電変換部105と重なった位置に開口116が形成される。半導体基板101の撮像領域103及び周辺領域104に第1導波路部材118を形成する。第1導波路部材118の周辺領域104に配された部分を除去し、第5層間絶縁膜113eを露出させる。

(もっと読む)

半導体装置の製造方法

【課題】レジストの膜減りによって残すべき配線がエッチングされることを防止すると共に、露光機による配線パターニング時のフォーカスずれを抑制し、配線の線幅にバラツキが生じることを防止する。

【解決手段】スクライブライン内において、スクライブラインの両側では層間絶縁膜2、4、6が存在せず半導体基板1の表面が露出する領域を設け、スクライブラインの中央位置、つまり溝Tの間に挟まれた領域には層間絶縁膜2、4、6を残す。これにより、スクライブラインとチップとの境界位置近傍において、第3配線層7を形成する際のマスクとして用いるレジスト21が膜減りすることを抑制できる。したがって、レジスト21の膜減りによって残すべき配線がエッチングされることを防止できると共に、露光機による第3配線層7のパターニング時のフォーカスずれを抑制でき、第3配線層7の線幅にバラツキが生じることを防止することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、異なる膜特性を有する絶縁膜に形成されるコンタクト形状の制御性を向上させる。

【解決手段】半導体基板に素子領域を形成し、半導体基板の第1の領域上に、第1の絶縁膜を形成し、半導体基板の第2の領域上に、膜応力及びコンタクトの形成の際のエッチング加工時のエッチングレートが、第1の絶縁膜と異なる第2の絶縁膜を形成し、少なくとも第2の絶縁膜において、コンタクトが形成されるコンタクト領域に選択的にUV光を照射し、UV光を照射した後、第1の絶縁膜及び前記第2の絶縁膜をエッチングして前記コンタクトを形成する。

(もっと読む)

161 - 180 / 2,232

[ Back to top ]