Fターム[5F033KK32]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201) | 窒化物 (1,946)

Fターム[5F033KK32]の下位に属するFターム

Fターム[5F033KK32]に分類される特許

361 - 380 / 801

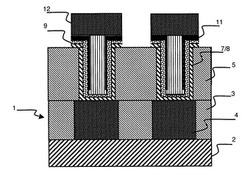

カーボンナノチューブベースの電気的接続の製造方法

【課題】デュアルダマシン構造にも適用出来る好ましくはカーボンで作られるナノチューブによるビアの形成法を提供する。

【解決手段】底部と、側壁とを備える、少なくとも1つのビアを、金属材料の2つの層4及び12を隔てる絶縁材料層5の中に形成する。次いで接着層7及び/又は保護層8の上に触媒層9を堆積する。さらに抑止層11を、前記ビアの前記底部における前記触媒層9の部分を除く、前記ビアの前記ビアの側壁の上と、前記絶縁材料層5の上に方向性堆積によって形成する。ナノチューブを前記抑止層11のない前記ビア底部の前記触媒層9の部分から成長させて前記金属材料の2つの層4及び12を電気的に接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生容量が低く、かつ、熱処理による抵抗値の変動が小さい抵抗素子を有する半導体装置を得ることのできる技術を提供する。

【解決手段】スパッタリングターゲット材料としてタンタルを用い、スパッタリングガスとしてアルゴンと窒素との混合ガスを用いた反応性直流スパッタリング法により、窒化タンタル膜からなる厚さ20nm、窒素濃度30原子%未満の第1抵抗層5a、及び窒化タンタル膜からなる厚さ5nm、窒素濃度30原子%以上の第2抵抗層5bを順次形成した後、第1及び第2抵抗層5a,5bを加工して抵抗素子R1を形成する。窒素濃度が30原子%以上の上部領域を設けることにより、配線工程において熱負荷が与えられても抵抗素子R1の抵抗変動率を1%未満に抑えることができる。

(もっと読む)

半導体装置

【目的】多層配線において配線層間の剥がれ耐性を向上させた装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、基板200上に多層配線構造で形成され、最上層に電極パッド30を有する実効配線10と、多層配線構造内で実効配線10の周囲を取り囲むように形成されたビアリング20と、多層配線構造の最終表面を保護する積層保護膜PFと、積層保護膜PFと接する位置であって実効配線10が形成される領域とチップ領域端との間に形成された、電極パッド30を構成する導体とビアリング20を構成する導体とのいずれよりもヤング率が大きい膜パターンで構成されるクラックストッパ膜40と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】記憶情報のセキュリティ性の高い半導体装置を製造工程数の増加を抑えて製造することのできる技術を提供する。

【解決手段】半導体基板10の主面に細い配線M1aと太い配線M1bとを形成した後、高密度プラズマCVD法によりこれら配線M1a,M1bを覆う絶縁膜26を堆積し、さらに遮光膜27および下層絶縁膜28aを順次堆積する。続いて下層絶縁膜28aの表面をCMP法により研磨して太い配線M1bの上の遮光膜27を露出させ、さらに太い配線M1bの上の遮光膜27を研磨して除去した後、上層絶縁膜28bを堆積する。続いて太い配線M1bの上の絶縁膜26および上層絶縁膜28bに、太い配線M1bに達する接続孔29aを形成した後、接続孔29aの内部にプラグ31を埋め込む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】配線間の容量が低く、歩留りや信頼性が高い半導体装置を提供する。

【解決手段】ギャップ110の形成によりキャップ膜108厚が薄くなったまたは消失したとしても、ギャップ110を形成した後に、下層配線107上にキャップ膜111を選択的に成長させることにより、キャップ膜の厚さを確保することができるため、配線間の容量を十分に低減でき、かつ、歩留りや信頼性を高く維持することができる。

(もっと読む)

半導体装置

【課題】応力耐性のより高いシールリング構造を有する半導体装置を提供する。

【解決手段】複数の半導体素子を含む半導体層と、半導体層の上に設けられた絶縁膜と、絶縁膜を貫通し且つ半導体素子の全体を囲む筒状体と、を含む半導体装置であり、筒状体は、その周方向において各々が互いに離間し且つ平行な複数の筒状プラグと、筒状プラグの各々と交差する複数の壁部と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線材料を接続孔に埋め込み易く、線膨張係数差に基づく応力の影響を低減できる半導体装置及びその製造方法を提供する。

【解決手段】下部配線と、下部配線上に配置された絶縁膜と、絶縁膜に形成された配線溝に、配線材料を埋め込んで形成された上部配線と、配線溝の底面から下部配線まで延設して絶縁膜に形成された接続孔に、配線材料を埋め込んで形成された接続部とを有し、上部配線と接続部が同一の配線材料を用いて一括形成され、下部配線と上部配線とが接続部を介して電気的に接続された半導体装置であって、接続孔の壁面のうち、配線溝の底面に至る上端部が配線溝の底面側ほど拡がったテーパ形状とされ、配線溝の壁面のうち、開口部に至る側面の上端部が開口部側ほど拡がったテーパ形状とされ、側面と底面との角部がテーパ形状とされている。

(もっと読む)

貫通導電体を有する半導体装置およびその製造方法

【課題】 より簡単な方法(プロセス)で且つより低い製造コストで製造できる、貫通導電体を有する半導体装置とその製造方法を提供する。

【解決手段】

SiO2膜(第1絶縁膜)23は、シリコン基板11の貫通孔14の内側面とシリコン基板11の裏面を覆うと共に、表面電極15の裏面に達する透孔31を貫通孔14の内部に持つ。配線膜24は、SiO2膜23上に所定パターンで形成されると共に、貫通孔14の内部で透孔31を介して表面電極15の裏面に接触せしめられている。外部電極25は、配線膜24上に形成されていて、貫通孔14の内部で配線膜24の内側に残存する空隙を充填する充填部25aを持ち、配線膜24の貫通孔14の内部にある部分と充填部25aとが、貫通導電体として機能する。

(もっと読む)

フローティングボディ素子及びバルクボディ素子を有する半導体素子及びその製造方法

【課題】フローティングボディ素子及びバルクボディ素子を有する半導体素子及びその製造方法を提供する。

【解決手段】この半導体素子の製造方法は、バルクボディ素子領域及びフローティングボディ素子領域を有する基板を準備する工程を含む。バルクボディ素子領域の基板の活性領域を画定するとともに、フローティングボディ素子領域のうち第1素子領域の基板上に順に積層された第1犠牲パターン及び第1活性パターンを画定する素子分離膜を形成する。フォトリソグラフィ及びエッチング工程を用いて素子分離膜に第1犠牲パターンの一部分を露出させる第1リセス領域を形成する。第1犠牲パターンを除去して第1活性パターン下部に第1空間を形成する。第1空間の内壁及び第1リセス領域の内壁に第1埋込誘電膜を形成する。第1埋込誘電膜を有する基板上に少なくとも第1空間を埋め込む第1埋込パターンを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜として低誘電率膜のように機械的強度が低い膜を用いた場合であっても配線の集積度が高く且つ信頼性を確保できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上にトランジスタ12等の半導体素子を被覆する第1の層間絶縁膜16を形成した後、ヤング率が低い低誘電率膜からなる下層側層間絶縁膜Aと、シリコン酸化膜等のようにヤング率が高く且つ密着性及び耐湿性が優れた膜からなる上層側層間絶縁膜Bを形成する。電極パッド70の直下域の下層側層間絶縁膜A内にはダミー配線及びダミープラグとともに、半導体素子に電気的に接続された有効配線を配置する。また、電極パッド70の直下域の上層側層間絶縁膜B内にはダミー配線及びダミープラグのみを配置し、電極パッド70に応力が印加されたときに下層側層間絶縁膜Aよりも上層側層間絶縁膜Bに大きな応力が印加されるようにする。

(もっと読む)

NORフラッシュデバイス及びその製造方法

【課題】本発明は、NORフラッシュデバイス及びその製造方法を提供する。

【解決手段】バックエンドオブライン(BEOL)構造を有するNORフラッシュデバイスにおいて、BEOL構造は導電領域を有する基板と、基板上に形成された第1層間絶縁膜と、導電領域に形成される第1金属ラインと、該第1金属ラインと第1層間絶縁膜を覆う第2層間絶縁膜と、第2層間絶縁膜を貫通する第1コンタクト及び第1コンタクトを通じて第1金属ラインと連結される第2金属ラインを具備して、第1コンタクト、第1及び第2金属ラインのうちで少なくとも一つは銅であり、第1及び第2層間絶縁膜のうちで少なくとも一つは、低誘電物質を含む。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に下部金属配線を形成する段階と、下部金属配線を含む半導体基板上に、ダマシンホールを持つ層間絶縁膜を形成する段階と、ダマシンホールの下側部分に露出された下部金属配線及びダマシンホールの側面部分に露出された層間絶縁膜上に拡散防止膜を形成する段階と、不活性気体を用いたプラズマ方式で、ダマシンホールの下側部分の下部金属配線上に形成された拡散防止膜を選択的に除去する段階と、を含む半導体素子の製造方法とした。したがって、ビアに残存する残余物をパンチスルーによって除去し、接触抵抗を下げ、サイドカバレッジ(side coverage)を向上させることによって、上部金属配線のギャップ・フィル特性を改善させ、不良率の改善によって歩留まりを向上させる効果を奏する。

(もっと読む)

半導体装置の製造方法

【課題】ハードマスク除去プロセスにおいて、低誘電率絶縁膜の誘電率の上昇を伴うダメージを低減させると共に加工形状を安定させることを目的とする。

【解決手段】ハードマスクを用いて配線溝を形成するプロセスからなる半導体装置の製造方法において、メタルハードマスク107を用いて配線溝111の形成を行うことで配線溝111の形状を安定化させることができると共に、配線溝111にTaNやCuを形成する前にあらかじめメタルハードマスク107の一部または全てを除去することで低誘電率膜表面の誘電率の上昇を伴う損傷が低減されて配線間のリーク電流を低減させることができ、信頼性の高い半導体装置を実現できる。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】銅膜を酸化させその酸化物を酸もしくはアルカリなどで除去することにより銅膜の表面をエッチングする方法において、エッチング処理を行った後の銅膜表面が荒れてしまうことが少なく、少ない工程で短時間に精度良く行うことができる半導体装置の製造方法及び半導体製造装置を提供する。

【解決手段】半導体基板上の絶縁膜に形成された配線溝又はコンタクト孔に配線金属を堆積して前記配線溝又はコンタクト孔に充填する工程と、前記配線金属を研磨して前記絶縁膜を露出する工程と、前記半導体基板を洗浄する工程と、前記配線溝又はコンタクト孔に埋め込まれた前記配線金属表面をリセスエッチングする工程を有している。前記研磨工程、前記洗浄工程及び前記リセスエッチング工程の少なくとも2工程で用いる薬液の主たる成分が同一である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板に貫通配線層を形成する際の貫通孔底部での配線層の薄膜化が防止され、貫通接続部の接続不良が改善された半導体装置を提供する。

【解決手段】貫通孔3を有する半導体基板2の表面に、該貫通孔3と同径の開口4aを有する第1の絶縁層4が被覆され、その上に第1の配線層5が形成されている。また第1の配線層5の近傍に、貫通孔3とその内壁面等に形成された第3の絶縁層8および貫通孔3内に充填・形成された第3の配線層9から成る貫通接続部が形成されている。そして、この貫通接続部に内接された第2の配線層7と第1の配線層5とが電気的に接続され、貫通孔3の内壁面と第1の配線層5との間に第2の絶縁層6が介在し、第1の配線層5と貫通孔3内に充填・形成された第3の配線層9とが離間されるように構成されている。

(もっと読む)

配線膜の形成方法、トランジスタ、及び電子装置

【課題】ヒロック発生を防止し、密着性とバリア性に優れた配線膜を形成する。

【解決手段】成膜対象物21が配置された真空槽13に酸素又は窒素を含有する添加ガスを導入し、Zr等の添加元素を含む銅ターゲット11をスパッタリングし、アルミニウム膜23の表面にバリア膜24を形成する。バリア膜24は銅を主成分とするため、アルミニウム膜23と同じエッチング液でエッチング可能であり、添加元素と酸素を含むため、アルミニウム膜23にヒロックが発生しない。また、配線膜25の表面にITOを密着させた場合には、アルミニウム膜23は直接ITOに接触しないからコンタクト抵抗も高くならない。

(もっと読む)

半導体装置

【課題】多層配線構造を有する半導体装置において、製造工程を増加させることなく形成される、外部との電気接続信頼性の高い電極パッドを備える半導体装置を提供すること。

【解決手段】 この半導体装置1において、第2配線層4の上には、第3配線層5が形成されている。第3配線層5には、所定パターンのAl配線36(各バリア膜34,35,37を含む)が形成されている。Al配線36は、層間膜38に被覆されている。この層間膜38の上には、表面保護膜39が積層されている。そして、表面保護膜39および層間膜38には、これらの膜を膜厚方向に貫通する、パッド開口40が形成されている。Al配線36は、パッド開口40内に臨む部分が、外部との電気接続のための電極パッドとして露出している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の貫通配線部において、貫通孔底部での絶縁層の被覆性が向上され、電気的絶縁性の低下や接続不良が改善された半導体装置を提供する。

【解決手段】貫通孔3を有する半導体基板2の表面に、該貫通孔3と同径の開口4aを有する第1の絶縁層4が被覆され、その上に第1の配線層5が開口4aを覆い形成されている。また、貫通孔3内および半導体基板2の裏面に第2の絶縁層6が被覆されている。第2の絶縁層6は、第1の配線層5と内接するように形成され、内接部に第1の絶縁層4の開口4aよりも小径の開口6aを有している。さらに、貫通孔3内に第2の配線層7が充填・形成され、この第2の配線層7は第2の絶縁層6の開口6aを介して第1の配線層5に内接している。

(もっと読む)

半導体装置

【課題】 ストレスマイグレーション耐性およびエレクトロマイグレーション耐性に優れ、下部配線と上部配線との接続信頼性の高い半導体装置を提供すること。

【解決手段】 この半導体装置1において、Cuを主成分とするCu配線23とWからなるWプラグ32との間には、積層バリア膜30が介在されている。積層バリア膜30は、Taバリア膜42、TaNバリア膜43、Tiバリア膜44およびTaNバリア膜45が積層されてなる4層構造を有している。そして、Taバリア膜42は、ビアホール28の側面およびCu配線23の上面に被着されている。また、TiNバリア膜45は、積層バリア膜30の最上層をなし、Wプラグ32の表面に接触形成されている。

(もっと読む)

半導体装置

【課題】 Cuの層間絶縁膜中への拡散を防止することができるCu配線を備えた半導体装置を実現する。

【解決手段】 半導体装置1は、半導体基板10の基板面10aの上方に、順番に積層形成された第1配線層33、第2配線層34及び第3配線層35を備えている。第1配線層33は、SOI基板などの半導体基板10の基板面10a上に形成されており、層間絶縁膜12、側面バリアメタル層15、Cu配線18及び上面バリアメタル層19を備えている。Cu配線18の上面部18aは、側面バリアメタル層15と同様の材料により形成された上面バリアメタル層19により覆われている。ここで、上面バリアメタル層19の幅は、上面部18aの幅よりも大きく形成されている。この上面バリアメタル層19により、Cu配線18から上層の層間絶縁膜12へのCuの拡散を防止することができる。

(もっと読む)

361 - 380 / 801

[ Back to top ]