Fターム[5F033KK32]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201) | 窒化物 (1,946)

Fターム[5F033KK32]の下位に属するFターム

Fターム[5F033KK32]に分類される特許

281 - 300 / 801

半導体装置および半導体装置の製造方法

【課題】貫通孔底部にノッチを有する半導体装置のノッチ部に被覆性良好な連続した金属膜を積層するプロセスを提供し、半導体装置の歩留まりと信頼性向上をはかること。

【解決手段】ノッチ部を含む貫通孔にCVD絶縁膜を積層した後に、バリア層およびシード層のメタル層をスパッタ法により形成する。メタル層のスパッタ成膜中に基板バイアス(負電圧)を印加して、アルゴンやクリプトン等の希ガスのプロセスガスイオンを貫通孔内部へ引き込み、既にある程度貫通孔底部に積層したメタル層をスパッタエッチングするか、貫通孔底部にメタル層を積層すると同時にスパッタエッチングしたメタル材料を貫通孔底部周辺のノッチ部分へ飛散させる。飛散したメタル材料はノッチ部分の絶縁膜上に付着し積層する。Ar+イオン等により飛散されたメタルは高いエネルギーを有する為、メタル層がノッチ内部へ強固に付着する。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供すること。

【解決手段】半導体装置1は、半導体基板(図示略)と、半導体基板上に設けられた第一の電気ヒューズ12と、第二の電気ヒューズ13とを備える。第一の電気ヒューズ12は、異なる配線層に形成された第一の上層配線121および第一の下層配線122と、第一の上層配線121および第一の下層配線122を接続するビア123とを有する。第二の電気ヒューズ13は、異なる配線層に形成された第二の上層配線131および第二の下層配線132と、第二の上層配線131および第二の下層配線132を接続するビア133とを有する。半導体装置1は、第一の電気ヒューズ12の前記第一の上層配線121と、第二の電気ヒューズ13の第二の下層配線132とを接続する接続部14を有する。この接続部14は、第一の電気ヒューズ12および第二の電気ヒューズ13を直列に接続する。

(もっと読む)

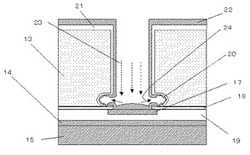

半導体装置及びその製造方法

【課題】 コンタクトプラグの凸形状部の電界集中による絶縁破壊を抑制したViaパターンを有する半導体装置を提供する。

【解決手段】 第一の配線層1及び第一の絶縁層2上に形成された層間絶縁膜3と、層間絶縁膜3内に第一の配線層1との接続部から上方にいくにつれて断面形状が大きくなるように形成された接続孔4と、接続孔4の側壁全面に所定の深さから上方にいくにつれて膜厚が大きくなるように連続的にスペーサ膜5と、スペーサ膜5の内側に第一の配線層1と電気的に接続されるコンタクトプラグ7と、コンタクトプラグ7上に形成され、コンタクトプラグと電気的に接続された第二の配線層8と、第二の絶縁層9とを有する半導体装置。

(もっと読む)

半導体集積回路装置の製造方法

【課題】銅ダマシン関連のバック・エンド領域におけるエッチング装置等の運用に関して、無駄時間が発生していることが明らかとなった。すなわち、たとえば、銅ダマシン配線における層間膜のドライ・エッチング工程においては、5分に1度程度の高頻度でステージ温度の切り替えが発生していることが明らかとなった。これは、ドライ・エッチングのステージ温度等のデータが製造実行システムに登録されていないために、ロット優先度の高いロットが仕掛となるたびに、高頻度でステージ温度の切り替えが発生しているからである。

【解決手段】本願発明は、エッチング・ステージ温度等のように、条件変更に比較的長い準備時間を要する処理条件を製造実行システムに登録しておくことによって、効率のよいウエハ・プロセスの進行管理を実現するものである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】130nm、90nmおよび65nmテクニカル・ノードのプロセス等に適用されるCu-CMP工程においては、Cu配線の腐食を防止する目的で防食剤を添加したスラリが主流となっている。ところが、防食剤を添加したスラリを用いたCu-CMP工程について、本願発明者らが検討したところによると、防食剤はCuと錯体を形成する場合が多く、異物としてウェハ上に多量に残留し歩留の低下や、Cu配線におけるTDDB特性といった信頼度を劣化させる要因となることが明らかとなった。

【解決手段】本願発明は、ポストCMP洗浄において、ウエハのデバイス面をほぼ水平上向きで、当該面に薬液又は純水等の洗浄液体を供給するとともに、ウエハを水平面内で、ほぼその中心の周りで自転させながらウエット洗浄するときに、その自転速度をデバイス面上における洗浄液体の厚さがほぼ均一になる程度に低速にするものである。

(もっと読む)

半導体装置およびその形成方法

【課題】半導体装置の多層配線構造において、下部Cu配線と上部絶縁層との界面に、優れた密着性と耐酸化性と拡散バリア性を有する新規界面層を形成する。

【解決手段】半導体装置の多層配線構造は、半導体ウェハ(1)上に形成した第1の絶縁層(2)と、前記第1の絶縁層上(2)に形成されるCu配線層(4)と、前記Cu配線層上(4)に形成される第2の絶縁層(6)と、前記Cu配線層(4)と前記第2の絶縁層(6)との界面に形成される金属酸化物層(5)と、を備える。金属酸化物層(5)は、Cu配線層(4)上にSnまたはZnなどの金属を浸漬メッキし、その後このメッキ層を酸化性雰囲気中で加熱処理して形成される。

(もっと読む)

不揮発性半導体メモリ

【課題】信頼性の高い不揮発性半導体メモリを提供できる。

【解決手段】本発明の例に関わる不揮発性半導体メモリは、複数のメモリセルが配置されるメモリセルアレイ領域100と、メモリセルアレイ領域100の周囲を取り囲む周辺回路領域と、周辺回路領域とメモリセルアレイ領域100との境界部分であるセルアレイ隣接領域105と、メモリセルアレイ領域100内に層間絶縁膜を介して設けられる複数の第1導電線SLと、セルアレイ隣接領域105内に層間絶縁膜を介して設けられる複数の第2導電線M2とを具備し、複数の第2導電線M2はその配線内にスリット50が形成されていることを備える。

(もっと読む)

電解メッキ液、電解メッキ方法、および半導体装置の製造方法

【課題】銅配線層を電解メッキ法で形成する際に電極となるシード層の溶解に起因する銅メッキ層の欠陥の発生を抑制する電解メッキ液及び該メッキ液を用いた電解メッキ方法を提供する。

【解決手段】電解メッキ液として、極性溶媒と、前記極性溶媒中に溶解した硫酸銅を含み、さらに添加剤として、硫黄化合物よりなるアクセラレータと、前記アクセラレータよりも小さい分子量を有する還元剤とを添加した電解メッキ液を使う。

(もっと読む)

配線用セルフアライン(自己整合)バリア層

集積回路中の銅線を完全に取り囲んでいるケイ酸マンガン層及び窒化ケイ素マンガン層を組み込んだ集積回路用の配線構造、及びその製造方法を提供する。ケイ酸マンガンは、銅が配線から拡散しないためのバリアを形成し、それにより、絶縁体が磁気尚早に損しないよう保護し、トランジスタが銅により劣化しないように保護する。また、ケイ酸マンガン及び窒化ケイ素マンガンは、銅と絶縁体の間の強い接着を促進し、これゆえに製造及び使用の間のデバイスの機械的な完全性が保持される。また、銅−ケイ酸マンガン界面及び窒化ケイ素マンガン界面における強い接着は、デバイスの使用の間の銅のエレクトロマイグレーションによる損傷から保護する。また、マンガン含有シースは、銅がその周囲の酸素又は水により腐食しないよう保護する。 (もっと読む)

半導体装置、半導体装置の製造方法、半導体製造検査装置、および検査装置

【課題】配線幅の変遷に影響されない、表面欠陥を実用可能なレベルよりさらに低いレベルまで低減できる基本的な結晶構造を具備したCu配線を有する半導体装置及びその検査技術を提供する。

【解決手段】半導体装置において、バリア膜及びシード膜を特定すると共に、Cu配線の全ての結晶粒界に占める、粒界Σ値27以下の対応(CSL)粒界の割合(頻度)を60%以上とすることにより、表面欠陥を実用可能な現状レベルの1/10以下まで低減できる。または、該半導体装置において、バリア膜及びシード膜を特定すると共に、Cu配線の全ての結晶粒界に占める、粒界Σ値3の対応(CSL)粒界の割合(頻度)を40%以上とすることにより、表面欠陥低減の同様の効果を得ることができる。

(もっと読む)

配線基板、その製造方法、配線基板を用いた画像表示装置用のパネル、および、該パネルが搭載された画像表示装置

【課題】材料にガラスを用いた基体上にTaN(6方晶)、αTa、銅がこの順形成された溝配線構造の場合、配線と基体との間で十分な密着強度が得られない場合があった。

【解決手段】本発明は、ガラスからなる基体上に銅配線が形成された、配線基板であって、銅配線が、Ta2N膜、αTa膜、および、銅あるいは銅を主成分とする合金からなる膜がこの順に形成された積層構造であることを特徴とする配線基板である。

(もっと読む)

半導体装置

【課題】層間絶縁膜としてLow−k膜を有する半導体装置において、温度サイクル試験時における層間絶縁膜の剥離を防止し、信頼性に優れた半導体装置を提供する。

【解決手段】銅を主導電層とする埋め込み配線5、8、11を内部に形成した層間絶縁膜4、7、10と、埋め込み配線5、8、11のキャップ絶縁膜6、9、12を積層した構造を備えた半導体装置において、相対的にヤング率の小さいLow−k膜からなる層間絶縁膜7と上面で接する相対的にヤング率の大きいキャップ絶縁膜6は、半導体装置の端部において、非設置となるように形成する。

(もっと読む)

半導体デバイスの製造方法

【課題】本発明は、下層配線層を損傷させず、その上部にデュアルダマシン構造の配線要素を形成する半導体デバイスの製造方法を提供することを目的とする。

【解決手段】下層配線上に絶縁物で構成され該下層配線の金属材料の拡散を防止する拡散防止膜を形成し、該拡散防止膜の上部に第1絶縁膜を形成し、該第1絶縁膜の上部にエッチングストッパ膜を形成し、該エッチングストッパ膜の上部に第2絶縁膜を形成し、該下層配線の上部に、該第2絶縁膜、該エッチングストッパ膜、および、該第1絶縁膜を貫通して該拡散防止膜を露出するビアホールを形成し、該ビアホールの内部に、そのビアホールの内壁を覆う有機層を形成し、該第2絶縁膜の所定部位をエッチングにより除去して配線溝を形成し、該配線溝底に露出した該エッチングストッパ膜および該ビアホール底に露出した該拡散防止膜を同時に除去する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間容量を低減する。

【解決手段】半導体装置70には、積層形成される配線膜6及び10から構成される配線層が設けられる。キャップ膜3上に形成される層間絶縁膜4の第1の開口部には、配線膜6が埋設される。配線膜6の底部及び側面部にはバリアメタル膜5が設けられる。層間絶縁膜4及び配線膜6上に形成されるキャップ膜7及び層間絶縁膜8の第2の開口部には、配線膜10が埋設される。配線膜10の底部及び側面部にはバリアメタル膜9が設けられる。層間絶縁膜8及び配線膜10上に形成される。配線膜10は配線膜6上に設けられ、配線膜10の端部は配線層6の端部よりも内側に設けられる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ワイヤボンディングで実装されるチップとバンプ電極で実装されるチップとで、製造工程を共通化できる技術を提供する。

【解決手段】バンプ電極によりチップ1が外部との電気的接続を行う場合においても、ボンディングワイヤによりチップ1が外部との電気的接続を行う場合においても、1本の最上層の配線7にバンプ接続部15およびボンディングパッド16の両方を設ける。バンプ電極を用いる場合にはバンプ接続部15上の絶縁膜に開口部を設け、ボンディングパッド16上は絶縁膜で覆う。一方、ボンディングワイヤを用いる場合にはボンディングパッド16上の絶縁膜に開口部を設け、バンプ接続部15上は絶縁膜で覆う。

(もっと読む)

半導体装置及びその製造方法

【課題】Ru材料をCu配線のバリアメタル膜として使用した際、CMP時にCu溶出の発生しないCu配線形成方法を提供する。

【解決手段】層間絶縁膜上面の第1のバリアメタル上に形成された第2のバリアメタル膜(Ru膜)を除去する工程(d)と、前記工程(d)の後に、前記第1及び第2のバリアメタル膜上にシード銅(Cu)膜を堆積する工程(e)とを有する。このように、シード銅膜を形成する前に、上面の第2のバリアメタル膜を除去してしまうことにより、この第2のバリアメタル膜と銅との電池効果で、銅がスラリー中に溶出することを防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】歩留りが高く且つ配線間容量を十分に低減でき、且つ機械的強度を十分に得られるようにする。

【解決手段】半導体装置は、半導体基板の上に形成された第1の層間絶縁膜101と、第1の層間絶縁膜101に形成された複数の配線105と、第1の層間絶縁膜101に複数の配線105の少なくとも1つと接続するように形成されたビア113及びダミービア106とを有している。第1の層間絶縁膜101における互いに隣り合う配線105同士の間には空隙部109が選択的に形成されており、ダミービア106は、空隙部109と接する配線105Aの下側に該配線105Aと接続して形成され、ビア113及びダミービア106は、空隙部109を介することなく第1の層間絶縁膜101により周囲を覆われている。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、ダマシン構造を有する銅多層配線を構成するトレンチのCMP工程後に露出した低誘電率膜表面のダメージを回避して配線信頼性を確保するとともに、直列抵抗の増大を抑制する。

【解決手段】 ポーラス絶縁膜に設けた凹部に埋め込まれた第1の金属膜の少なくとも頂面を、前記ポーラス絶縁膜の頂面と整合する高さまでZr及びBを含む第2の金属膜で覆う。

(もっと読む)

半導体装置およびその製造方法

【課題】十分なEM耐性および配線間TDDB寿命を確保しつつ、層間絶縁膜の低誘電率化を行っても絶縁膜ライナー膜厚を薄くすることができ、配線間の実効比誘電率Keffを低減した高速で高信頼性な配線を得ることができる。

【解決手段】第1の絶縁膜1には配線溝M1が形成されており、配線溝M1内にはCu膜2bが設けられている。Cu膜2bの上にはSiCN膜3a、SiCO膜3bおよびSiOC膜4aが順に設けられており、SiOC膜4aはSiCN膜3aおよびSiCO膜3bよりも低誘電率な絶縁膜である。SiCO膜3bの上面には、高密度化処理が施されて高密度膜3cが形成されている。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の電気的特性のばらつきを低減することにより、半導体素子の信頼性および製造歩留まりを向上させることのできる技術を提供する。

【解決手段】半導体基板1上にニッケル−白金合金膜を形成した後、熱処理温度が210〜310℃の1回目の熱処理をヒータ加熱装置で行うことで、ニッケル−白金合金膜とシリコンとを反応させて(PtNi)2Si相の白金添加ニッケルシリサイド層33を形成する。続いて未反応のニッケル−白金合金膜を除去した後、1回目の熱処理よりも熱処理温度が高い2回目の熱処理を行い、PtNiSi相の白金添加ニッケルシリサイド層33を形成する。1回目の熱処理の昇温速度は10℃/秒以上(例えば30〜250℃/秒)とし、2回目の熱処理の昇温速度は10℃/秒以上(例えば10〜250℃/秒)とする。

(もっと読む)

281 - 300 / 801

[ Back to top ]