Fターム[5F033KK32]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201) | 窒化物 (1,946)

Fターム[5F033KK32]の下位に属するFターム

Fターム[5F033KK32]に分類される特許

261 - 280 / 801

半導体装置の製造方法および半導体装置

【課題】Low−k膜の機械的強度を向上させることができる半導体装置の製造方法、およびそれにより得られる半導体装置を提供する。

【解決手段】半導体基板SB上に、SiOCを含有する骨格構造部と、炭化水素化合物を含有する空孔形成材料部とを有するSiOC膜である層間絶縁膜3が形成される。層間絶縁膜3に200nm以上260nm以下の波長を有する光が照射される。

(もっと読む)

半導体装置

【課題】 容量低減とビア加工マージンの確保を効率的に達成する。

【解決手段】 複数の配線層を有する半導体装置であって、所定領域を有する第1配線層26と、第1配線層の上層に位置する第2配線層47と、第1配線層と第2配線層との間に設けられる層間絶縁膜36と、層間絶縁膜と第1配線層の配線との間に設けられるバリア絶縁膜(29,31)とを有し、所定領域における配線上部のバリア絶縁膜の厚さは、所定領域以外の領域における配線上部のバリア絶縁膜の厚さよりも厚く、所定領域においては隣接する配線間にエアギャップ35が形成され、所定領域以外においては隣接する配線間にエアギャップが形成されない。

(もっと読む)

半導体装置およびその製造方法

【課題】配線抵抗およびビア抵抗のばらつきを配線層全体として抑制できる半導体装置およびその製造方法を提供する。

【解決手段】ビア深さBDEの深い第1のビアホールVH内の導電層(配線層IL2)と配線層IL1との接触部の抵抗は、ビア深さBDEの浅い第2のビアホールVH内の導電層(配線層IL2)と配線層IL1との接触部の抵抗よりも小さくなっている。

(もっと読む)

半導体装置

【課題】ボンディングする際に、電極パッドの下方に加わるストレスに対しての耐性が強く、且つ配線の配置が容易な半導体装置を提供する。

【解決手段】半導体基板1上に形成された多層配線層2を貫通し半導体基板1に達する支柱5a,5bにより、多層配線層2上に形成される電極パッド4の4隅のうち、少なくとも隣接する2隅を下方から支え、支柱5a,5b間に複数の梁6a,6b,6cを接続し、梁6a,6b間に部材7a,7b,7c,7dを接続する。

(もっと読む)

半導体装置

【目的】リソグラフィの解像度や、光学コントラストを向上させると共にメモリ素子領域部のチップ面積を縮小させる半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、メモリ素子領域内で、同一線幅及び同一ピッチで繰り返し配置される複数のビット線10と、前記メモリ素子領域内で、前記複数のビット線10と同層で、かつ平行に形成され、前記複数のビット線10と同一線幅及び同一ピッチで配置される複数のシャント線30と、前記複数のシャント線30の上層側から前記複数のシャント線30に跨って接続するように配置される上層コンタクトプラグ34と、を備えたことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】抵抗素子の膜厚が薄くても、抵抗素子と上層配線と接続する為のコンタクトホールを形成する際に、コンタクトホールが抵抗素子を突き抜けてしまうことを防止する半導体装置及びその製造方法を提供する。

【解決手段】基板上にゲート絶縁膜4を形成し、ゲート絶縁膜4上に第1の金属膜5、および第2の金属膜6を含む積層膜を形成し、ゲート電極形成領域及び抵抗素子部形成領域に前記積層膜が残るように、パターニングを行う。その後、ゲート電極形成領域及び前記抵抗素子部形成領域に、コンタクトホール形成領域を設定し、コンタクトホール形成予定領域を保護した状態で、抵抗素子形成予定領域の前記第2の金属膜6を除去し、その後に前記積層膜を覆うように層間膜9を形成し、コンタクトホール形成予定領域に形成された前記層間膜9を除去し、前記第2の金属膜6に達するコンタクトホールを形成する工程とを具備する。

(もっと読む)

半導体装置

【課題】ダイシング時及びボンディング時においても活性領域への水分等の不純物の侵入を防止し、小型化を容易におこなうことができる半導体装置を提供することを目的とする。

【解決手段】

半導体素子と外部接続端子とを接続する配線が貫通する開口部を含み、前記半導体素子を含む半導体層上に設けられた絶縁膜内に延在して前記半導体素子の全体を囲み、かつ前記外部接続端子の内側に配置された筒状ダミー配線を有する。

(もっと読む)

半導体装置及びその製造方法、感光性樹脂組成物並びに電子部品

【課題】有機絶縁膜を被覆した無機絶縁膜のエッチング時にエッチング残渣が生成せず、金属配線や金属層などの銅及び銅合金の腐食を抑制する半導体装置及びその製造方法、感光性樹脂組成物並びに電子部品を提供する。

【解決手段】半導体装置は、パッド電極2が形成された半導体基板1と、少なくとも前記パッド電極2上に形成された無機絶縁膜3と、無機絶縁膜3上に形成された第1の有機絶縁膜4とを備える。第1の有機絶縁膜4は、樹脂構造にフッ素を含まないポリイミド系樹脂と、複素環状化合物、チオ尿素類及びメルカプト基を有する化合物から選択される少なくとも1種の化合物とを含有する樹脂組成物から形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗上昇や表面の電極パッドの突き抜けを防止できる構造を備えた固体撮像装置を提供する。

【解決手段】 半導体装置は、半導体基板6を貫通して形成された貫通電極5と、貫通電極5の上に形成され、貫通電極5と電気的に接続する導電体からなる導電体パッド14と、半導体基板6の表面に形成され、導電体パッド14と電気的に接続する配線層3とを備える。

(もっと読む)

銅相互接続配線、ならびにそれを構成するための方法および機器

【課題】ガスクラスターイオンビーム処理プロセスの適用により、集積回路の相互接続構造に使用される、銅の相互接続配線層の表面上で、層をキャップ化する、改良された集積相互接続、集積回路の構造を形成する方法ならびに機器である。

【解決手段】

銅の拡散が抑制され、電気泳動寿命が向上し、選択金属キャップ化技術の使用、およびそれに付随した問題が解消される。銅のキャップ化処理、清浄化処理、エッチング処理、および膜形成処理用の、ガスクラスターイオンビーム処理モジュールを含む、各種クラスターツール構成について示した。

(もっと読む)

半導体装置及びその製造方法

【課題】Cuを含む配線について、配線抵抗を低く維持しつつ、しかも、ストレスマイグレーション耐性の劣化を伴うことなく、エレクトロマイグレーション耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上方に形成された層間絶縁膜36と、層間絶縁膜36内に形成されたCuより成る配線50と、層間絶縁膜36と配線50の間に形成され、Ti膜42とTa膜44との積層膜より成るバリアメタル膜46とを有し、配線50表面に、TiとSiとを含む界面層54が形成されている。

(もっと読む)

固体撮像装置と電子機器

【課題】暗電流及び白点欠陥などの特性をさらに改善し、感度向上及び混色低減が可能な固体撮像装置とカメラを提供する。

【解決手段】半導体基板10の複数の画素が集積された受光面において画素ごとにフォトダイオードPDが形成され、フォトダイオードを被覆して半導体基板上に絶縁膜(15,16,17,20,21,22,25,26,27,30,31)が形成され、絶縁膜中に埋め込まれて配線(19,24,29)が形成され、少なくともフォトダイオードの形成領域を被覆して、配線の内の最下層の配線から半導体基板に近い側に離間して炭化シリコンからなるエッチングストッパ膜STが形成され、フォトダイオードの上方部分において絶縁膜に凹部Hがエッチングストッパ膜に達するように形成され、凹部に埋め込まれて絶縁膜より高い屈折率を有する光導波路(36,37)が形成されている構成とする。

(もっと読む)

金属ヒューズ、アンチヒューズ及び/又は抵抗器を含む金属ゲート統合構造体及び方法

【課題】 個々の半導体デバイス・コンポーネントの統合の強化、製造性の向上をもたらす、半導体構造体及びそれらの半導体構造体を製造する方法を提供する。

【解決手段】 半導体構造体及び半導体構造体を製造するための方法が、半導体基板の活性領域上に配置及び形成された電界効果デバイスと、半導体基板内の活性領域から横方向に分離された分離領域上に少なくとも部分的に同時に配置及び形成された、ヒューズ構造体、アンチヒューズ構造体及び抵抗器構造体の少なくとも1つとを提供する。電界効果デバイスは、高誘電率の誘電体材料を含むゲート誘電体と、金属材料を含むゲート電極とを含む。ヒューズ構造体、アンチヒューズ構造体及び抵抗器構造体の少なくとも1つは、ゲート誘電体と同じ材料を含むパッド誘電体と、随意的に、同様にゲート電極と同じ金属材料を含むことができるヒューズ、アンチヒューズ又は抵抗器とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜中の水分による配線メタルの腐食を防止することができ、配線の信頼性向上をはる。

【解決手段】埋め込み配線を有する半導体装置であって、一部に配線用溝113が形成された配線間絶縁膜111,112と、配線間絶縁膜111,112の配線用溝113内に埋め込み形成され、且つ配線用溝113の側壁面との間にギャップを有する金属配線層115と、配線層115の側壁面と上面を覆うように形成された耐水性バリア層118とを備えた。

(もっと読む)

半導体装置

【課題】半導体装置の配線構造の信頼性を高める。

【解決手段】半導体装置は、素子103a,103bが形成された半導体基板101と、半導体基板101上に設けられた、少なくとも1層の金属層118及び水素含有ガスを原料ガスとしたプラズマCVD法により形成された第1の膜123を有する配線構造と、前記金属層118と非接触に前記半導体基板101上に形成されたTiNx(但し、0≦x)からなる第2の膜120とを具備する。

(もっと読む)

相変化メモリデバイスに電極を形成する方法

サブリソグラフィックな寸法又は高アスペクト比を含む、小寸法の開口内に電極材料を均一に形成する方法を提供する。この方法は、内部に形成された開口を有する絶縁層を提供するステップと、開口の上部及び内部に非等質的導電又は準抵抗性材料を形成するステップと、導電材料を移動化して開港内に圧縮するステップとを有する。この方法は、導電又は準抵抗性材料における空孔又は欠陥密度を堆積されたままの状態に対して低減する。移動化するステップは、押出又は熱的リフローによって達成され、空隙又は欠陥を合体、崩壊、染み透り又は他の方法によって堆積したままの導電又は準抵抗性材料から除去する。  (もっと読む)

(もっと読む)

半導体装置

【課題】切断された電気ヒューズの切断状態を良好に保つ。

【解決手段】半導体装置200は、基板上に形成された下層配線120と、下層配線120上に下層配線120に接続して設けられたビア130と、ビア130上にビア130に接続して設けられた上層配線110とを含み、切断状態において、上層配線110を構成する導電体が上層配線110の外方に流出してなる流出部が形成されることにより切断される電気ヒューズ100と、少なくとも上層配線110と同層に形成され、上層配線110に生じる熱を吸収するガード上層配線152(導電吸熱部材)とを含む。

(もっと読む)

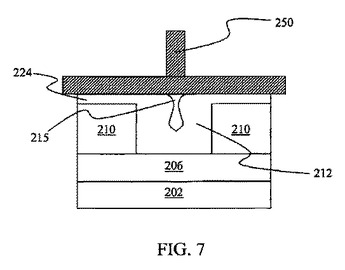

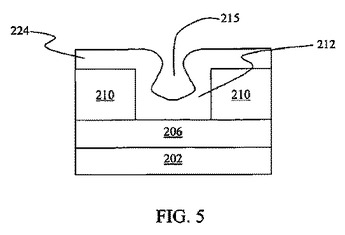

半導体デバイス内でのビアパターニングにおける金属キャップ層の侵食を低減する方法

【解決手段】

半導体デバイスの高性能な金属化システムにおいてビア開口をパターニングする間、開口(221A)が導電性キャップ層(213)を通って延び、適切なイオン衝撃が確立されて下層の金属領域(212)の材質が導電性キャップ層(213)の露出した側壁部分へ再分配され、それにより保護材質(212P)が確立される。その結果、後続のウエット化学的エッチング処理(215)において、導電性キャップ層(213)の過度な材質除去の可能性を大幅に低減することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】微細コンタクト孔の形状寸法を安定させつつ、コンタクト抵抗ばらつきを低減することができる、半導体装置およびその製造方法を提供する。

【解決手段】半導体基板11上にニッケルを含む金属シリサイド層12を形成し、その最表面12aを窒化した半導体装置を構成する。この構造によれば、金属シリサイド層最表面12aの窒化により、金属シリサイド層12中に存在するシリコンのダングリングボンドと窒素が結合するため、金属シリサイド層12中への酸素の拡散を抑制することができる。したがって、金属シリサイド層12の酸化による電気的絶縁を低減できるため、コンタクト抵抗を安定化することができる。

(もっと読む)

相変化メモリデバイスに電極を形成する気相法

サブリソグラフィック寸法又は高アスペクト比を含む小寸法を有する開口内に均一で均質に電極材料を形成する方法を提供する。この方法は、内側に形成された開口を有する絶縁層を提供し、開口上及び開口内に均質な導電又は準抵抗材料を形成するステップを含んでいる。この方法は、金属窒化物、金属アルミニウム窒化物及び金属ケイ素窒化物電極組成を形成するCLD又はALDプロセスである。この方法は、アルキル、アリル、アルケン、アルキン、アシル、アミド、アミン、イミン、イミド、アジド、ヒドラジン、シリル、アルキルシリル、シリルアミン、キレーティング、ヒドリド、サイクリック、カルボサイクリック、シクロペンタジエニル、ホスフィン、カルボニル又はハライドから選択された1以上のリガンドを含む金属前駆体を利用する。公的な前駆体は、一般式MRnを有し、Mは金属、Rは上述のリガンド、nは主要な金属原子に結合したリガンドの数に対応している。Mは、Ti、Ta、W、Nb、Mo、Pr、Cr、Co、Ni又は他の遷移金属である。  (もっと読む)

(もっと読む)

261 - 280 / 801

[ Back to top ]