Fターム[5F033KK32]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201) | 窒化物 (1,946)

Fターム[5F033KK32]の下位に属するFターム

Fターム[5F033KK32]に分類される特許

181 - 200 / 801

半導体デバイスのメタライゼーションシステムにおいて優れたエレクトロマイグレーション性能を提供すること及び敏感な低k誘電体の劣化を低減すること

【解決手段】

複雑なメタライゼーションシステムの形成の間、全体的な伝導性に否定的な影響を与えることなしにエレクトロマイグレーション性能を高めるために、伝導性キャップ層(122C)が銅含有金属領域(122A)上に形成されてよい。その一方で熱化学的処理が実行されてよく、その結果、敏感な誘電体材質(121)の優れた表面状態をもたらすことができる他、敏感なULK材質の材質特性の大きなばらつきを従来的にはもたらすことがある炭素減損を抑制することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】印加電界の履歴によって抵抗値が変化する抵抗変化層を有するスイッチ素子を多層配線中に形成し、かつ配線又は抵抗変化層の表面がダメージを受けることを抑制できるようにする。

【解決手段】この半導体装置は、第1配線層12、第2配線層16、及びスイッチビア35を備える。第1配線層12は第1配線32を有しており、第2配線層16は第2配線39を有している。スイッチビア35は、第1配線32と第2配線39を接続する。またスイッチビア35は、少なくとも底部に、抵抗変化層33を有しているスイッチ素子を有している。抵抗変化層33は、電界印加履歴に応じて抵抗値が変化する。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にCVD−Ru膜を有するウエハWを収容し、チャンバー1内に、成膜中に発生する副生成物であるCu(hfac)2の蒸気圧がその蒸気圧よりも低いCu錯体であるCu(hfac)TMVSからなる成膜原料を気相状態で導入して、ウエハWに形成されたCVD−Ru膜上にCVD−Cu膜を成膜するにあたり、チャンバー1内の圧力をCVD−Ru膜表面に吸着したCu(hfac)2の脱離および拡散が進行する圧力に制御する。

(もっと読む)

半導体装置及びその製造方法

【課題】 銅配線を備えた半導体装置において、高歩留り又は高信頼性を実現する。

【解決手段】半導体装置は、基板100上に形成された空孔率が低い低空孔率領域である絶縁膜105と低空孔率領域よりも空孔率が高い高空孔率領域107とを有し、絶縁膜105における配線溝105bに形成された銅配線109bとを備える。絶縁膜105は、配線溝105bの下部に形成されており、絶縁膜107は、配線溝105bの側壁の周辺部に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】製造プロセスが簡便な多層配線構造を有する半導体装置を提供する。

【解決手段】第1配線層と、第1配線層上の第1層間絶縁膜と、第1配線層と交差し、第1層間絶縁膜上に設けられた第2配線層と、第2配線層上の第2層間絶縁膜と、第1配線層と第2配線層とを電気的に接続するビア導体とを有し、第2配線層は、第1配線層との交差位置に当該第2配線層を分離するスペースを有し、前記ビア導体は、分離された第2配線層間を電気的に接続するように前記分離スペースを経由し、第2層間絶縁膜および第1層間絶縁膜を貫通して第1配線層に達する、半導体装置。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】コストを抑えた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、ビット線BL0i〜BL2i、ビット線BL0i〜BL2iと交差するワード線WL0i、WL1i、及びビット線BL0i〜BL2i及びワード線WL0i、WL1iの交差部で両配線間に接続されたメモリセルMC0〜MC3を有する単位セルアレイMAT00を備える。さらに、不揮発性半導体記憶装置は、第1位置に設けられたビット線BL0iの側部に接し、第1位置よりも上方の第2位置に設けられたビット線BL1iまで積層方向に延びるコンタクトプラグCL1〜CL3と、第1位置と第2位置の間の第3位置に設けられたワード線WL0iの側部に接し、第2位置よりも上方の第4位置に設けられたワード線WL1iまで積層方向に延びるコンタクトプラグCL5、CL6とを備える。

(もっと読む)

半導体装置、その半導体装置の作製方法及びその半導体装置を有する電子機器

【課題】酸化物半導体を用いた薄膜トランジスタにおいて、電界効果移動度を向上させることを課題の一とする。また、薄膜トランジスタの電界効果移動度を向上させても、オフ電流の増大を抑制することを課題の一とする。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とゲート絶縁層の間に、該酸化物半導体層より導電率が高い酸化物クラスターを形成することによって、該薄膜トランジスタの電界効果移動度を向上させ、且つオフ電流の増大を抑制することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】相異なる膜質領域を有する層間絶縁膜において、膜界面における膜剥れや隣接配線間リークの発生を抑制する。

【解決手段】単層構造の層間絶縁膜である第3の絶縁膜107は複数の空孔120を有している。第3の絶縁膜107における単位体積当たりの空孔占有率は膜厚方向に変化している。

(もっと読む)

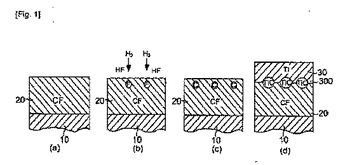

フッ化炭素膜の表面処理

半導体デバイスの製造方法は、絶縁性層をアニーリングする工程と、金属元素を含んだ障壁層を前記絶縁性層上に形成する工程とを含んでいる。前記絶縁性層は、フッ化炭素(CFx)膜を含んでいる。前記障壁層は、前記アニーリング工程後に、高温スパッタリングプロセスによって形成される。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】ダマシン配線構造を有する半導体装置に形成される配線表面の酸化物部を選択的に除去する。

【解決手段】ダマシン配線構造を有する半導体装置を製造するに際し、配線表面を、Xeのプラズマで逆スパッタリングする。本発明によれば、Xeのプラズマガスで逆スパッタリングすることにより、配線表面の酸化物部等を選択的に効率よく除去でき、ダマシン配線構造において、上下配線間のコンタクト抵抗の増大を回避できる。また、配線の上に形成されたCFなどの絶縁膜へのダメージを抑制でき、絶縁膜の誘電率変動も抑制できる。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通孔(接続孔)内に形成された絶縁膜上に設けられる配線層と半導体基板との間の電気的絶縁性の不良の発生が低減された半導体装置の製造方法を提供する。

【解決手段】半導体基板11の一方の面上に第1の絶縁層12を介して位置する第1の配線層13と、半導体基板の他方の面から第1の配線層に至る接続孔19を形成する。接続孔の側面から他方の面に亘って半導体基板上に位置し、接続孔内で第1の配線層に接する第2の絶縁層14を形成する。接続孔の側面上から他方の面上に亘って第2の絶縁層上に位置し、接続孔内で第1の配線層に接する第2の配線層16を形成する。この形成において、第2の絶縁層を、膜質の異なる2種の絶縁膜14a、14b又はそれ以上の絶縁膜の積層体から構成する。

(もっと読む)

発光装置の作製方法

【課題】平坦性の向上により、TFTの移動度を向上させ、TFTのオフ電流を低減する

。

【解決手段】基板上に非晶質構造の半導体膜を形成する工程と、前記半導体膜上に結晶化

を促進する金属元素を添加する工程と、加熱処理を行って、前記半導体膜を結晶構造の半

導体膜とする工程と、前記結晶構造の半導体膜に第1のレーザー光を照射する工程と、前

記結晶構造の半導体膜に第2のレーザー光を照射する工程とを有する。レーザー光を照射

する工程を2回設けることにより、結晶構造の半導体膜の平坦化を向上させることができ

る。その結果、TFTの移動度を向上させ、TFTのオフ電流を低減させることができる

。

(もっと読む)

半導体装置

【課題】開口率の高い半導体装置又はその作製方法を提供することを目的の一とする。また、消費電力の低い半導体装置又はその作製方法を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に設けられた酸化物半導体層と、酸化物半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の導電層と第2の導電層との順で積層されたゲート電極を含むゲート配線と、酸化物半導体層と、前記ゲート電極を含む前記ゲート配線を覆う絶縁膜と、絶縁膜上に設けられ、酸化物半導体層と電気的に接続され、第3の導電層と第4の導電層との順で積層されたソース電極を含むソース配線と、を有し、ゲート電極は、第1の導電層で形成され、ゲート配線は、第1の導電層と第2の導電層で形成され、ソース電極は、第3の導電層で形成され、ソース配線は、第3の導電層と第4の導電層で形成されている。

(もっと読む)

エレクトロマイグレーション耐性を有するビア・ライン相互接続体

【課題】 エレクトロマイグレーション耐性を有するビア・ライン間相互接続構造体及びその製造方法を提供する。

【解決手段】 導電性ビアの上層金属ライナと、下方の金属ラインの下層金属ライナとの間に、ライナ・ライナ間接触を形成する。ライナ・ライナ間接触は、急激なエレクトロマイグレーションによる故障を抑制し、金属相互接続構造体のエレクトロマイグレーション耐性を強化する。少なくとも1つの誘電体材料部分は、上層金属ライナと下層金属ライナの間の直接接触を保証するように配置された複数の誘電体材料部分を含むことができる。代替的に、少なくとも1つの誘電体材料部分は、リソグラフィ・オーバーレイ変動の許容範囲内でライナ・ライナ間直接接触が形成されるのを保証するのに十分な、導電性ビア領域との横方向の重なりを有する領域の単一の誘電体部分を含むことができる。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】多層配線構造の半導体装置のパッケージ工程や環境試験において、膜剥れが起き難い技術を提供する。

【解決手段】絶縁層中に配線層が構成された下層配線層、前記下層配線層上に設けられた層間絶縁層、前記層間絶縁層の上に設けられた絶縁層中に配線層が構成された上層配線層、及び前記層間絶縁層に構成された前記下層配線層の配線層と前記上層配線層の配線層とを電気的に接続する為の接続層とを具備する半導体装置において、

前記層間絶縁層A7に、該層間絶縁層A7の上層および/または下層に繋がる埋設層A15が構成され、前記埋設層A15および接続層A12を有する層間絶縁層A7の平均弾性率が10GPa以上であるよう構成されてなる半導体装置。

(もっと読む)

誘電ライン・バイアのエレクトロマイグレーション耐性が向上した界面層を有する相互接続構造およびその製造方法

【課題】 相互接続構造内にガウジング・フィーチャを導入することなくエレクトロマイグレーション耐性を向上させる相互接続構造を提供する。

【解決手段】 この構造は、バイア開口の底部に存在する金属界面層(または金属合金層)を含む。バイア開口は、第1の導電材料が埋め込まれた第1の誘電材料の上に位置する第2の誘電材料内に位置する。バイア開口の底部に存在する金属界面層(または金属合金層)は、第1の誘電体内に埋め込まれた下にある第1の導電材料と第2の誘電材料内に埋め込まれた第2の導電材料との間に位置する。また、エレクトロマイグレーション耐性が向上した相互接続構造を製造する方法も提供する。

(もっと読む)

半導体装置の製造方法

【課題】デュアルダマシン溝(接続孔)内への異物の残留を回避し、配線接続の信頼性および半導体装置性能の向上を図る。

【解決手段】第4配線層の配線33上に絶縁膜34〜38を順次形成し(絶縁膜34,36,38はシリコン窒化膜からなる。絶縁膜35,37はシリコン酸化膜からなる)、絶縁膜38に溝パターン40a、40bをフォトリソグラフィを用いて転写する。絶縁膜38の溝パターン40を埋め込む反射防止膜41を形成し、さらに孔パターン43を有するレジスト膜42を形成する。レジスト膜42の存在下でエッチング処理を施し、絶縁膜38,37,36および絶縁膜35の一部に孔パターン43を転写する。その後、レジスト膜42,反射防止膜41を除去し、絶縁膜38をマスクとして溝パターン40を絶縁膜37に、孔パターン43を絶縁膜35に転写する。

(もっと読む)

半導体装置

【課題】 半導体装置を提供する。

【解決手段】本発明による半導体装置(100)は、絶縁層(125)の一部および半導体層(126)を覆う第1層間絶縁膜であって、絶縁層(125)のうちの下側電極(142)上の領域を覆わない第1層間絶縁膜(102)と、絶縁層(125)および第1層間絶縁膜(102)を覆う第2層間絶縁膜(104)と、第1層間絶縁膜(102)および第2層間絶縁膜(104)に設けられたコンタクトホールを介して半導体層(125)のソース領域およびドレイン領域と電気的に接続されたソース電極(128)およびドレイン電極(130)と、ソース電極(128)およびドレイン電極(130)と同じ材料から形成され、絶縁層(125)および第2層間絶縁膜(104)に設けられたコンタクトホールを介して下側電極(142)と電気的に接続された上側電極(144)とを備える。

(もっと読む)

キャパシタ構造体

【課題】面積を増加せずとも、キャパシタの静電容量を増大させることのできるキャパシタ構造体を提供すること。

【解決手段】本発明のキャパシタ構造体は、複数個の開口部を有する第1の電極と、前記開口部の各々の中央に形成される第2の電極と、前記開口部を埋め込んで第2の電極を囲むように形成される誘電膜とを備えることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】Q値の高いモノリシックインダクタ素子を備える半導体装置及びその製造方法を提供する。

【解決手段】半導体装置50は、半導体基板1と、半導体基板1上に設けられた層間絶縁膜6と、層間絶縁膜6の上部に埋め込むように設けられ、スパイラルパターンを有する第1インダクタ配線層7と、層間絶縁膜6上及び第1インダクタ配線層7上を覆うように設けられ、第1インダクタ配線層7に沿って延びる少なくとも一つの溝状接続孔10を有するバリア絶縁膜9と、バリア絶縁膜10上に、第1インダクタ配線層7に沿って延びるように形成されると共に、溝状接続孔10を埋め込んで第1インダクタ配線層7に電気的に接続された第2インダクタ配線層11とを備える。第2インダクタ配線層11は、その長さ方向に延びるように上面側に設けられた少なくとも一つの溝状凹部12を有する。

(もっと読む)

181 - 200 / 801

[ Back to top ]