Fターム[5F033KK32]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201) | 窒化物 (1,946)

Fターム[5F033KK32]の下位に属するFターム

Fターム[5F033KK32]に分類される特許

241 - 260 / 801

半導体装置及びその製造方法

【課題】パッド領域における内部応力発生時にその応力が接続孔に偏って集中することを防止し、それに起因する配線機能の劣化を回避することを可能とするとともに、格子状の配線をCMPの対象面としたとき、CMP時のディッシング量及びエロージョン量を低減させる。

【解決手段】パッド領域内において低誘電率絶縁膜に形成された第1の接続孔の占有密度が、素子領域における前記第2の接続孔の占有密度よりも高く、パッド領域における前記低誘電率絶縁膜の上方に、前記素子領域と外部とを電気的に接続するための格子状の配線が形成される。格子状の配線は、パッド領域における低誘電率絶縁膜の上方にさらに形成された低誘電率絶縁膜に格子状の配線溝パターンが形成され、当該配線溝パターン内に配線材料を埋め込むことにより形成された配線である。また、第1の接続孔及び格子状の配線はデュアルダマシン法によって形成される。

(もっと読む)

銅の異方性ドライエッチング方法および装置

【課題】ハロゲンによる銅の腐食を生じさせずに銅を異方性エッチングすることができる銅の異方性ドライエッチング方法を提供すること。

【解決手段】基板に形成された銅膜を異方的にドライエッチングする銅の異方性ドライエッチング方法は、銅膜に対して異方性酸化処理を施す工程と、酸化処理によって形成された酸化銅をハロゲンを含有しない有機酸によりドライエッチングする工程とを含む。

(もっと読む)

電子デバイス及びその製造方法

【課題】層間絶縁膜に形成した空隙部を導電材料で充填して配線・接続部を形成する際に問題となる、下層の導電領域と配線・接続部との接続状態に起因する不都合を生ぜしめることなく、微細な配線及び接続部が所望の状態に正確且つ容易に実現されてなる信頼性の高い電子デバイスを実現する。

【解決手段】ダミー構造物16を形成し、ダミー構造物16の側面のみに側壁膜17を形成する。このダミー構造物16を覆うように層間絶縁膜18を形成する。そして、側壁膜17が残るようにダミー構造物16のみを除去し、下層配線14の表面の一部を露出させ、層間絶縁膜18に形成された開口18aをCuで埋め込み、Cuの表層を層間絶縁膜18の表面に合わせて平坦化する。以上により、下層配線14と直接的に接続されるCu接続部22を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】コーナー部を有する微細金属配線を備えた半導体装置の信頼性を向上させることを目的とする。

【解決手段】第1層間絶縁膜82に埋め込まれ、屈曲したコーナー部を有する第1配線21を一定のコーナー数毎に区切る。区切った第1配線21同士は、第2層間絶縁膜87に埋め込まれたプラグ22及び第2配線23によって連結する。第1配線はコーナー部により結晶粒径が減少するが、一定のコーナー部数で短く区切られるためエレクトロマイグレーション耐性が向上する。また、第2配線23の配線幅を調整することにより、第1配線21のコーナー部による抵抗上昇を、第2配線23で補償することができる。

(もっと読む)

半導体装置の製造装置及び半導体装置の製造方法

【課題】多層配線構造における硼窒化ジルコニウム膜と下地膜との間の密着性を向上させることにより半導体装置の信頼性を向上させた半導体装置の製造装置及び半導体装置の製造方法を提供する。

【解決手段】第1メタルキャップ膜MC1と第2メタルキャップ膜MC2とが成膜される際に、まず基板Sの表面に水素ラジカルが供給されて、表面処理である微粒子のエッチング処理や未結合手への末端処理、さらには酸化層の還元処理が実行される。そして、この表面処理が基板Sに施された後、基板Sの表面にZr(BH4)4と励起状態の窒素とが供給されて、第1メタルキャップ膜MC1及び第2メタルキャップ膜MC2である硼窒化ジルコニウム膜が成膜される。

(もっと読む)

半導体装置及びその製造方法

【課題】高速動作が可能なMIPS構造を持つメタルゲートを含む半導体装置を得られるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜3と、該ゲート絶縁膜3の上に順次形成され、TiN膜4とポリシリコン膜5とにより構成されたゲート電極20の第2のゲート電極部20bと、半導体基板1の上にゲート電極20を覆うように形成された層間絶縁膜8とを有している。層間絶縁膜8及びポリシリコン膜5を貫通して形成されたコンタクト9は、TiN膜4と直接に接続されている。

(もっと読む)

導体または半導体基板上に堆積させたカーボンナノチューブマットの製造方法

【課題】酸化層の前堆積を行うことなく、導体または半導体材料上に高密度のカーボンナノチューブマットを製造する方法を提供する。

【解決手段】拡散バリア520、拡散バリア上にアモルファスシリコン層530、アモルファスシリコン層上に金属層を含む触媒複合体を導体または半導体基板510上に堆積させる。次いで前記金属層に酸化処理を行い、最後に、酸化処理された金属層からカーボンナノチューブマット580を成長させる。

(もっと読む)

半導体装置の製造装置及び半導体装置の製造方法

【課題】多層配線構造における硼窒化ジルコニウム膜の耐酸化性を向上させることにより半導体装置の信頼性を向上させた半導体装置の製造装置及び半導体装置の製造方法を提供する。

【解決手段】絶縁膜と前記絶縁膜に囲まれた金属膜とが露出する基板を加熱した状態で収容する成膜室31Sと、Zr(BH4)4と励起した窒素とを前記成膜室31Sへ供給して加熱下である基板Sの表面に硼窒化ジルコニウム膜を成膜する成膜部とを備えた半導体装置の製造装置であって、前記成膜部が、成膜時間が経過するに連れて前記励起した窒素の供給量を低くすることを要旨とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ダマシン法によるCu配線構造の形成において、Cu−Mn合金をバリアメタル膜に組み合わせて欠陥の自己修復および密着性の向上を図る際に、Mnの拡散によるCu配線パターンの抵抗増加を抑制する配線の製造方法を提供する。

【解決手段】半導体基板上方に形成された酸素を含む絶縁膜21と、前記絶縁膜に形成された凹部21Tと、凹部の内壁に形成された高融点金属膜22と、高融点金属膜上に形成された銅とマンガンと窒素を含む金属膜23と、金属膜上に形成され、凹部を充填する銅膜24Aと、を含む構造とする。

(もっと読む)

表示装置用パネル、液晶表示装置、配線形成方法

【要 約】

【課題】剥離しない上部配線膜を形成する。

【解決手段】

下部配線膜11とコンタクトする部分や、SiN層12の表面に、インクジェット法によってIn微粒子が分散された第一の印刷液を塗布し、焼成して酸化Inから成る無機接着膜13を形成し、無機接着膜13の表面にAg微粒子が分散された第二の印刷液を塗布し、焼成して上部配線膜14を形成する。無機接着膜13は、下部配線膜11表面のMoN層23及びガラス基板10上のSiN層12と、上部配線膜14と接着性が高いので、上部配線膜14が剥離しない。

(もっと読む)

電磁波検出素子

【課題】信号配線の電子ノイズをより低減させた電磁波検出素子を提供する。

【解決手段】走査配線101(2)、信号配線3、及び共通配線102(18)をセンサ部103よりも下層に各々絶縁膜を介して設けられた異なる金属層により形成されており、信号配線3を走査配線101及び共通配線102よりも厚く形成した。

(もっと読む)

半導体装置及びその製造方法

【課題】Cuを主体とする配線について、配線抵抗を低く維持するとともに、ストレスマイグレーション耐性及びエレクトロマイグレーション耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上方に形成された層間絶縁膜28、30と、層間絶縁膜28、30に形成されたビアホール34及び配線溝36内に形成され、Ta膜より成るバリアメタル膜38と、バリアメタル膜38上に形成されたTi膜40と、バリアメタル膜38及びTi膜40が形成されたビアホール34及び配線溝36内にそれぞれ埋め込まれ、Cuより成る導体プラグ44及び配線46とを有し、Ti膜40の膜厚が、配線溝36の底部において4nm以下になっている。

(もっと読む)

半導体装置

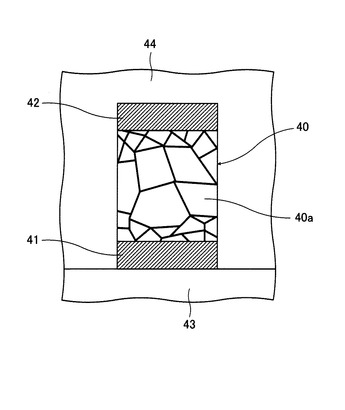

【課題】Low−k膜を層間絶縁膜として用いた半導体装置であっても、ダイシング時に発生するクラックがシールリング部へ伝播するのを抑制し、半導体装置の信頼性を向上する技術を提供する。

【解決手段】ダイシング領域側の各層にダミービア125,135,145,155,165を形成する。ダミービア125,135,145,155,165は上面からみて、縦横に等間隔に配置、あるいは千鳥配置されるように形成する。ダイシング時にクラックが発生しても、ダミービア125,135,145,155,165によって、クラックがシールリング部190にまで伝播するのを抑制することができる。その結果、回路形成領域の吸湿耐性を向上させ、信頼性の劣化を防止することができる。

(もっと読む)

相互接続構造体およびその形成方法(エレクトロマイグレーション耐性強化のための相互接続構造体)

【課題】 ビア開口の下部分を多層ライナで内側を覆うことにより強化したエレクトロマイグレーション耐性を有する相互接続構造体を提供する。

【解決手段】 多層ライナは、誘電体材料のパターン付けされた表面から外側に、拡散障壁、マルチ材料層、及び金属含有ハード・マスクを含む。マルチ材料層は、下層の誘電体キャッピング層からの残留物からなる第1材料層と、下層の金属キャッピング層からの残留物からなる第2材料層とを含む。本発明はまた、誘電体材料内に形成されたビア開口の下部分内に多層ライナを含む相互接続構造体を形成する方法を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極である金属膜/多結晶シリコン膜間の接触抵抗が大きい場合であっても、ゲートコンタクトプラグに印加した電界を十分な速度で十分に金属膜に伝えることができる半導体装置、およびその製造方法を得ることを目的とする。

【解決手段】本発明の一実施形態における半導体装置は、半導体基板1と、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3上に形成された金属膜4、当該金属膜4上に形成された多結晶シリコン膜5、を有するゲート電極6と、ゲート電極6上に形成された層間絶縁膜11と、層間絶縁膜11および多結晶シリコン膜5を貫通して金属膜4と接触するように形成されたコンタクトプラグ12と、を備える。

(もっと読む)

半導体装置およびその製造方法

【解決手段】 本発明による半導体装置は、メタル抵抗素子の下面に形成された下面酸化防止絶縁膜と、上面に形成された上面酸化防止絶縁膜と、下面酸化防止絶縁膜及び上面酸化防止絶縁膜とは別工程で、ウェハ全面に堆積した後に異方性エッチングを施しメタル抵抗素子の側面近傍にのみ形成された側面酸化防止絶縁膜とを有する。

【効果】 本発明によれば、メタル抵抗素子が酸化されて抵抗値が上昇するのを防止することができると同時に、加工プロセスを複雑にすることなく金属配線層間の寄生容量の増大を防止することができる。

(もっと読む)

半導体装置

【課題】配線とビアとの界面でのボイドの発生を抑制し、信頼性に優れた半導体装置を提供すること。

【解決手段】半導体装置1は、比誘電率が3.0以下の低誘電率の絶縁膜112中に形成され、配線幅が0.1μm以下の配線14と、配線14に接続された径が0.1μm以下のビア17と、絶縁膜112中に形成されたダミーメタル15とを有し、ダミーメタル15は、配線14の端部に対し、配線14の延在方向に沿って隣接し、ダミーメタル15と、配線14との間の距離Dが0.3μm以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程を複雑化することなく、配線の信頼性低下を招かない、配線構造を有する半導体装置及びその製造方法を得る。

【解決手段】接続孔30の底面及び側面上並びに配線用溝31の底面及び側面上にTa/TaN積層バリア層12を介して、NiFe磁性層13をPVD装置のNiFeチャンバを用いたPVD法によって成膜する。次に、同一のPVD装置の同一のNiFeチャンバを用いて、成膜条件を変更することにより、接続孔30及び配線用溝31の底面上及び層間絶縁膜11の表面上におけるNiFe磁性層13を選択的に除去する。さらに、同一のPVD装置のTaチャンバ及びCuチャンバを用いて、接続孔30の底面及び側面上並びに配線用溝31の底面及び側面上にTaバリア層及びCuシード層を順次形成する。

(もっと読む)

半導体装置

【課題】細幅配線間のTDDB寿命の低下、および細幅配線間のショートによる歩留まり低下を抑制する半導体装置を提供する。

【解決手段】半導体装置10は、ダマシン配線からなる配線層を有し、0.5μm以上の幅を有する第1の配線12と、前記第1の配線12に隣接し前記第1の配線12から0.5μm未満の間隔で配置された第2の配線14と、前記第2の配線14に隣接し前記第1の配線12から0.5μm以下の間隔で配置された第3の配線16と、を備え、前記第2および第3の配線は同電位を有するよう構成されている。

(もっと読む)

半導体装置の製造方法

【課題】配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】Al配線40を形成する際、バリアメタル41上に、Al粒子40aが第1の平均粒径となるように第1の条件で第1のAl膜を形成し、次いで、第1の平均粒径より小さい第2の平均粒径となるように第2の条件で第2のAl膜を形成する。その後、第2のAl膜上にバリアメタル42を形成し、形成後、バリアメタル41,42および第1,第2のAl膜を配線パターンに加工する。

【選択図】図9  (もっと読む)

(もっと読む)

241 - 260 / 801

[ Back to top ]