Fターム[5F033KK32]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201) | 窒化物 (1,946)

Fターム[5F033KK32]の下位に属するFターム

Fターム[5F033KK32]に分類される特許

101 - 120 / 801

半導体装置およびその製造方法

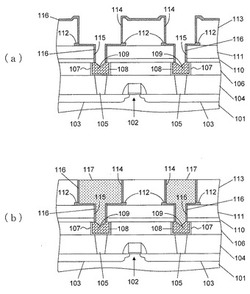

【課題】 デュアルダマシン法による配線構造の製造において、接続プラグ用のホールを通じて下層配線の表面に凹部をエッチング形成するとき、上層配線用の溝の底部が過剰エッチングされないようにする。

【解決手段】 TaNなどからなり、接続プラグに対応する開口を有する導電性膜パターン112をSiOCなどからなる層間絶縁膜111と113との間に設けた後、配線溝114、ホール115を形成する。次にTaN、Taなどからなる積層導電性膜116を堆積し、ホール115の底部の積層導電性膜116を除去し、さらに下層配線を構成するCu膜109を掘り込むエッチングを行う。このとき、導電性膜パターン112があるために配線溝114の底部の下にある層間絶縁膜111のエッチングを防止できる。その後、配線溝114およびホール115内にCuなどの導電性膜117を埋め込む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ロジック回路のコンタクト抵抗の増加を抑制しつつ、メモリ回路のキャパシタ容量を最大限に高めることが実現される半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置においては、ロジック回路を構成する配線を有する配線層の層数をMとし、メモリ回路を構成する配線を有する配線層の層数をNとしたとき(MおよびNは自然数であって、M>N)、(M−N)層あるいは(M−N+1)層の配線層にわたって、容量素子150が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】MIM容量素子形成時に生じる異常放電による容量絶縁膜の絶縁破壊を抑えることができて、高容量密度のMIM容量素子を得る。

【解決手段】半導体基板2上に、下部電極4−容量絶縁膜5−上部電極6からなるMIM容量素子1を有する半導体装置であって、上部電極4を構成する上部電極用金属膜は容量絶縁膜5との界面が、有機金属気相成長法(MOCVD)によりプラズマを用いないで堆積したアモルファス状のTiN膜などの金属窒化膜で構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

半導体装置

【課題】機能回路の電源配線及び接地配線に要する接地面積を少なくし、同時に消費電流による電源電圧降下及び接地電圧上昇を抑えることで、薄型・軽量・高機能・低価格の半導体装置を提供する。

【解決手段】機能回路に電源電圧を供給する電源配線1009及び接地電圧を供給する接地配線1010が格子状に配置されている半導体装置である。格子状にすることで、電源電圧降下及び接地電圧上昇は大幅に低減できる。また、配線幅を細くしても、格子状にしない場合と同程度の電源電圧降下及び接地電圧上昇に抑えられるので、電源配線及び接地配線の配置面積を大幅に低減できる。

(もっと読む)

半導体装置の製造方法

【課題】 組み立て工程やCMP工程時における剥離を抑制した、低誘電率層間絶縁膜の製造方法とそれを用いた半導体装置を提供する。

【解決手段】低誘電率層間絶縁膜の成膜の際、高周波と低周波の2周波を切り替え、膜厚方向に膜特性の変調をかけることで、低誘電率を保持したまま密着強度を向上させる。プラズマ発生のための高周波と低周波が同一電極から印加される。そして絶縁膜の成膜開始時あるいは成膜終了時の少なくとも一方において、低周波の入力が成膜開始時及び成膜終了時を除いた他のタイミングより高い。例えば絶縁膜は、厚さ方向における少なくともどちらか一方の端部が、高周波と低周波の2周波により密着層となり、密着層以外の部分は低周波の入力を低下あるいは0にすることで低誘電率絶縁膜となる。

(もっと読む)

半導体装置の製造方法

【課題】ビア等となる開口内への金属の埋設において、ボイドの発生を抑制することを課題とする。

【解決手段】基板上に形成された第2のp−SiCOH膜204の直上に、ハードマスクとしてTiN膜205を形成する工程と、フォトリソグラフィーとエッチングにより、TiN膜205および第2のp−SiCOH膜204を貫く開口を形成する工程と、前記開口内を洗浄する工程と、前記洗浄工程の後、TiN膜205を除去する工程と、TiN膜205を除去後、第2のp−SiCOH膜204の直上に、前記開口を埋める第2の金属膜214を形成する工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、炭化シリコン薄膜の機械強度を高め、膜の消失や剥離を防止する。

【解決手段】 ポーラスな誘電率低誘電率絶縁膜上に−CH2−結合が環状になってSiと結合し且つ二重結合を含む官能基を有する原料を用いて炭化シリコン薄膜を形成する工程と、前記炭化シリコン薄膜を所定パターンにエッチングしてハードマスクを形成する工程と、前記ハードマスクをエッチングマスクとして前記低誘電率絶縁膜をエッチングして配線形成用溝或いはビアホールの少なくとも一方を形成する工程とを設ける。

(もっと読む)

半導体装置の製造方法、半導体装置、及び半導体製造装置

【課題】有機シリカ膜を成膜したのちのプラズマ反応室の内壁のクリーニング時間を短縮する。

【解決手段】まずプラズマ反応室内壁をプリコート膜で被覆する(プリコート工程)。次いで基板上に、シリコン炭素組成比(C/Si)が1以上である有機シリカ膜を成長させる(基板処理工程)。次いで、基板を取り出した後、プラズマ反応室内壁に付着した有機シリカ膜とプリコート膜とをプラズマを用いて除去する(クリーニング工程)。プリコート膜としては、基板上に成膜された有機シリカ膜よりも少なくとも炭素含有率が低い有機シリカ膜である高酸素含有プリコート膜を用いる。

(もっと読む)

ダマシンインターコネクトのエレクトロマイグレーション抵抗を向上させる界面層

【課題】、ダマシンインターコネクトのエレクトロマイグレーション特性を向上させるべく銅線内に保護キャップを形成する方法を提供する。

【解決手段】a)酸化物を含まない銅または銅合金107の露呈領域と誘電体の露呈領域とを含む基板100を、アルミニウムを含む化合物に、少なくとも約摂氏350度の基板温度で曝して、前記誘電体および前記銅または銅合金の層の両方の上にアルミニウムを含む第1の層を形成する工程と、(b)前記第1の層の少なくとも一部を化学的に修正して、アルミニウムを含むパッシベーション層109を形成する工程と、(c)前記パッシベーション層の上に誘電体層111.を堆積させる工程とを備える方法。

(もっと読む)

半導体装置

【課題】電極パッドからの水分の拡散を防止できると共に、絶縁膜の薄膜化及び低誘電率化に対応できるようにする。

【解決手段】半導体装置は、半導体基板11の上方に形成され、外部との電気的な接続を取る接続部25である電極パッドと、半導体基板と接続部との間に積層された絶縁膜14等にそれぞれ形成され、上層の配線34が接続部と接続された複数の第1配線層及び該第1配線層同士を接続するビア31よりなる積層構造体27と、複数の絶縁膜に積層構造体の周囲を隙間なく囲むように形成され、複数の第2配線層40等及び該第2配線層同士を線状に接続するラインビア41よりなるリング構造体28と、接続部と内部回路とを電気的に接続する引き出し配線32Aとを有している。積層構造体とリング構造体とは複数の第1配線層の少なくとも1つによって互いに接続されており、引き出し配線はリング構造体と接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】配線が形成される多孔質絶縁膜がプラズマダメージ等を受けるのを防ぐことにより、高歩留り且つ高信頼性な半導体装置を得られるようにする。

【解決手段】半導体基板の上に、化学気相成長法により、炭素濃度、空孔形成剤濃度及び酸素濃度がそれぞれ異なる複数の領域を有する空孔形成剤含有膜を形成する工程を備えている。この工程は、前駆体、空孔形成剤及び酸化剤を第1の流量で流す第1の期間と、第1の期間の後に、前駆体の流量に対する空孔形成剤の流量を減少させる第2の期間と、第2の期間の後に、前駆体の流量に対する空孔形成剤の流量の減少を停止し、前駆体、空孔形成剤及び酸化剤を第2の流量で流す第3の期間と、第3の期間の後に、前駆体の流量に対する酸化剤の流量を増大させる第4の期間と、第4の期間の後に、前駆体、空孔形成剤及び酸化剤を第3の流量で流す第5の期間とを含む。

(もっと読む)

ハードマスク材料

【課題】集積回路製造工程のバックエンドプロセス、およびフロントエンドプロセスにおいて利用することができる、高硬度、且つ低応力のハードマスク膜を提供する。

【解決手段】ハードマスク膜は、応力が約−600MPaから600MPaの範囲内であり、硬度は少なくとも約12Gpaである。ハードマスク膜は、PECVD処理チャンバにおいて、高密度化プラズマ後処理を複数回行うことによって、ドープ済または未ドープのシリコンカーバイドの副層を複数成膜することによって得られる。ハードマスク膜は、SixByCz、SixByNz、SixByCzNw、BxCy、およびBxNyから成る群から選択される高硬度のホウ素含有膜を含む。ハードマスク膜は、ゲルマニウム含有率が少なくとも約60原子パーセントと、ゲルマニウム含有率が高いGeNxハードマスク材料を含む。

(もっと読む)

半導体装置

【課題】低誘電率誘電体材料などからなる層間絶縁膜を用いた多層配線構造を有する半導体装置において、機械的ストレス又は熱的ストレスに起因する層間絶縁膜のクラック又は剥離等を確実に防止する。

【解決手段】半導体基板のチップ領域の外周部にシールリング4が設けられていると共に、当該チップ領域におけるシールリング4の近傍にチップ強度強化用構造体5が設けられている。チップ強度強化用構造体5は複数のダミー配線構造(例えばダミー配線構造5A〜5E等)から構成されている。各ダミー配線構造5A〜5E等はそれぞれ、最下層及び最上層の配線層のいずれか一方のみを含むか又はいずれも含まない2層以上の配線層に亘ってビア部を介して連続的に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】研磨時にバリア膜が溶解することを抑制することができるような半導体装置及びその製造装置を提供する。

【解決手段】半導体基板上に形成された、溝109を有する絶縁膜107と、溝109に形成された第1のバリア膜111と第2のバリア膜112とを有する配線115とを備えている。第1のバリア膜111は、溝109の側壁及び底面上に形成され、第2のバリア膜112は、第1のバリア膜111を覆うように溝109に形成されている。さらに、第2のバリア膜112は、配線115の上面よりも下側に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 層間絶縁膜内の水分などによるバリアメタルの腐食を防止し、銅配線の信頼性の低下及び抵抗値の上昇を抑制し得る半導体装置、及びその製造方法を提供する。

【解決手段】 メチル基を含有する層間絶縁膜32内に配線溝37を形成する。配線溝37が形成された絶縁膜32に紫外線又は電子線を照射した後に、メチル基を有するガスを用いて絶縁膜の露出面を疎水化する。配線溝37の疎水化された内面に沿ってバリアメタル層41を形成し、該バリアメタル層41を介して配線溝37を銅配線43で充填する。一実施形態において、配線溝37はメタルハードマスク47を用いて絶縁膜32をエッチングすることにより形成され、絶縁膜32への紫外線又は電子線の照射は、メタルハードマスク47を残存させた状態で行われる。

(もっと読む)

電子装置の切断方法

【課題】半導体装置を含む電子装置の製造コストの増大を抑制可能であり、かつ、低誘電体膜の損傷を防止可能な電子装置の切断方法を提供すること。

【解決手段】本電子装置の切断方法は、基板上に複数の絶縁層及び複数の配線層が積層されている電子装置を準備する第1工程と、ブラスト処理を含む工程により、前記電子装置の切断可能領域に存在する全配線層及び全絶縁層を除去して前記基板を露出させる第2工程と、前記切断可能領域に露出する前記基板をブレードにより切断する第3工程と、を有する。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】エレクトロマイグレーションによる配線寿命の劣化を抑えると共に、配線間の抵抗が増加するのを抑えることができる半導体素子の製造方法及び半導体素子を提供する。

【解決手段】半導体素子は、半導体回路が形成された回路層10上に形成された絶縁膜20上に予め定めた配線パターンで形成された金属配線が、バックフロー効果を有する予め定めた長さに分割された複数の分割配線34A〜34Dから成り、かつ、各分割金属配線間にバリアメタル36が形成された構成となっている。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】絶縁表面上に第1配線と、前記第1配線を覆う第1層間絶縁膜と、前記第1層間絶縁膜上の一部に接して第2層間絶縁膜と、前記第1層間絶縁膜及び前記第2層間絶縁膜上に第2配線とを有し、前記第1配線と前記第2配線とが重なっている領域には、前記第1層間絶縁膜と前記第2層間絶縁膜とが積層された半導体装置である。第1配線と第2配線間に層間絶縁膜が積層されていることで寄生容量の低減が可能となる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】信頼性の高い半導体集積回路装置の製造プロセスを提供する。

【解決手段】銅ダマシン配線プロセスのバリアメタル膜のタンタル系積層膜に関し、スパッタリング成膜チャンバ内のシールド内面に、比較的薄い窒化タンタル膜およびタンタル膜が交互に成膜されるが、この連続成膜プロセスを断続的に繰り返すと、膜の内部応力により剥がれて、異物やパーティクルの原因となる。この異物やパーティクルの防止のため、繰り返し、成膜するに際して、所定の間隔を置いて、厚い膜厚を有する異物防止用タンタル膜をチャンバの実質的な内壁に成膜する工程を設ける。

(もっと読む)

101 - 120 / 801

[ Back to top ]