Fターム[5F033KK32]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201) | 窒化物 (1,946)

Fターム[5F033KK32]の下位に属するFターム

Fターム[5F033KK32]に分類される特許

121 - 140 / 801

半導体装置

【課題】動作速度が低下することを抑制することができる半導体装置を提供する。

【解決手段】半導体装置は、MOSトランジスタ9を有するシリコン基板5と、シリコン基板5上に形成され、配線および絶縁膜により構成された配線層が複数積層された多層配線層と、多層配線層内に埋め込まれた、下部電極(下部電極膜91)、容量絶縁膜92、および上部電極(上部電極膜93)を有しており、メモリ素子を構成する容量素子90と、を備え、容量素子90とMOSトランジスタ9との間にダマシン形状の銅配線(第2層配線25)が少なくとも1層以上形成され、1つの配線(第2層配線25)の上面と容量素子90の下面とが略同一平面上にあり、容量素子90上に銅配線(プレート線配線99)が少なくとも1層以上形成されている。

(もっと読む)

半導体装置

【課題】パッド電極が設けられる層間絶縁膜に低誘電率膜を用いた場合にも、該層間絶縁膜の破壊及び界面剥離を発生させず、高い接続信頼性を確保できるようにする。

【解決手段】半導体基板1の上方に、層間絶縁膜11、21等を介在させて形成された外部接続用電極を備えている。外部接続用電極は、上面を露出するパッドメタル層8と、該パッドメタル層8と半導体基板1との間に形成された第1のメタル層2と、層間絶縁膜21を貫通してパッドメタル層8と第1のメタル層2とを電気的に接続し、且つ、層間絶縁膜21に形成された少なくとも2つの第1のビア22とを有している。第1のビア22同士の最大の間隔bは、パッドメタル層8の幅寸法aよりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜を備えた半導体装置において、膜剥がれの発生及びリークパスの形成を抑制する。

【解決手段】半導体装置は、複数の空孔を含む層間絶縁膜16を備えている。層間絶縁膜16は、単層構造の膜である。層間絶縁膜16における、下面領域に含まれる空孔の空孔径及び上面領域に含まれる空孔の空孔径は、上面領域と下面領域との間に介在する中央領域に含まれる空孔の空孔径よりも小さい。

(もっと読む)

半導体装置のパッド構造

【課題】半導体装置のパッド構造を提供する。

【解決手段】半導体装置200は、半導体基板202、相互接続構造、複数のダミーメタルビア235及びパッド構造を備える。半導体基板202は、内部に複数の微小電子素子が設けられている。相互接続構造は、半導体基板202上に設けられ、複数の金属層210a〜210iと、金属層を隔離する複数のIMD層220とを有する。金属層210a〜210iは、最上金属層210iと、最下金属層210aと、最上金属層210iと最下金属層210aとの間に設けられた少なくとも2層の金属層とを含む。複数のダミーメタルビア235は、少なくとも2層の金属層間に設けられた1層又は2層以上のIMD層220内に形成される。パッド構造は、ダミーメタルビア235の上に直接設けられている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極およびこれと一体的に形成された裏面電極を有する半導体装置において、貫通電極の膜厚と裏面電極の膜厚とを独立に制御することにより、貫通電極の剥離の問題と裏面配線の剥離の問題を同時に解消することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10と、半導体基板の上方に形成された少なくとも1層からなる配線層13と、半導体基板の裏面から配線に達する貫通電極30と、半導体基板の裏面に設けられて貫通電極に接続された裏面配線40と、裏面配線に接続された外部端子50と、を含む半導体装置であり、裏面配線は、少なくとも外部端子との接続部を含む部分の膜厚が、貫通電極の膜厚よりも厚く形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】グラフェンのバリスティック伝導性を利用した低抵抗配線を備え、配線と配線接続部材の接続部分の構成の複雑化を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、基板と、基板の上方に設けられ、積層された複数のグラフェンナノリボンシート122からなるグラフェンナノリボン層121を含む下層配線12と、複数のグラフェンナノリボンシート122の少なくとも1枚を貫通し、下層配線12と上層配線13とを接続するビア14およびバリアメタル15と、を有する。

(もっと読む)

相互接続用自己整合バリアおよびキャッピング層

集積回路に使用する銅線のための集積回路用相互接続構造およびこれを作る方法が提供される。Mn、Cr、またはV含有層が、線からの銅の拡散に対しバリアを形成し、それにより、絶縁体の早期絶縁破壊を防ぎ、銅によるトランジスタの劣化を保護する。また、Mn、Cr、またはV含有層は、銅と絶縁体の間の強い接着を促進し、その結果、製造と使用中のデバイスの機械的健全性を保ち、さらに、デバイスの使用中の銅のエレクトロマイグレーションによる故障を防ぎ、また、環境からの酸素または水による銅の腐食を防ぐ。このような集積回路の形成に関しては、本発明の特定の実施形態により、Mn、Cr、V、またはCoを銅表面上に選択的に堆積させ、一方で、絶縁体表面上のMn、Cr、V、またはCoの堆積を減らす、または防ぎさえもする方法が提供される。また、Mn、Cr、またはV含有前駆物質およびヨウ素または臭素含有前駆物質を使った銅の触媒堆積も提供される。 (もっと読む)

半導体製造装置及びそれを用いた半導体装置の製造方法

【課題】冷却効率に優れ、安定的に絶縁膜を所望の特性に改質できる、冷却機構を有する紫外線照射装置を備えた半導体製造装置を提供する。

【解決手段】半導体製造装置は、紫外線発光部101と、紫外線発光部101との間に空間103が形成されるように、紫外線発光部101を覆うように配置された外套管102とを備える。外套管102は、冷却媒体が空間103の内部に流入する冷媒流入口104と、冷却媒体が空間103の外部に流出する冷媒流出口105とを有し、冷媒流出口105近傍における外套管102の内壁の上部高さは、冷媒流入口105近傍における外套管102の内壁の上部高さよりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】低誘電率膜に対するUVキュア処理による低誘電率膜の下で且つ配線の上に形成されるライナ膜とその下層の膜との間の界面剥離を、UVブロッキング膜を用いずに防ぐことにより、高歩留まりの配線構造を有する信頼性が高い半導体装置を得られるようにする。

【解決手段】基板の上に、第1の絶縁膜11を形成し、形成した第1の絶縁膜11の上部に第1の金属配線12を形成し、第1の絶縁膜11の上に、第1の金属配線12を覆うように第2の絶縁膜13を形成し、第2の絶縁膜13に対して膜質の改質処理を行う。その後に、第2の絶縁膜13の上に第3の絶縁膜14を形成し、形成した第3の絶縁膜14に対してキュア処理を行う。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

成膜方法及び半導体装置

【課題】層間絶縁膜と配線金属との間に形成されるバリア膜について、配線金属を構成する元素や層間絶縁膜を構成する元素に対して高いバリア性を提供する。

【解決手段】処理容器内に基板を載置する載置台51と周方向に沿って多数のスリットが形成された平面アンテナ部材82とを対向して設け、導波管からのマイクロ波を前記平面アンテナ部材を介して処理容器内に供給する。一方処理容器の上部からArガスなどのプラズマ発生用のガスを供給すると共にこのガスの供給口とは異なる位置から原料ガスである例えばトリメチルシランガスと窒素ガスとを供給することでこれらガスをプラズマ化し、更に載置台51の上面の単位面積当たりに供給されるバイアス用の高周波電力が0.048W/cm2以下となるようにバイアス用の高周波電力を印加する。

(もっと読む)

キャパシタ・モジュール・アレイを含む半導体構造とその製造方法および動作方法

【課題】漏れ電流の大きいキャパシタを電気的に切断することができるキャパシタ・モジュールを含む半導体構造、これを製造する方法、およびこれを動作させる方法を提供する。

【解決手段】モジュール化したキャパシタ・アレイは複数のキャパシタ・モジュールを含む。各キャパシタ・モジュールは、キャパシタと、このキャパシタを電気的に切断するように構成されたスイッチング・デバイスと、を含む。スイッチング・デバイスは、キャパシタの漏れのレベルを検出するように構成された検知ユニットを含み、漏れ電流が所定のレベルを超えるとスイッチング・デバイスがキャパシタを電気的に切断するようになっている。各キャパシタ・モジュールは、単一のキャパシタ・プレート、2つのキャパシタ・プレート、または3つ以上のキャパシタ・プレートを含むことができる。漏れセンサおよびスイッチング・デバイスを用いて、漏れを生じたキャパシタ・アレイのキャパシタ・モジュールを電気的に切断し、これによってキャパシタ・アレイを過剰な電気的漏洩から保護する。

(もっと読む)

カーボンナノチューブ配線及びその製造方法

【課題】カーボンナノチューブを有するプラグ配線において良好な電気的接続を得ることができるカーボンナノチューブ配線及びその製造方法を提供する。

【解決手段】第1配線層12上に層間絶縁膜13が形成され、層間絶縁膜13上に第2配線層14が形成されている。第1配線層12と第2配線層14との間の層間絶縁膜13内にはコンタクト孔15が形成される。コンタクト孔15内には、一端が第1配線層12に接続され、他端が第2配線層14に接続された複数のカーボンナノチューブ16が形成されている。さらに、層間絶縁膜13と第2配線層14との間にはストッパ膜17が形成され、ストッパ膜17の一部は複数のカーボンナノチューブ16の前記他端間に充填されている。

(もっと読む)

相互接続構造およびこれを形成する方法(細い相互接続開口のための導電性構造)

【課題】電気的抵抗が低い相互接続構造、および、かかる相互接続構造を形成する方法を提供する。

【解決手段】相互接続構造は、少なくとも1つの開口を含む誘電物質を含む。少なくとも1つの開口内には、任意のバリア拡散層、結晶粒成長促進層、凝集めっきシード層、任意の第2のめっきシード層、および導電性構造が配置される。典型的にはCuである金属含有導電性物質を含む導電性構造は、バンブー微細構造を有し、平均グレイン・サイズが0.05ミクロンよりも大きい。いくつかの実施形態では、導電性構造は、(111)結晶方位を有する導電性結晶粒を含む。

(もっと読む)

半導体装置

【課題】スルーホールの深さを正確に制御して、特定の配線層に選択的にエアギャップを形成した半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体素子を有する半導体基板1と、半導体基板1の上方に形成され、配線10a、10b、10c、10d、配線10c、10dの周囲のエアギャップ101、およびエアギャップ101に連続するスルーホール102含む配線構造と、スルーホール102下に形成されたスルーホールストッパー103と、を有する。

(もっと読む)

電子デバイス

【課題】製造工程数や面積の増大を招くことなく、金属薄膜抵抗の抵抗率を異ならせる素子構造を提案する。

【解決手段】基板に形成された積層構造における絶縁層間の導電膜配置階層の1つに、抵抗素子の抵抗値を規定する抵抗膜5が配置されている。また、抵抗膜5の厚さ方向の少なくとも一方の他の導電膜配置階層に、水素吸蔵金属3が、抵抗膜5と絶縁された状態で、かつ金属抵抗膜の少なくともコンタクトエッジ間の領域の全域と平面視で重なる位置と大きさで配置されている。

(もっと読む)

半導体装置

【課題】同一の半導体基板上に容量素子を備えたメモリ回路部と論理回路部を有する半導体集積回路装置において、論理回路部のみからなる半導体集積回路装置と完全互換の配線設計パラメーターを確保し、かつ微細化が進んでもセル容量を確保する。

【解決手段】容量素子を備えたメモリ回路部と論理回路部を同一の半導体基板上に有する半導体集積回路装置において、論理回路部に形成される多層配線を絶縁分離する層間絶縁膜の少なくとも複数の配線層にまたがる領域に該容量素子を埋め込むことで、該容量素子の接続に必要な配線をすべて論理回路部の多層配線で構成することにより、論理回路部の設計パラメーターを、該メモリ回路部を有しない半導体集積回路装置と完全に同一とする。また多層配線の複数層に渡るように該容量素子を配置させることで該容量素子の高さを確保し、スケーリングが進んでも必要な容量値を確保する。

(もっと読む)

デバイス構造体およびその形成方法

【課題】 相互かみ合い型導電線を有するキャパシタ構造体ならびにそれを製造する方法を提供する。

【解決手段】 相互かみ合い型構造体は、少なくとも1つの第1の金属線と、少なくとも1つの第1の金属線に平行で、しかも少なくとも1つの第1の金属線から分離されている少なくとも1つの第2の金属線と、少なくとも1つの第1の金属線の端部に接触し、しかも少なくとも1つの第2の金属線から分離されている第3の金属線とを含むことができる。少なくとも1つの第1の金属線はいずれの金属ビアにも垂直に接触しないが、少なくとも1つの第2の金属線は少なくとも1つの金属ビアに垂直に接触することができる。相互かみ合い型構造体の複数の層を垂直に積み重ねることができる。代わって、相互かみ合い型構造体は、複数の第1の金属線と複数の第2の金属線を含むことができ、それぞれの金属線はいずれの金属ビアにも垂直に接触しない。キャパシタを形成するために、回転の有無を問わず、相互かみ合い型構造体の複数の実例を横方向に複製し接合するか、あるいは垂直に積み重ねるか、またはその両方を行うことができる。

(もっと読む)

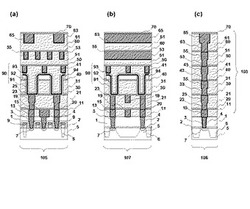

半導体装置及びその製造方法

【課題】配線の設計自由度が高く、ゲート電極及びソース/ドレイン領域に接続されるコンタクト部の形成に問題が生じ難く、微細化プロセスに適した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基体21上にゲート電極31を形成し、基体にソース/ドレイン領域37及びチャネル形成領域35を形成し、ソース/ドレイン領域37上にゲート電極31の頂面と同一平面内に頂面を有する第1層間絶縁層41を形成した後、(b)第1層間絶縁層41に溝状の第1コンタクト部43を形成し、(c)全面に第2層間絶縁層51を形成した後、(d)第1コンタクト部43の上の第2層間絶縁層51の部分に孔状の第2コンタクト部53を形成し、その後、(e)第2層間絶縁層51上に、第2コンタクト部53と接続された配線61を形成する各工程から成る。

(もっと読む)

半導体装置の製造方法

【課題】誘電率の比較的低い誘電体膜に、累積的に紫外線を含む光が照射されることに起因する不良の発生が抑制される半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜5上にLow−k膜9が形成される。次に、Low−k膜9に、所定のランプから発せられる紫外線を含む光が照射される。次に、Low−k膜9の開口部9a内にTiO2からなるバリア膜11と銅配線13が形成される。Low−k膜9上にSiCN膜15およびSiON膜17が形成される。次に、SiON膜17の上にLow−k膜19が形成される。そのLow−k膜19に、所定のランプから発せられる紫外線を含む光が照射される。

(もっと読む)

121 - 140 / 801

[ Back to top ]