Fターム[5F033LL04]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜材料の特徴点 (1,721) | 不純物、イオンを含むもの (1,142) | As、B、P系 (585)

Fターム[5F033LL04]に分類される特許

41 - 60 / 585

半導体装置およびその製造方法

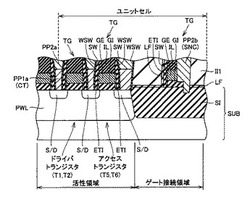

【課題】活性領域における上記プラグと、活性領域の外部における上記プラグとの双方を有する、微細化された半導体装置において、枠付け絶縁膜を確実に形成し、かつ導電性などの機能を最適化することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に形成される活性領域と、平面視における活性領域の周辺に形成されるゲート接続領域と、活性領域上に形成される複数の第1のトランジスタTGに挟まれる領域に形成される、第1のトランジスタTGと第1のトランジスタTGよりも上側の層とを電気的に接続するための第1の接続層CTと、ゲート接続領域上に形成される第2のトランジスタTGと、第2のトランジスタTGよりも上側の層とを電気的に接続するための第2の接続層とを備えている。上記第1の接続層CTには第1の導電部PP1aと第2の導電部PP2aとを含み、第2の接続層SNCには第3の導電部PP2bを含む。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】携帯電話などに使用されるハイパワーアンプの出力段は、多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成するLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。本願発明者らが、このポリシリコンプラグについて、検討したところによって、熱処理に起因してポリシリコンプラグの固相エピタキシャル成長により、ポリシリコンプラグが収縮し、それによってシリコン基板に歪が発生し、リーク不良等の原因となることが明らかとなった。

【解決手段】本願発明は、LDMOSFETを有する半導体集積回路装置において、半導体基板に埋め込まれたシリコン系導電プラグのボロン濃度が、固溶限界内に於いて、8.1x1020atom/cm3以上である。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極とポリシリコン抵抗素子とを同じ半導体基板に混載するとともに、半導体装置の設計の自由度を向上し、また、半導体装置の小型化を図る。

【解決手段】半導体基板1の主面上にゲート絶縁膜を介してMISFET用のメタルゲート電極が形成され、また、半導体基板1の主面上に積層パターンLPを介してポリシリコン抵抗素子用のシリコン膜パターンSPが形成されている。メタルゲート電極は金属膜とその上のシリコン膜とを有し、積層パターンLPは絶縁膜3aとその上の金属膜4aとその上の絶縁膜5aとを有し、絶縁膜3aは、前記ゲート絶縁膜と同層の絶縁膜により形成され、金属膜4aはメタルゲート電極の金属膜と同層の金属膜により形成され、シリコン膜パターンSPは、メタルゲート電極のシリコン膜と同層のシリコン膜により形成されている。シリコン膜パターンSPは、平面視で絶縁膜5aに内包されている。

(もっと読む)

半導体装置及びその製造方法

【課題】基板貫通電極の周囲に形成される絶縁分離部において、埋め込まれる絶縁膜が接合面を有していると、基板裏面の研削後の絶縁分離部は、接合面が基板主面から基板裏面に達することで、機械的強度が低下しやすく、貫通電極に応力を印加した場合に絶縁分離部の内側領域が孤立しやすい。

【解決手段】絶縁分離部5に埋め込まれる絶縁膜を第1の絶縁膜3と第2の絶縁膜4の少なくとも2段の積層構造とすることで、第1の絶縁膜3の接合面3Sと第2の絶縁膜4の接合面4Sとが第2の絶縁膜4の底面の接合面のない領域で分断され、機械的強度が増加し、絶縁分離部の内側領域の孤立を阻止することができる。

(もっと読む)

電子デバイス、及び、その製造方法

【課題】素子に不具合が生じることが抑制された電子デバイス、及び、その製造方法を提供する。

【解決手段】接合された2つの基板(10,50)に素子(20,60)と貫通電極(30)とが形成されて成る電子デバイスであって、素子(20,60)は、2つの基板(10,50)の少なくとも一方に形成され、貫通電極(30)は、2つの基板(10,50)の少なくとも一方に形成されており、貫通電極(30)は、一方の基板(10)における他方の基板(50)との接合面(10a)側から、その裏面(10b)まで除去されて成るトレンチ(31)と、該トレンチ(31)を構成する壁面の一部に形成された導電膜(35)と、を有する。

(もっと読む)

多層接続構造及びその製造方法

【課題】3次元積層ICデバイスにおいて、相互接続領域のコンタクトレベルのスタックへの電気接続形成工程を簡略化する製造方法を提供する。

【解決手段】各コンタクトレベルは導電層と絶縁層とを有する。コンタクト開口を作り出すために、第1のコンタクトレベルを露出させるように上部層の一部が除去される。N個のマスクを用いて、最大2N個のコンタクトレベルまでコンタクト開口がエッチングされる。各マスクは、コンタクト開口のうちの実効的に半数をエッチングするために使用される。Nが3であるとき、第1のマスクにより1つのコンタクトレベルがエッチングされ、第2のマスクにより2つのコンタクトレベルがエッチングされ、第3のマスクにより4つのコンタクトレベルがエッチングされる。コンタクト開口の側壁に誘電体層が形成され得る。コンタクト開口内に導電体が形成され、前記誘電体層が該導電体を前記側壁から電気的に絶縁する。

(もっと読む)

パターン形成方法

【課題】微細なパターンと比較的サイズが大きめのパターンとを有するパターン形成方法で、サイズが大きめのパターンを従来に比して精度良く形成することができるパターン形成方法を提供する。

【解決手段】実施形態によれば、加工対象上の芯材膜31に開口を形成した後、マスク膜32をコンフォーマルに形成する。マスク膜32をエッチバックして芯材膜31の側面に第1の幅のマスク膜32を残す。開口の形成領域以外の領域にレジストパターン35aを形成し、これをマスクに芯材膜31をエッチングする。さらに、芯材膜31をスリミングして第1の幅より小さい第2の幅のラインアンドスペース状のパターンを形成する。側壁膜をコンフォーマルに形成した後、エッチバックし、さらに芯材膜31を除去して、加工対象上に側壁膜からなる側壁パターンを形成する。そして側壁パターンで加工対象をエッチングする。

(もっと読む)

半導体装置およびその製造方法、並びに表示装置

【課題】3層以上の配線を接続する際に、最も効率的にかつ最小面積で接続を行えるコンタクト構造を実現可能な半導体装置およびその製造方法、並びに表示装置を提供する。

【解決手段】基板201上に3層以上のn層の導電層202〜204が積層して形成され、n層の導電層がコンタクトパターンを介して接続され、コンタクトパターンが形成される一つの主コンタクト領域には、(n−1)個の導電層202,203を接続する(n−1)個の接続領域211,212を有し、(n−1)個の導電層のうち基板201に対する積層方向(基板201の主面に対する法線方向)において第1層より上層の導電層は、その終端部がコンタクトパターンCPTNの縁の一部に臨むように形成され、(n−1)個の導電層は、第n層の導電層により電気的に接続されている。第n層の導電層は、コンタクトパターンCPTNであるコンタクト孔を埋めつくよう形成されている。

(もっと読む)

半導体装置の製造方法

【課題】本実施形態は、コンタクトプラグの抵抗の低減を行うことができる半導体装置の製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板にコンタクトホール又はコンタクトトレンチを形成し、コンタクトホール又はコンタクトトレンチの底に、アモルファスシリコン層又は多結晶シリコン層を形成し、アモルファスシリコン層又は多結晶シリコン層を覆うように不純物を含むニッケル膜を形成し、加熱することによりニッケル膜とアモルファスシリコン層又は多結晶シリコン層とを反応させて、ニッケルシリサイド膜を形成し、コンタクトホール又はコンタクトトレンチを埋め込むようにコンタクト金属膜を形成する。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】隣接するメモリセルゲート電極間に空隙を形成することで結合容量を抑制し、複数のコンタクト同士の短絡を防止しメモリの信頼性を向上する。

【解決手段】半導体記憶装置は、複数の選択ゲート電極間に形成され、選択ゲート電極に近接した側の側面と当該選択ゲート電極との第2間隔が第1間隔より広い層間絶縁膜11と、複数のメモリセルゲート電極間に空隙AGを備えるよう当該空隙AGの上部を被覆し、複数の選択ゲート電極間においては当該選択ゲート電極の側面および層間絶縁膜11の側面に沿って形成され、その上部に窪部Rを備えて形成されたエアギャップ形成膜12と、複数のメモリセルゲート電極上のエアギャップ形成膜12上に形成され、複数の選択ゲート電極間ではエアギャップ形成膜12の窪部Rの内側に埋込まれたリフィル膜13と、複数の素子領域に接触するように層間絶縁膜11に形成された複数のコンタクトCBa,CBbを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグ形成時に位置ずれが発生しても水分や不純物が溜まる窪みが発生することがなく、微細化しても長期間にわたる信頼性を確保できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1の絶縁膜121の上に形成された強誘電体キャパシタ131と、強誘電体キャパシタ131を覆う第2の絶縁膜311及びエッチングストッパ膜312と、エッチングストッパ膜312の上面からトランジスタTの不純物領域に到達する第1のコンタクトホール内に導電体材料を充填して形成された第1のプラグ313と、エッチングストッパ膜の上に形成された第3の絶縁膜314と、第3の絶縁膜314の上面から第1のプラグに到達する第2のコンタクトホール内に導電体材料を充填して形成された第2のプラグ315とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板を貫通する貫通電極の周囲に形成される環状の絶縁分離部において、絶縁分離部を構成する酸化膜の応力により絶縁分離部周囲の半導体基板が変形する。

【解決手段】絶縁分離部の基板側に深さ方向に圧縮応力を与える第1の膜4を形成し、第1の膜4上に深さ方向に引張応力を与える第2の膜6膜を形成し、その際、第1及び第2の膜の膜厚を圧縮応力と引張応力とがほぼ釣り合うように調整する。

(もっと読む)

Cu合金膜、及びそれを備えた表示装置または電子装置

【課題】基板及び/又は絶縁膜との高い密着性を有し、且つ、液晶表示装置などの製造過程で施される熱処理の後も低い電気抵抗率を有する新規なCu合金膜を提供すること。

【解決手段】表示装置用Cu合金膜であって、前記Cu合金膜は、Cu−Mn−B合金で構成されており、前記Cu合金膜の基板側の界面(I)から、前記Cu合金膜の最表面に向って50nm(II)までの深さ方向のMn量およびB量をそれぞれ、Mn量(MnI−II)およびB量(BI−II)とすると共に、前記Cu合金膜の深さ50nm(II)から、前記Cu合金膜最表面(III)までの深さ方向のMn量およびB量をそれぞれ、Mn量(MnII−III)およびB量(BII−III)とし、前記Mn量のMnI−IIとMnII−IIIとの関係が、2.0≦(MnI−II/MnII−III)であると共に、前記B量のBI−IIとBII−IIIとの関係が、1.5≦(BI−II/BII−III)であること。

(もっと読む)

発光装置の作製方法

【課題】微細な配線パターンを備えた発光装置の作製方法の提供。

【解決手段】Inと、Gaと、Znとを有する酸化物半導体層を形成し、酸化物半導体層上に第1の導体パターンを形成し、第1の導体パターンより微細な第2の導体パターンを形成し、前記第2の導体パターンと電気的に接続する発光素子を形成する発光装置の作製方法であって、第2の導体パターンは、酸化物半導体層を横断する。

(もっと読む)

電気光学装置の製造方法

【課題】素子基板に絶縁膜を成膜した際にフッ素が混入しても、電界効果型トランジスターに特性異常が発生することを防止することのできる電気光学装置の製造方法を提供すること。

【解決手段】素子基板10にシリコン酸化膜からなる絶縁膜12を成膜する第1絶縁膜成膜工程の後、画素トランジスター30(電界効果型トランジスター)の半導体層1aを形成する半導体層形成工程を行う前に、絶縁膜12に水素を導入する第1絶縁膜水素導入工程を行う。また、シリコン酸化膜からなる層間絶縁膜41を形成する第2絶縁膜成膜工程の後、層間絶縁膜41に対して水素の導入を行う第2絶縁膜水素導入工程を行う。このため、絶縁膜12や層間絶縁膜41にフッ素が混入していた場合でも、かかるフッ素は、水素と結合してフッ化水素として放出される。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

半導体装置

【課題】絶縁耐量を改善することができる半導体装置を得る。

【解決手段】Si基板10(基板)上にゲート抵抗7(下配線)が設けられている。ゲート抵抗7を層間絶縁膜12が覆っている。層間絶縁膜12上に、互いに分離したアルミ配線5a,5b(第1及び第2の上配線)が設けられている。アルミ配線5a,5bを半絶縁性の保護膜4が覆っている。ゲート抵抗7の直上であってアルミ配線5aとアルミ配線5bとの間の領域に、保護膜4が設けられていない。

(もっと読む)

半導体装置およびその製造方法

【課題】配線部を通じた信号伝搬速度を向上できるようにした半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板上に形成された第1絶縁膜と、前記第1絶縁膜上に形成された、前記第1絶縁膜より比誘電率が高い第2絶縁膜と、前記第2絶縁膜と隣接する側面が順テーパ形状を有し、前記第1絶縁膜および前記第2絶縁膜を貫通して形成された複数の縦柱状プラグと、前記第2絶縁膜上に形成された、前記第2絶縁膜よりも比誘電率が低い第3絶縁膜と、前記複数の縦柱状プラグの上部に到達するように前記第3絶縁膜に形成された複数の溝と、前記複数の溝内にそれぞれ形成され、前記複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部と、を備える。

(もっと読む)

半導体装置

【課題】容量素子を備え、電気的特性の安定化が可能な半導体装置を提供する。

【解決手段】半導体基体1上の配線層に形成されている配線と絶縁層とからなる容量素子10を備える。そして、容量素子10の形成領域内の半導体基体11上に形成されている導体パターンと、導体パターンの電位を固定するための電位固定端子28とを備える半導体装置を構成する。

(もっと読む)

41 - 60 / 585

[ Back to top ]