Fターム[5F033MM02]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 埋め込み型配線、ダマシン (3,807) | デュアルダマシン (1,592)

Fターム[5F033MM02]に分類される特許

161 - 180 / 1,592

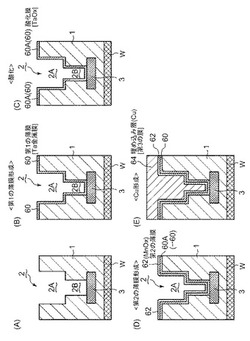

成膜方法及び処理システム

【課題】比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成することが可能な成膜方法を提供する。

【解決手段】絶縁層1が表面に形成された被処理体Wに対して成膜処理を施す成膜方法において、第1の金属よりなる第1の薄膜60を形成する第1の薄膜形成工程と、前記第1の薄膜を酸化して酸化膜60Aを形成する酸化工程と、前記酸化膜上に第2の金属を含む第2の薄膜62を形成する第2の薄膜形成工程とを有する。これにより、比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成する。

(もっと読む)

誘電体膜の材料特性を高めるための活性化学的方法

【課題】ケイ素含有誘電体材料の層の誘電率の修復

【解決手段】第1の誘電率および少なくとも1つの表面を有するケイ素含有誘電体材料の層の誘電率の修復方法であって、ケイ素含有誘電体材料の層の第1の誘電率が第2の誘電率まで増加しており、該方法は、ケイ素含有誘電体材料の層の少なくとも1つの表面と、ケイ素含有流体とを接触させるステップ、そしてケイ素含有誘電体材料の層の少なくとも1つの表面を、紫外線照射、熱、および電子ビームからなる群から選択されるエネルギー源に曝すステップ、の各ステップを含み、ケイ素含有誘電体材料の層は、ケイ素含有誘電体材料の層をエネルギー源に曝した後の第2の誘電率より低い第3の誘電率を有する、方法。

(もっと読む)

半導体装置の製造方法、配線用銅合金、及び半導体装置

【課題】半導体装置の歩留まりと信頼性を向上させる。

【解決手段】配線凹部に埋め込まれた部分以外のバリアメタル膜3b上のCu膜5bを化学機械研磨によって除去する。そして配線凹部内のCu膜5b上に、添加元素からなる層6bを形成する。添加元素を層6bからCu膜5b中に拡散させて、Cu表面、及びCu結晶粒の粒界及び該粒界近傍の位置においてCu結晶粒内部よりも添加元素の濃度が高い界面及びその近傍を形成するとともに、Cu膜5b中の酸素を層6bにゲッタリングさせる。その後、余剰な層6bを除去し、さらに絶縁膜上のバリアメタル膜3bを除去する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】歩留まりに優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、基板内の記憶回路領域に形成されており、多層配線層内に埋め込まれた少なくとも1以上の容量素子および周辺回路を有する記憶回路と、平面視において、基板内の憶回路領域とは異なる領域である論理回路領域に形成された論理回路と、を備え、容量素子は、下部電極、容量絶縁膜、上部電極、埋設電極および、上部接続配線で構成されており、上部接続配線と埋設電極とは、同一の材料かつ一体に構成されており、上部接続配線と下部電極との間には、論理回路を構成する前記配線が少なくとも1以上設けられており、上部接続配線の上面と、上部接続配線と同じ配線層に形成された論理回路を構成する配線の上面とが、同一面を構成する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】Cuを主要な成分とする再配線に設けられた外部接続用Auパッドの剥離を抑制する。

【解決手段】Cu膜15aの上部にNi膜15bを積層した2層膜からなる再配線15の表面には、ワイヤが接続されるパッド18が形成されている。パッド18は、Ni膜19aの上部にAu膜19bを積層した2層膜からなり、再配線15の上面および側面を覆うように一体形成されている。これにより、再配線15とパッド18の接触面積が大きくなるので、パッド18が再配線15から剥がれ難くなる。

(もっと読む)

配線構造の形成方法および配線構造

【課題】太い幅の配線溝と細い幅の配線溝をCuの電解メッキで充填する際に、アンダープレートの発生を抑制し、化学機械研磨後におけるディッシングの発生を抑制する。

【解決手段】表面の第1の領域に縦/横比小さい第1の配線溝22Aが形成され、表面の第2の領域に縦/横比が大きい第2の配線溝22Bを形成された絶縁膜の表面上にレジスト膜R1を形成し、第1の領域を露出する第1のレジスト開口部R1Aを形成する工程と、レジスト膜をマスクに電解メッキを行い、第1の配線溝を第1の配線パタ―ン25Aで充填する工程と、第2の領域を露出する第2のレジスト開口部を形成する工程と、レジスト膜をマスクに電解メッキを行い、第2の配線溝を第2の配線パタ―ンで充填する工程と、レジスト膜を除去し、第1の配線パタ―ンおよび第2の配線パタ―ンを、それぞれの表面が絶縁膜の表面に一致するように、化学機械研磨により平坦化する工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】プロセスマージンを大きく取れる配線配置構造を提供する。

【解決手段】基板上に形成された複数の第1配線6を含む第1配線層と、第1配線層上に形成され、第1配線6に接続された複数のビアコンタクト10を含むコンタクト層と、コンタクト層上に形成され、ビアコンタクト10に接続された複数の第2配線14を含む第2配線層とを備える半導体装置において、コンタクトピッチは、第1配線6の最小配線ピッチ、又は、第2配線14の最小配線ピッチ、よりも大きくなるようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】low−k膜のワイヤーボンディング時の荷重による変形やクラッキングの発生を回避し、半導体装置の信頼性の低下を抑制することが可能な半導体装置とその製造方法を提供する。

【解決手段】半導体装置において、基板上に形成された絶縁層と、絶縁層上に形成された複数の層間絶縁膜と、層間絶縁膜中にそれぞれ形成される複数の配線層及びビアからなる多層配線と、複数の配線層のうち最下層の配線層より基板側に形成されたメタルパッドと、メタルパッドの一部の領域上の絶縁層及び層間絶縁膜が除去されて形成された開口部と、メタルパッド上に、複数の層間絶縁膜を貫通し、開口部を取り囲むように設けられるパッドリングと、を備える。

(もっと読む)

半導体装置の製造方法

【課題】ポーラスLow−k膜の信頼性を向上させる。

【解決手段】プラズマCVD法によって層間絶縁膜IL2を形成する際にCVD装置内に供給するポロジェンの流量を、ポロジェンおよびメチルジエトキシシランの合計の流量の30%以上60%以下とすることで、層間絶縁膜IL2内に形成される空孔10の大きさを小さくし、プロセスダメージによって層間絶縁膜IL2の表面に変質層CLが形成されることを防ぐ。また、水分を含む変質層CLの形成を抑えることで、各配線を構成するバリア膜および主導体膜の酸化を防ぎ、各配線間の耐圧の劣化を防ぐ。これにより、層間絶縁膜IL2に隣接して形成される配線のEM寿命および前記配線の線間TDDB寿命の劣化を防ぐ。

(もっと読む)

半導体装置

【課題】ポーラスLow−k膜の信頼性を向上させる。

【解決手段】ポーラスLow−k膜からなる第2ファイン層の層間絶縁膜IL2内の空孔10および空孔11の平均径を1.0nm以上1.45nm未満とすることで、プロセスダメージによって層間絶縁膜IL2の表面に変質層CLが形成されることを防ぐ。また、水分を含む変質層CLの形成を抑えることで、各配線を構成するバリア膜および主導体膜の酸化を防ぎ、各配線間の耐圧の劣化を防ぐ。これにより、層間絶縁膜IL2に隣接して形成される配線のEM寿命および前記配線の線間TDDB寿命の劣化を防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】下層の金属配線のダメージがなく上層の金属配線が形成され、かつ、配線間の寄生容量が低減された半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板上に設けられた第1の金属配線層と、

前記第1の金属配線層上に設けられ、該第1の金属配線層の金属の拡散を防止する拡散防止膜と、前記拡散防止膜上に設けられた第1の絶縁膜と、前記第1の絶縁膜上に設けられた、前記拡散防止膜と同じ材料からなる第2の絶縁膜と、前記第2の絶縁膜上に設けられた第3の絶縁膜と、前記拡散防止膜、前記第1の絶縁膜、前記第2の絶縁膜及び前記第3の絶縁膜に形成された接続孔に充填され、前記第1の金属配線層に電気的に接続された第2の金属配線層と、を備えたことを特徴とする。

(もっと読む)

絶縁パターン形成方法及びダマシンプロセス用絶縁パターン形成材料

【課題】 煩雑なエッチング工程等を施すことなく、簡便に多層構造が形成できる、絶縁パターン形成方法及び樹脂組成物を提供すること。

【解決手段】 〔I〕基板上に有機パターンを形成する工程と、

〔II〕前記有機パターンのパターン間に絶縁材料を埋め込む工程と、

〔III〕前記有機パターンを除去し、前記絶縁材料からなる反転パターンを得る工程と、

〔IV〕得られた反転パターンを硬化させる工程と、

を有することを特徴とする、絶縁パターン形成方法と、ダマシンプロセス用絶縁パターン形成材料を提供する。

(もっと読む)

半導体装置の製造方法

【課題】安定した形状の信頼性の高いエアギャップを効率良く形成する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、半導体基板上に、ビアホール及びエアギャップ用トレンチを含む複数のホールを有する層間絶縁膜を形成する。次に、エアギャップ用トレンチ内に有機材料を埋め込んだ後、硬化させる。また、ビアホール内にビアプラグを形成する。この後、エアギャップ用トレンチ内に埋め込まれた有機材料を除去することにより、エアギャップを形成する。

(もっと読む)

半導体素子、及びその形成方法

【課題】 信頼性が向上する半導体素子、及びその形成方法を提供する。

【解決手段】 半導体素子の形成方法は、半導体基板100の上にゲート電極120及びゲート電極120の両側にスペーサー110を形成する段階、ゲート電極120の上にキャッピングパターン170を形成する段階、ゲート電極120の間にメタルコンタクト195を形成する段階を含み、キャッピングパターン170の幅はゲート電極120の幅より大きく形成される。これにより、形成された半導体素子は、メタルコンタクト195とゲート電極120との間での電気的な短絡を效果的に防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗変化素子を半導体装置に組み込む際の必要なフォトマスクを削減しても高密度化が可能な抵抗変化素子を搭載した半導体装置及びその製造方法を提供すること。

【解決手段】配線溝を有する層間絶縁膜14と、配線溝に埋め込まれた配線16aと、配線16aを含む層間絶縁膜14上に形成されるとともに、配線16aに通ずる下穴を有する層間絶縁膜18と、少なくとも下穴が配置された領域における配線16a上に形成されるとともに、抵抗が変化する抵抗変化膜19aと、下穴が配置された領域における抵抗変化膜19a上に形成されたバリアメタル20aと、下穴が配置された領域におけるバリアメタル20a上に形成されたプラグ21aと、を備え、抵抗変化素子5は、第1電極と第2電極との間に抵抗変化膜19aが介在した構成となっており、配線16aは、第1電極を兼ね、バリアメタル20aは、第2電極を兼ねる。

(もっと読む)

半導体装置およびその製造方法

【課題】パッド電極に荷重または衝撃力が加わっても、周囲の絶縁膜にクラックが発生しにくい構造の半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、平面形状が、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形、ならびに、これらの少なくとも一部分を含む形状の組合せからなる群から選ばれた平面形状となるような凹部を形成する凹部形成工程と、前記凹部の内面に少なくとも一部を被覆する下敷膜を形成する下敷膜形成工程と、絶縁膜で覆われた前記凹部に導電性の電極材質を埋め込むパッド部形成工程とを含み、前記凹部形成工程は、第1の凹部を形成する工程と、前記第1の凹部の一部分においてさらに深く凹む第2の凹部を形成する工程とを含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ビア深さのバラツキを抑制することができる半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に、SiおよびCを含むキャップ絶縁膜を形成する工程と、キャップ絶縁膜上に、キャップ絶縁膜と比較して、シリコン原子数に対する炭素原子数の組成比が高い、有機シリカ膜を形成する工程と、不活性ガス、Nを含むガス、フッ化炭素ガスおよび酸化剤ガスを含む混合ガスを用いたプラズマ処理により、有機シリカ膜に、異なる開口径を有する2以上の凹部を形成する工程と、を含む。

(もっと読む)

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

空隙組込みの構造体及び方法

【課題】 空隙を組み込んだ構造体及びその形成方法を提供する。

【解決手段】 VLSI及びULSI用の空隙含有金属・絶縁体相互接続構造体を、光パターン化可能低k材料を用いて作成する方法、及び形成した空隙含有金属・絶縁体相互接続構造体を開示する。より具体的には、本明細書で説明する方法は、内部に種々異なる深さの空隙がフォトリソグラフィにより画定された光パターン化可能低k材料の内部に構築される相互接続構造体を提供する。本発明の方法においては、空隙を形成するのにエッチ・ステップは必要としない。光パターン化可能低k材料内部の空隙を形成するのに、エッチ・ステップを必要としないで、本発明において開示する方法は、高信頼性の相互接続構造体を提供する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板SSと、半導体基板SS上に形成され、周辺配線P1および配線L2が形成された配線層LL1,LL2と、配線層LL2に形成され、配線L3を含む配線層LL3と、配線層LL3上に形成され、磁気記憶素子MRを含む配線層LL4とを備え、配線L1,L2上に形成された拡散防止膜NF1,NF2は、SiCN膜またはSiC膜から形成され、配線L3上に形成された拡散防止膜NF3は、SiNから形成される。

(もっと読む)

161 - 180 / 1,592

[ Back to top ]