Fターム[5F033MM04]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898)

Fターム[5F033MM04]の下位に属するFターム

Fターム[5F033MM04]に分類される特許

21 - 40 / 46

半導体装置及びその製造方法

【課題】下層の金属配線のダメージがなく上層の金属配線が形成され、かつ、配線間の寄生容量が低減された半導体装置及びその製造方法を提供する。

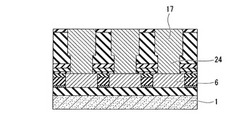

【解決手段】本発明に係る半導体装置は、半導体基板上に設けられた第1の金属配線層と、

前記第1の金属配線層上に設けられ、該第1の金属配線層の金属の拡散を防止する拡散防止膜と、前記拡散防止膜上に設けられた第1の絶縁膜と、前記第1の絶縁膜上に設けられた、前記拡散防止膜と同じ材料からなる第2の絶縁膜と、前記第2の絶縁膜上に設けられた第3の絶縁膜と、前記拡散防止膜、前記第1の絶縁膜、前記第2の絶縁膜及び前記第3の絶縁膜に形成された接続孔に充填され、前記第1の金属配線層に電気的に接続された第2の金属配線層と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

半導体デバイス及びその製造方法

本願は、半導体デバイス及びその製造方法に関するものである。本発明の半導体デバイスの製造方法は、半導体基板を提供する工程と、半導体基板に、該半導体基板に形成されたゲート絶縁層及び該ゲート絶縁層に形成された犠牲ゲートを含むゲート領域と、ソース/ドレイン領域とを含むトランジスタ構造を形成する工程と、第1の層間絶縁層を堆積し、犠牲ゲートを露出させるように該第1の層間絶縁層に対して平坦化を行う工程と、犠牲ゲートを除去して、リプレースメントゲートホールを形成する工程と、第1の層間絶縁層におけるソース/ドレイン領域に対応する位置に、第1のコンタクトホールを形成する工程と、第1のコンタクトホール及びリプレースメントゲートホールに第1の導電材料を充填して、ソース/ドレイン領域に接触する第1のコンタクト部と、リプレースメントゲートとを形成する工程とを含む。本発明によれば、リプレースメントゲートと第1のコンタクト部は、同一の工程で同じ材料を堆積して形成することができるため、製造プロセスを簡単化できた。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜を除去するエッチング中に、異常エッチングを防止する。エッチング工程において加わる水圧や風圧によりガードリングの形状が変形して剥離し、欠陥が発生することを防止する。

【解決手段】半導体装置は、メモリセル領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた周辺回路領域と、ガードリング及び周辺回路領域上に設けられた支持体膜と、周辺回路領域内に設けられたコンタクトプラグとを有する。ガードリングとコンタクトプラグは、同一の導電材料から構成される。

(もっと読む)

集積回路および集積回路の製造方法

【課題】トランジスタのゲート電極上に第1の誘電体層を形成し、かつ金属層と接合したダマシン構造を形成する方法を提供する。

【解決手段】トランジスタのゲート電極上に第1の誘電体層を形成し、第1の誘電体層上にエッチストップ層を形成し、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出し、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、トランジスタのS/D領域に接触させ、さらに金属層と接合したダマシン構造を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、収納容器に半導体ウエハを長期間保管しても、パッド部にフッ化物などの汚染物質が付着することを防止できる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、スクライブライン及びスクライブラインの内側に位置する製品チップ領域を有する半導体ウエハ上に絶縁膜を形成する工程(S12)と、製品チップ領域上に位置する第1のパッド部及びスクライブライン上に形成された評価用素子に接続された第2のパッド部を絶縁膜上に形成する工程8(S13)と、絶縁膜上、第1及び第2のパッド部の上にパッシベーション膜を形成する工程(S14)と、半導体ウエハを、収納容器に保管する工程(S15)と、収納容器から半導体ウエハを取り出し、パッシベーション膜をエッチングすることにより、パッシベーション膜に第1のパッド上に位置する開口部を形成する工程(S17)とを具備することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の設計自由度が高く、ゲート電極及びソース/ドレイン領域に接続されるコンタクト部の形成に問題が生じ難く、微細化プロセスに適した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基体21上にゲート電極31を形成し、基体にソース/ドレイン領域37及びチャネル形成領域35を形成し、ソース/ドレイン領域37上にゲート電極31の頂面と同一平面内に頂面を有する第1層間絶縁層41を形成した後、(b)第1層間絶縁層41に溝状の第1コンタクト部43を形成し、(c)全面に第2層間絶縁層51を形成した後、(d)第1コンタクト部43の上の第2層間絶縁層51の部分に孔状の第2コンタクト部53を形成し、その後、(e)第2層間絶縁層51上に、第2コンタクト部53と接続された配線61を形成する各工程から成る。

(もっと読む)

半導体装置およびその製造方法

【課題】製造プロセス中に磁性体膜の材料の拡散を防止しながら、高い磁気シールド効果を有するヘテロ構造磁気シールドを備えた半導体装置を提供する。

【解決手段】半導体装置10は、半導体基板20、半導体基板20の主面上に形成され、かつ多層配線層11Bを含む半導体素子12、および半導体素子12を被覆するヘテロ構造磁気シールド170を含む。ヘテロ構造磁気シールド170は、第一の磁気シールド積層構造16Aと磁気シールド積層構造16Aを覆う第二の磁気シールド積層構造16Bを含む。第一および第二の磁気シールド積層構造16Aおよび16Bは、いずれも、半導体素子12を被覆する磁性体からなる磁気シールド膜および半導体素子12と磁気シールド膜との間に介在し磁性体の拡散を防止するバッファ膜とを有する。

(もっと読む)

表示装置用Al合金膜、薄膜トランジスタ基板および表示装置

【課題】Al合金膜とTFTの半導体層との間のバリアメタル層を省略可能な新規のSiダイレクトコンタクト技術を提供する。詳細には、Al合金膜をTFTの半導体層と直接接続しても、AlとSiの相互拡散を防止でき、良好なTFT特性が得られると共に、TFTの製造工程でAl合金膜に約100〜300℃の熱履歴が加わった場合でも、低い電気抵抗と優れた耐熱性が得られる新規なSiダイレクトコンタクト技術を提供する。

【解決手段】本発明の表示装置用Al合金膜は、表示装置の基板上で、薄膜トランジスタの半導体層と直接接続されるAl合金膜であって、上記Al合金膜は、Geを0.1〜4原子%;La、GdおよびNdよりなる群から選ばれる少なくとも1種を0.1〜1原子%;並びにTa、Nb、Re、ZrおよびTiよりなる群から選ばれる少なくとも1種を含有する。

(もっと読む)

金とニッケルの選択エッチング液

【課題】

金とニッケルとが共存する材料の1液でのエッチングを可能にし、さらに金およびニッケルのエッチングレートを制御できるエッチング方法およびエッチング液を提供する。

【解決手段】

ヨウ素系エッチング液において、無機酸または常温で固体の有機酸、および/または有機溶剤を加えて、各成分の配合比を調節したエッチング液とし、金および/またはニッケルをエッチングする。

(もっと読む)

半導体装置

【課題】半導体膜の厚みを適当な範囲に制御することによって、大きいドレイン電流を有するとともに、所望の電気的特性を備える半導体装置を提供する。

【解決手段】半導体装置は、主表面1aを有するガラス基板1と、主表面1a上に設けられ、チャネル領域11と、チャネル領域11の両側に位置するソース領域9およびドレイン領域13とが形成されたポリシリコン膜7と、ポリシリコン膜7に接触するように設けられたゲート絶縁膜17と、ゲート絶縁膜17を介してチャネル領域11に向い合う位置に設けられたゲート電極21とを備える。ポリシリコン膜7は、50nmを超え150nm以下の厚みを有する。ソース領域9およびドレイン領域13は、ポリシリコン膜7の頂面7aからポリシリコン膜7の底面7cにまで達して形成されている。

(もっと読む)

薄膜トランジスタ表示板の製造方法およびこれに使用されるネガティブフォトレジスト組成物

【課題】パターンの不良が減少した薄膜トランジスタ表示板の製造方法およびこれに使用されるネガティブフォトレジスト組成物を提供する。

【解決手段】基板上に導電性物質からなる導電膜を形成する段階と、導電膜上にネガティブフォトレジスト組成物からなるエッチングパターンを形成する段階と、エッチングパターンをエッチングマスクとして利用して導電膜をエッチングし、導電膜パターンを形成する段階とを含み、ネガティブフォトレジスト組成物は、アルカリ現像液に溶解性を有するヒドロキシル基を含有するノボラック樹脂10〜50重量部、第1光酸発生剤(特定構造のスルホニルオキシイミド化合物)0.5〜10重量部、第2光酸発生剤(第1光酸発生剤とは構造の異なる特定構造のスルホニルオキシイミド化合物)0.5〜10重量部、架橋結合剤1〜20重量部および溶媒10〜90重量部を含む。

(もっと読む)

半導体装置の製造方法

【課題】ダイシング後にパッドの表面に接続される金属物の密着性を改善することができ

る半導体装置の製造方法を提供する。

【解決手段】半導体装置1の製造方法において、半導体基板10の上方の層間絶縁膜36

上に金属パッド40を形成する工程と、酸素含有雰囲気内において熱処理を行い、金属パ

ッド40の表面にアルミニウム又はアルミニウム合金を有する金属酸化膜41を形成する

工程と、半導体基板10を分割してチップを形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】強誘電体キャパシタを備えた半導体装置の歩留まりを改善することが可能な半導体装置の製造方法を提供すること。

【解決手段】シリコン基板20の上方に第1層間絶縁膜31を形成する工程と、第1層間絶縁膜31の上に、下部電極41a、強誘電体材料よりなるキャパシタ誘電体膜42a、及び導電性酸化物よりなる上部電極43aをこの順に積層してなるキャパシタQを形成する工程と、キャパシタQを覆う第2層間絶縁膜54を形成する工程と、上部電極43aの上の第2層間絶縁膜54に、該上部電極43aが露出するホール54aを形成する工程と、ホール54a内に、上部電極43aと接続された導電性窒化物よりなる単層のグルー膜58をスパッタ法で形成する工程と、グルー膜58をアニールする工程と、ホール54a内のグルー膜58上に導電性プラグ59aを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

化合物半導体装置とその製造方法

【課題】ゲート電極の近傍での耐圧が高められた化合物半導体装置とその製造方法を提供すること。

【解決手段】SiC基板20と、SiC基板20の上に形成された電子走行層21と、電子走行層21の上に形成された電子供給層23と、電子供給層23の上に互いに間隔をおいて形成されたソース電極27a及びドレイン電極27bと、ソース電極27aとドレイン電極27bの間の電子供給層23上に形成され、SiC基板20に向かって狭径となる開口29bを備えた保護絶縁膜30と、開口29b内の電子供給層23上に形成されたゲート電極32とを有する化合物半導体装置による。

(もっと読む)

半導体装置及び当該半導体装置の作製方法

【課題】集積回路部上にアンテナを作り込んで設ける場合であっても、接続不良やコンタクト抵抗の増加を抑制することを課題とする。

【解決手段】基板上に第1の導電膜を有する集積回路部を形成し、集積回路部上に絶縁膜を形成し、絶縁膜上にアンテナとして機能する第2の導電膜を選択的に形成し、絶縁膜及び第2の導電膜に開口部を形成して第1の導電膜を露出させ、メッキ処理により開口部及び第2の導電膜の上面に第3の導電膜を形成することにより、第1の導電膜及び第2の導電膜とを電気的に接続する。

(もっと読む)

化合物半導体装置

【課題】電気的特性を維持しつつ接着強度が改善された化合物半導体装置を提供する。

【解決手段】化合物半導体からなる基板と、前記基板の裏面に設けられ、複数の開口部を有する裏面金電極と、を備え、前記複数の開口部はメッシュ状に設けられ、互いに最も近接している前記開口部を結ぶ直線は、前記基板の端面に形成されたへきかい面と非平行であることを特徴とする化合物半導体装置が提供される。

(もっと読む)

半導体装置

【課題】完全にシリサイド化されたシリサイド領域を一部に有する配線を形成する際、シリサイド領域と非シリサイド領域の境界に発生する空隙による断線のない半導体装置を提供する。

【解決手段】基板1上に形成されたポリシリコン配線12と、ポリシリコン配線12に対向して配置されたシリサイド配線13と間に、絶縁性の拡散防止膜5を配置する。そして、ポリシリコン配線12とシリサイド配線13を、金属膜9,10が埋め込まれたコンタクトホール20,21及び配線11により構成される接続構造体により電気的に接続する。シリサイド配線13の形成時に、ポリシリコン配線12からのシリコンの拡散が拡散防止膜5により防止されるので、ポリシリコン配線12及びシリサイド配線13間に空隙が発生しない。

(もっと読む)

GaAs集積回路装置およびその取付け方法

ガリウム砒素装置(11)は、GaAs基板(14)およびターゲット装置のパッド(16)との電気的な接地接点を作るための銅の接触層(21)を有する。銅の接触層は、ニッケルバナジウム(NiV)層などの拡散バリヤ層(23)を介してGaAs基板から分離される。酸化効果を減じるために、有機はんだ付け性保護剤が露出した銅をコーティングしてもよい。銅の接触層を堆積させるに先立って金または銅のシード層が堆積してもよい。銅の接触層(21)がコンタクトパッド(16)に直接はんだ付け(18)され、コンタクトパッドがあふれた接着剤の領域を必要とせずに、比較的小さく作られ得ることを示唆する。  (もっと読む)

(もっと読む)

21 - 40 / 46

[ Back to top ]