Fターム[5F033MM10]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | 側面 (77)

Fターム[5F033MM10]に分類される特許

1 - 20 / 77

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

半導体装置、及びその製造方法

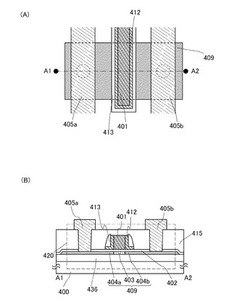

【課題】TSV付き半導体装置において、貫通孔側面すべてにバリア及びシード層を成膜しないことで、空隙の発生を防止する。

【解決手段】

第1の溝部、及び前記第1の溝部より水平断面積が小さい第2の溝部からなる凸状溝部を画成し、且つ、前記第1及び第2の溝部により両端を開口する貫通ビアホールが形成される半導体基板と、前記第1の溝部の内面から、前記第2の溝部の側面の一部まで被覆して、前記貫通ビアホールの側面に隆起するバリア層およびシード層と、前記シード層の表面上、及び、前記シード層で被覆されていない前記第2の溝部内部に形成されて、前記半導体基板の両表面から露出する電極と、を備える半導体装置が提供される。

(もっと読む)

磁気抵抗素子構造の製造方法

【課題】本発明は、磁気抵抗材料と集積回路とを巧みに統合することのできる、磁気抵抗素子構造の製造方法を提供する。

【解決手段】基板を提供する工程と、上記基板の上に金属ダマシン構造を形成する工程と、該金属ダマシン構造に電気的に接続するように該金属ダマシン構造の上にパターン化磁気抵抗ユニットを形成する工程とを含む、磁気抵抗素子構造の製造方法である。

(もっと読む)

優勢エッチング抵抗性を具備する低K誘電バリアを得る方法

【課題】低い誘電率、向上したエッチング抵抗性、優れたバリアパフォーマンスを具備する誘電バリアを形成する方法を提供する。

【解決手段】前駆物質を処理チャンバへ流すことと、前記前駆物質が、有機ケイ素化合物と炭化水素化合物の混合物を備えており、かつ、前記炭化水素化合物が、エチレン、プロピン、または、これらの組合わせを備え、前記半導体基板上に炭素−炭素結合を有する炭化ケイ素ベースの誘電バリア膜を形成するために、前記処理チャンバ内において前記前駆物質の低密度プラズマを生成することと、前記前駆物質中の前記炭素−炭素結合の少なくとも一部が、前記低密度プラズマ内に生き残り、かつ、前記誘電バリア膜内に存在し、制御された量の窒素を導入することにより、前記誘電バリア膜から炭素−炭素二重結合(C=C)、および/または、炭素−炭素三重結合(C≡C)を除去することと、を備える方法。

(もっと読む)

半導体装置及び半導体装置の形成方法

【課題】配線層間に絶縁物が堆積しない配線の形成方法を提供する。

【解決手段】半導体装置10は、第1絶縁体層14と、第1絶縁体層14上に間隔を空けて配置された複数の配線層18a、18bと、配線層18a、18bの側面上に形成された水素を吸蔵及び放出する水素吸蔵層19b、19c、19d、19eと、複数の配線層18a、18b上に、配線層間の溝20b上を跨ぐように形成された第2絶縁体層23と、を備えた配線を備える。

(もっと読む)

半導体装置の製造方法

【課題】 絶縁膜に、底面及び側面の形状を良好に保って配線溝を形成する技術が望まれている。

【解決手段】 基板の上に、仮のパターンを形成する。仮のパターンを囲むように、基板の上に層間絶縁膜を形成する。層間絶縁膜を形成した後、仮のパターンを除去する。仮のパターンが除去されることによって現れた凹部の側面及び底面に、第1のバリア膜及びシード膜を形成する。シード膜の上に、配線材料を堆積させることにより、凹部を配線材料で埋め込む。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の低抵抗化を図る。

【解決手段】本実施形態の半導体装置は、半導体基板10を覆う第1の層間絶縁膜上に設けられる配線60と、配線60の上面上に設けられるキャップ層68と、配線60と第2の層間絶縁膜との間に設けられるバリア膜62と、を含む。配線60は高融点導電層を含み、配線60の配線幅W1は、キャップ層68の幅W2よりも小さい。バリア膜62は、高融点導電層60が含む元素の化合物からなり、配線60を覆う層間絶縁膜69,70に起因する不純物が配線60内に拡散するのを抑制する。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】配線幅若しくは配線間隔の縮小に伴い、加工限界の制約を受けるために微細な配線形成が困難になりつつある。

【解決手段】絶縁層(第1の絶縁層12及び第2の絶縁層13)に溝15を形成し、導体膜(バリア膜16及び金属膜17)を溝15を埋設しない膜厚で形成し、続いて導体膜をエッチバックすることで溝15の側壁にサイドウォール状の配線18を形成することで、配線幅は導体膜の膜厚で制御できるために加工限界の制約を受けず、配線抵抗は配線高さを高くすることにより所定の配線抵抗を維持することができる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】基板上に設けられた層間絶縁膜40に開口部48を形成する工程と、開口部48の側面上および底面上、ならびに層間絶縁膜40上に第1金属材料からなる第1膜10を形成する工程と、第1膜10上であって、開口部48内および層間絶縁膜40上に、第1金属材料よりも電気陰性度が小さい第2金属材料からなる第2膜20を形成する工程と、第2膜20上に、第2金属材料よりも電気陰性度が小さい第3金属材料からなる第3膜30を形成する工程と、熱処理する工程と、開口部48外に位置する第1膜10および第2膜20、ならびに第3膜30を研磨によって除去する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

半導体装置

【課題】工程数の増大を抑制しつつ、チップ上に形成された再配線または突出電極の信頼性を向上させる。

【解決手段】配線2bおよびパッド電極2aが形成された半導体基板と、半導体基板上に形成された応力緩和層4と、応力緩和層4上に合金シード膜5を形成した後、応力緩和層4と合金シード膜5とを熱処理にて反応させることで、応力緩和層4と合金シード膜5との間に反応性バリア絶縁膜6を形成する。再配線8または突出電極は合金シード膜5上に形成する。

(もっと読む)

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線は、配線溝を有する絶縁膜13と、前記配線溝内の両側面の前記絶縁膜上に形成された第1触媒膜15と、前記配線溝内の両側面の前記第1触媒膜上に形成され、両側面に対して垂直方向に積層された複数のグラフェンシートで構成された第1グラフェン層16と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】スループット良く、銅を異方的にエッチングすることを可能とするとともに、銅を用いたバンプ電極を短時間で形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】内部配線153上に絶縁膜156を形成する工程と、絶縁膜156に内部配線153に通じる開口157を形成する工程と、開口157が形成された絶縁膜156上に、銅膜101を形成する工程と、銅膜101上に、バンプ電極形成パターンに対応したマスク材102を形成する工程と、マスク材102をマスクに用いて、銅膜101を異方的にエッチングし、バンプ電極を形成する工程と、とを具備する。

(もっと読む)

半導体装置

【課題】低抵抗かつ微細化が可能なグラフェン配線を有する半導体装置およびその製造方法を提供する。

【解決手段】一実施の形態によれば、半導体装置は、配線と前記配線に接続されるコンタクトプラグを有する。前記配線は、長さ方向の両側面に触媒層を有する基体と、前記基体の前記両側面上に前記触媒層と接して形成され、前記基体の前記両側面と垂直に積層された複数のグラフェンを有するグラフェン層を有する。

(もっと読む)

エッチング方法及びエッチングシステム

【課題】スループット良く、銅を、異方的にエッチングすることが可能なエッチング方法を提供すること。

【解決手段】 表面にマスク材102が形成された銅膜101に、マスク材102をマスクに用いて酸素イオン6を照射し、銅膜101内に、銅膜101の厚さ方向の全てに対して異方的に酸化された酸化銅103を形成する工程と、異方的に酸化された酸化銅103をエッチングする工程と、を具備する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 基板を薄くしてもその反りを防止するTSV構造の製造方法を提供する

【解決手段】本発明の半導体装置の製造方法は、半導体基板の表面に半導体素子を集積させて回路の少なくとも一部を形成する工程と、半導体基板の表面から穴を開ける工程と、穴の内表面に絶縁膜およびバリア膜を形成する工程と、バリア膜の表面に、穴を埋めるように導電性金属を形成する工程と、半導体基板の裏面を加工して厚さを減少させ、導電性金属を突出させる工程と、半導体基板の裏面にSiCN膜を設ける工程とを有する。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

半導体デバイス障壁層

【課題】本発明は、半導体デバイス要素のメタライゼーション及び誘電体材料の不活性化に使用される障壁層に関する。

【解決手段】半導体デバイスメタライゼーション要素用の障壁層は、要素くぼみ中に形成されたシリコン窒化物薄膜とシリコン窒化物薄膜上に形成された耐熱性金属薄膜を供する。デバイス要素は誘電体材料及び誘電体中に形成されたくぼみを含む。くぼみ内の誘電体材料の表面は、制御されたパラメータ下で窒素に露出される。くぼみの内部に隣接した誘電体材料の部分は、シリコン窒化物に変換される。

耐熱性金属は次に、くぼみの側壁に沿って、適合して堆積される。次に、耐熱性金属薄膜上にシード層が堆積され、次にくぼみ内に導電性金属が堆積される。次に、くぼみの外の過剰の金属を除去し、デバイスを平坦化するため、デバイスを研磨する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、バリアメタルの絶縁膜及びCuに対する密着性と、Cu拡散防止とを両立する。

【解決手段】 第1絶縁膜に設けた凹部の側壁に第2絶縁膜を形成し、第2絶縁膜の内側に順に第2絶縁膜との密着性が優れている第1の導電性バリア層、炭素を含有する第2の導電性バリア層、及び、Cu系埋込電極との密着性が優れている第3の導電性バリア層の3層構造のバリア層を介してCu系埋込電極を設けるとともに、前記第1の導電性バリア層と前記第2の導電性バリア層との界面と、前記第2の導電性バリア層と前記第3の導電性バリア層との界面に炭素混合領域を設ける。

(もっと読む)

1 - 20 / 77

[ Back to top ]