Fターム[5F033MM13]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | バリア層を含むもの (2,960)

Fターム[5F033MM13]に分類される特許

461 - 480 / 2,960

半導体装置の製造方法及び半導体装置

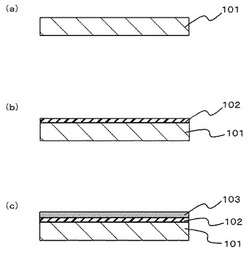

【課題】素子の信頼性を劣化させることなく、より比誘電率の低い絶縁膜を形成する。

【解決手段】この半導体装置の製造方法は、下地膜101に、環状シロキサンをプラズマ重合させて第一の絶縁膜102を形成する工程と、第一の絶縁膜102を形成する工程の後、連続的に、第一の絶縁膜102上に、環状シロキサンをプラズマ重合させて第二の絶縁膜103を形成する工程と、を含む。第一の絶縁膜102の成膜速度は、第二の絶縁膜103の成膜速度よりも遅い。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ロジック回路のコンタクト抵抗の増加を抑制しつつ、メモリ回路のキャパシタ容量を最大限に高めることが実現される半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置においては、ロジック回路を構成する配線を有する配線層の層数をMとし、メモリ回路を構成する配線を有する配線層の層数をNとしたとき(MおよびNは自然数であって、M>N)、(M−N)層あるいは(M−N+1)層の配線層にわたって、容量素子150が設けられている。

(もっと読む)

配線基板の製造方法

【課題】スループットが向上し、且つ少ない液滴量でも第1の電極と第2の電極とを導通性を確保する。

【解決手段】基体10の表面10aに形成された微細穴2の底部2aとなる下面電極3と、基体10の表面10aであって微細穴2の内壁部2bの上端近傍に配置された上面電極5とを導通させる導電層12を形成する。この導電層12の形成において、まず、金属ナノ粒子11を分散させるためのクリアインク8を微細穴2に充填する。次に、微細穴2に金属ナノ粒子11を含有する液滴を供給し、金属ナノ粒子11を微細穴2内のクリアインク8で分散させる。次に、微細穴2内のクリアインク8を揮発させることで、微細穴2の底部2a及び内壁部2bに析出した金属ナノ粒子膜11Aを有する導電層12を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】MIM容量素子形成時に生じる異常放電による容量絶縁膜の絶縁破壊を抑えることができて、高容量密度のMIM容量素子を得る。

【解決手段】半導体基板2上に、下部電極4−容量絶縁膜5−上部電極6からなるMIM容量素子1を有する半導体装置であって、上部電極4を構成する上部電極用金属膜は容量絶縁膜5との界面が、有機金属気相成長法(MOCVD)によりプラズマを用いないで堆積したアモルファス状のTiN膜などの金属窒化膜で構成されている。

(もっと読む)

表示装置およびその製造方法

【課題】ゲート絶縁層内に拡散する汚染元素によってトランジスタ特性が低下するのを防止した薄膜トランジスタを有する表示装置、および、その製造方法を提供することを目的とする。

【解決手段】基板101の上側に積層された半導体層104と、半導体層104の上側に積層されるゲート電極106と半導体層104とゲート電極106との間に積層されるゲート絶縁層105と、ソース電極112およびドレイン電極111と、を含む薄膜トランジスタを有する表示装置であって、ソース電極112およびドレイン電極111の少なくとも一方は、ゲート絶縁層105の上側に形成されて、ゲート絶縁層105に形成されるコンタクトホール109を介して半導体層に接続され、コンタクトホール109の側壁には、窒素化合物を含む側壁膜110が形成される、ことを特徴とする表示装置。

(もっと読む)

薄膜の製造方法

【課題】本発明は、薄膜材料となる微粒子を分散した液体を、被処理部材の表面に塗布して薄膜を製造する方法であって、均一な薄膜を製造する方法の提供を目的とする。

【解決手段】金属または半導体を含む薄膜の製造方法であって、溝(または凹部)4を有する被処理部材10の表面に、金属の微粒子、半導体の微粒子、金属の酸化物を含む微粒子、および半導体の酸化物を含む微粒子、のうちの少なくともいずれかを溶媒中に分散した液体8を塗布する塗布工程と、被処理部材10の表面に塗布した液体8の溶媒を揮発させる第1の熱処理工程と、マイクロ波を照射することにより、溶媒を揮発させた液体8に分散された微粒子を加熱し、液体8に含まれる微粒子または液体8に含まれる微粒子の成分で溝(または凹部)4を埋める第2の熱処理工程と、を備えたことを特徴とする薄膜の製造方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】配線間のショートを抑制すること。

【解決手段】半導体基板10上に第1絶縁膜20を形成する工程と、前記第1絶縁膜の上面を研磨する工程と、研磨された前記第1絶縁膜に接続30孔を形成する工程と、前記接続孔の内面および前記第1絶縁膜上に前記第1導電層32を形成する工程と、前記接続孔内の前記第1導電層上に第2導電層34を形成する工程と、前記第1絶縁膜上の前記第1導電層を研磨し前記第1絶縁膜の上面を露出させる工程と、前記第2導電層のエッチングレートより前記第1導電層のエッチングレートが大きいエッチャントを用い、前記接続孔内上部の前記第1導電層をエッチングする工程と、前記絶縁膜上に配線層50を形成する工程と、を含む半導体装置の製造方法。

(もっと読む)

薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法

【課題】接着層の厚さを増加させることなく、銅の下部層との接着性が向上し、銅が下部層に拡散することを防止することができる薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法を提供する。

【解決手段】本発明の薄膜形成方法は、基板上にスパッタリング方法により薄膜を形成する方法であって、薄膜は、電力密度が1.5〜3W/cm2、非活性気体の圧力が0.2〜0.3Paで形成する。薄膜は、非晶質構造を有することができ、チタニウム、タンタル、又はモリブデンのうちのいずれか一つで形成することができる。

(もっと読む)

半導体装置の製造方法

【課題】ビア等となる開口内への金属の埋設において、ボイドの発生を抑制することを課題とする。

【解決手段】基板上に形成された第2のp−SiCOH膜204の直上に、ハードマスクとしてTiN膜205を形成する工程と、フォトリソグラフィーとエッチングにより、TiN膜205および第2のp−SiCOH膜204を貫く開口を形成する工程と、前記開口内を洗浄する工程と、前記洗浄工程の後、TiN膜205を除去する工程と、TiN膜205を除去後、第2のp−SiCOH膜204の直上に、前記開口を埋める第2の金属膜214を形成する工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】 組み立て工程やCMP工程時における剥離を抑制した、低誘電率層間絶縁膜の製造方法とそれを用いた半導体装置を提供する。

【解決手段】低誘電率層間絶縁膜の成膜の際、高周波と低周波の2周波を切り替え、膜厚方向に膜特性の変調をかけることで、低誘電率を保持したまま密着強度を向上させる。プラズマ発生のための高周波と低周波が同一電極から印加される。そして絶縁膜の成膜開始時あるいは成膜終了時の少なくとも一方において、低周波の入力が成膜開始時及び成膜終了時を除いた他のタイミングより高い。例えば絶縁膜は、厚さ方向における少なくともどちらか一方の端部が、高周波と低周波の2周波により密着層となり、密着層以外の部分は低周波の入力を低下あるいは0にすることで低誘電率絶縁膜となる。

(もっと読む)

半導体装置とその製造方法、及び半導体ウエハ

【課題】半導体装置とその製造方法、及び半導体ウエハにおいて、個片化後の半導体チップがもとの半導体ウエハのどこに位置していたかを容易に特定すること。

【解決手段】複数のチップ領域Rcとスクライブ領域Rsとを有するシリコン基板20と、複数のチップ領域Rcの各々に対応する複数のモニタ素子Mと、スクライブ領域Rsに形成され、複数のモニタ素子Mの各々を電気的に接続する配線2とを有し、スクライブ領域RsにおけるダイシングラインX1〜X7、Y1〜Y7の位置をずらしたときに、配線2の異なる部分がダイシングされるようにして、配線2と複数のモニタ素子Mとの結線状態をダイシングラインX1〜X7、Y1〜Y7の位置に応じて可変にした半導体ウエハWによる。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁層のコンタクトホールに埋め込まれたコンタクトプラグを介して上層側の金属配線層と下層側の金属配線層とを電気的に接続する際の接続抵抗を低減する。

【解決手段】第2の層間絶縁層の上に少なくともコンタクトホールを形成する位置に開口部を有するレジスト層を形成する工程S1−4と、レジスト層を用いて第2の層間絶縁層をパターニングすることによって、第2の層間絶縁層を貫通するコンタクトホールを形成する工程S1−5と、コンタクトホールの内部に付着したポリマーを含む残渣をスチーム酸化によって除去する工程S1−7とを有する。

(もっと読む)

半導体装置の製造方法

【目的】ウェット処理を行った場合でも絶縁膜上に庇形状が形成されない半導体装置の製造方法を提供する。

【構成】本発明の一態様の半導体装置の製造方法は、基板上に絶縁膜を形成する工程(S102)と、絶縁膜上に保護膜を形成する工程(S104)と、保護膜に第1の開口部を形成する工程(S114)と、第1の開口部内に保護膜よりもウェットエッチングレートが大きい犠牲膜を形成する工程(S116)と、第1の開口部内の犠牲膜に第1の開口部よりも幅の狭い第2の開口部を形成する工程(S122の一部)と、第2の開口部を転写することで絶縁膜に第3の開口部を形成する工程(S122の一部)と、第3の開口部が形成された後に、ウェット処理を行なう工程(S126)と、ウェット処理後に、第3の開口部内にバリアメタル膜を形成する工程(S128)と、第3の開口部内に導電性材料を埋め込む工程(S132)と、を備えたことを特徴とする。

(もっと読む)

表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】表示装置の形成方法は、基板上に下地絶縁層を設け、その層上に配線パターンに沿った第1の銅拡散防止層を設ける。次に、その第1の銅拡散防止層上面に第1の銅拡散防止層の幅より僅かに狭い銅配線層を積層し、銅配線層の全表面を覆うように、第2の金属拡散防止層を設ける方法である。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜のストレスに耐え、絶縁膜からの酸素や水分の影響を抑制しつつ、エレクトロマイグレーションの耐性や配線間の耐圧も改善することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、(a)凹部102が形成された絶縁膜101上に、TaN膜103を成膜する工程と、(b)TaN膜103上に、Taよりも熱膨張係数が大きいTiを主成分とするTi膜104を成膜する工程と、(c)Ti膜104上に、Tiよりも熱膨張係数が大きいCuを主成分とするCu膜105を成膜する工程と、(d)Cuを、電解めっきにより、凹部102内に埋め込む工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】配線幅の拡大の阻止を図ることができる半導体装置の製造方法を提供する。

【解決手段】基板上に層間絶縁膜を形成する工程と、前記層間絶縁膜に配線溝を形成する工程と、前記配線溝に配線を形成する工程とを具備し、前記配線溝を形成する際に、前記配線溝内に酸素ラジカルを吸収する酸素ラジカル吸収物質を形成する(ステップS104)。

(もっと読む)

半導体装置の製造方法

【課題】配線密度の高い領域に発生するエロージョンを抑えることのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、配線8aおよび配線8aよりもパターンの密度が低い配線8bを、第1の絶縁膜3中の高密度領域4aおよび低密度領域4bにそれぞれ形成する工程と、第1の絶縁膜3の高さを下げて配線8a、8bの上部10a、10bを露出させる工程と、低密度領域4bにおける上面の最低高さが配線8a、8bの上面の高さよりも低くなるように、第1の絶縁膜3の上面、および上部10a、10bの表面を覆う第2の絶縁膜11を形成する工程と、第2の絶縁膜11上に第3の絶縁膜12を形成する工程と、配線8a、8b、および第3の絶縁膜12の研磨レートが第2の絶縁膜11の研磨レートよりも高い条件の下で第3の絶縁膜12、第2の絶縁膜11、配線8a、8bを研磨して平坦化させる工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】微細配線を有する半導体装置を高信頼性及び高歩留まりで得る。

【解決手段】この半導体装置の製造方法は、下層配線を形成する工程(ステップS101)と、下層配線上に絶縁膜を形成する工程(ステップS102)と、絶縁膜上にレジストを形成する工程(ステップS103)と、レジストをマスクとしてドライエッチングにより下層配線を露出する開口部を形成する工程(ステップS104)と、開口部を洗浄液を用いて洗浄する工程(ステップS105)と、洗浄した開口部をリンスする工程(ステップS106)と、含む。ステップS106では、リンス液と還元性ガスとを二流体ノズルから吐出して、開口部の底部をリンスする。

(もっと読む)

半導体装置の製造方法

【課題】配線間のリーク電流が発生することを抑制し、配線間容量の増大を抑制する。

【解決手段】半導体装置100の製造方法は、絶縁膜2にダマシン配線を形成する工程(A)を含む半導体装置100の製造方法であって、基板1上に形成された絶縁膜2の表面にプラズマ処理を行い、絶縁膜2中の水分を脱離する工程(B)と、シリル化ガスを含む雰囲気中でアニール処理を行い、絶縁膜2をシリル化する工程(C)と、を含む。

(もっと読む)

461 - 480 / 2,960

[ Back to top ]