Fターム[5F033MM13]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | バリア層を含むもの (2,960)

Fターム[5F033MM13]に分類される特許

441 - 460 / 2,960

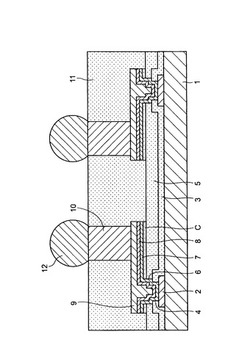

半導体装置の製造方法

【課題】 シリコン基板上にポリイミドなどからなる保護膜が形成された半導体装置の製造中に、保護膜の上面層が変質しても、この変質による悪影響が生じないようにする。

【解決手段】 ポリイミドなどからなる保護膜5に開口部6を形成したとき、保護膜5の開口部6を介して露出された接続パッド2の上面にポリイミドなどからなる残渣が残存する場合がある。そこで、次に、この残渣を酸素プラズマアッシングにより除去する。この場合、保護膜5の上面側に凸凹構造の変質層Aが形成される。次に、開口部4、6を介して露出された接続パッド2の上面に形成された自然酸化膜をアルゴンプラズマエッチングにより除去する。この場合、変質層Aがさらに変質して網目構造の変質層Cが形成される。次に、チタンなどからなる第1の下地金属層7を成膜する。この場合、第1の下地金属層7は網目構造の変質層Cの上面に成膜されるため、その界面の密着力は高い。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ディッシングを抑制することができる半導体装置の構造を実現する。

【解決手段】半導体装置200は、基板(シリコン基板)と、基板上に設けられた絶縁層(層間絶縁膜201)と、層間絶縁膜201に設けられた第1の配線溝と(配線溝202)、配線溝202に埋め込まれた第1の金属膜(Cuめっき膜206)と、を備え、配線溝202の底部が、凸部形状を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】高容量・高精度なMIM静電容量素子を少ない工程で製造する技術を提供する。

【解決手段】第1層間絶縁膜17上に静電容量素子の下部電極21と第2層配線22とを同時に形成した後、第1層間絶縁膜17上に堆積した第2層間絶縁膜24に開口部34を形成する。次に、開口部34内を含む第2層間絶縁膜24上に順次堆積した容量絶縁膜27、第2金属膜および保護金属膜29を順次堆積し、第2層間絶縁膜24上の保護金属膜29、第2金属膜および容量絶縁膜27をCMP法で研磨・除去することによって、開口部34内に容量絶縁膜27、第2金属膜からなる上部電極28および保護金属膜29を残す。

(もっと読む)

低水分誘電体膜を形成する方法

酸化表面層のハイブリッドその場ドライクリーニングプロセス

【課題】 集積回路における酸化表面層の洗浄を行うための新しいドライクリーニングプロセスの提供。

【解決手段】 一の実施例によると、当該方法は、酸化表面層を有する金属含有バリア層を含む基板を供する工程、前記酸化表面層を活性化させるために、プラズマ励起されたアルゴン気体を含む第1処理気体流へ前記酸化表面層を曝露する工程、及び、前記の第1処理気体流へ酸化表面層を曝露する工程中に基板バイアス電力を印加する工程を有する。当該方法は、非プラズマ励起された水素気体を含む第2処理気体へ前記の活性化した酸化表面層を曝露する工程をさらに有する。前記の第1処理気体流へ酸化表面層を曝露する工程は、前記酸化表面層を活性化させるのに加えて、水素気体を含む前記第2処理気体による、前記活性化した酸化表面層の還元を助ける。前記金属含有バリア層の厚さは、ハイブリッドその場ドライクリーニングプロセスによって実質的には変化しない。

(もっと読む)

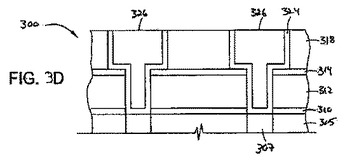

半導体処理システムのための前駆物質を生成する方法及び装置

【課題】半導体処理システム(320)の前駆物質を生成する装置を提供する。

【解決手段】装置は、側壁(402)、上部、底部を有するキャニスタ(300)を含んでいる。キャニスタ(300)は、上の領域(418)と下の領域(434)を有する内容積(438)を画成している。一実施形態においては、装置は、更に、キャニスタ(300)を部分的に取り囲んでいるヒータ(430)を含んでいる。ヒータ(430)によって、上の領域(418)と下の領域(434)間に温度勾配が生じる。また、精製ペンタキス(ジメチルアミド)タンタルから原子層堆積によってバリヤ層、例えば、窒化タンタルバリヤ層を形成する方法も特許請求される。

(もっと読む)

成膜方法、プログラム及びコンピュータ記憶媒体

【課題】基板の所定の位置に高い位置精度で膜を形成する。

【解決手段】電極形成用テンプレート112の表面112aには、ウェハWの貫通孔に対応する位置に開口部115が複数形成されている。電極形成用テンプレート112は、開口部115に連通する膜形成用液の流通路116を備えている。この電極形成用テンプレート112とウェハWを密着させた後、この状態のまま、めっき液供給口117から流通路116を介して開口部115からウェハWの貫通孔に対してめっき液を供給することで、ウェハWの貫通孔に電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の微細化に対処しうる、製造が容易で安価な低コンタクト抵抗の半導体装置およびその製造方法を得る。

【解決手段】Si基板(1)上の不純物領域(7)を覆うように層間絶縁膜(8)が形成され、その層間絶縁膜(8)には、層間絶縁膜(8)を貫通して不純物領域(7)を掘り込むようにコンタクトホール(9)が形成されている。コンタクトホール(9)内には、金属膜(10)、バリア層(11)、金属シリサイド(12)およびソース、ドレイン配線(14)が形成されている。ソース、ドレイン配線(14)は、タングステンから形成されている。

(もっと読む)

半導体装置

【課題】 パッド内での過度の電流集中を抑制することが可能なパッド構造を有する半導体装置を提供する。

【解決手段】 半導体基板の上に、絶縁性材料からなる第1の絶縁膜が形成されている。第1の絶縁膜の上に、導電材料からなるパッド部が形成されている。パッド部に電気的に連続し、第1の幅W1を有する配線部が形成されている。第1の絶縁膜の上であって、パッド部の外周線から第2の幅W2より内側の第1の領域に、複数の第2の絶縁膜が配置されている。配線部とパッド部との境界線に最も近い第2の絶縁膜を連ねる直線のうち、配線部をパッド部内に延長した領域と重なる部分が、パッド部の導電材料と交差する長さをL3としたとき、W1≦2×W2+L3を満たす。

(もっと読む)

スパッタリング用ターゲットおよび半導体装置の製造方法

【課題】スパッタリング用ターゲットから垂直方向に叩き出されるターゲット原子の個数を増大させる。

【解決手段】薄膜形成に用いられるターゲット原子Pから構成されたターゲット5において、ターゲット5から斜め方向に叩き出されたターゲット原子Pを側壁に衝突させることでターゲット原子Pがターゲット5から放出されるのを遮る凹部5aを表面に形成する。

(もっと読む)

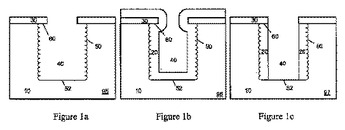

ビア及びエッチングされた構造におけるコンフォーマル絶縁層の形成方法及びパターン形成方法

マスク層の下にアンダーカット形状を形成するエッチングプロセスによって基板にビアが形成される。ビアはコンフォーマルな絶縁層で覆われ、この構造にエッチングプロセスを実施して水平面から絶縁層を取り除くと共にビアの垂直な側壁の絶縁層を残す。ビアの上部領域はエッチバックプロセスの際、アンダーカットハードマスクによって保護される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】マイクロローディング効果を防止しながら、上層配線となる金属配線のレイアウト制約のない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極4と、半導体基板1に形成された拡散層5と、半導体基板1の上に形成された絶縁膜7及び絶縁膜8と、絶縁膜及び絶縁膜8を貫通するホール9Dに埋め込まれ、側面を絶縁膜11で覆われた金属材料からなるプラグ12と、絶縁膜8を貫通しないホール10Bに埋め込まれ、絶縁膜11からなる絶縁体10Cと、絶縁膜8の上に形成され、プラグ12と電気的に接続する金属配線13Bとを備えている。

(もっと読む)

マンガン含有低誘電率膜及びその製造方法、半導体装置の製造方法並びに成膜装置

【課題】マンガン含有材料を利用して、低誘電率膜への銅の拡散を防止する。

【解決手段】成膜装置100では、制御部70の制御に基づき、処理容器1内を真空にして、ヒーター6によりウエハWを加熱しつつ、シャワーヘッド11のガス吐出孔13a,13bからウエハWへ向けて低誘電率材料とマンガン含有材料とを含む成膜ガスを供給する。高周波電源23からシャワーヘッド11に高周波電力を供給することにより、成膜ガスを解離させ、処理容器1内に成膜ガスのプラズマを生成させる。このプラズマによって、ウエハWの表面にMnを含有するSiCOH膜を成膜する。

(もっと読む)

半導体装置およびその製造方法

【課題】 デュアルダマシン法による配線構造の製造において、接続プラグ用のホールを通じて下層配線の表面に凹部をエッチング形成するとき、上層配線用の溝の底部が過剰エッチングされないようにする。

【解決手段】 TaNなどからなり、接続プラグに対応する開口を有する導電性膜パターン112をSiOCなどからなる層間絶縁膜111と113との間に設けた後、配線溝114、ホール115を形成する。次にTaN、Taなどからなる積層導電性膜116を堆積し、ホール115の底部の積層導電性膜116を除去し、さらに下層配線を構成するCu膜109を掘り込むエッチングを行う。このとき、導電性膜パターン112があるために配線溝114の底部の下にある層間絶縁膜111のエッチングを防止できる。その後、配線溝114およびホール115内にCuなどの導電性膜117を埋め込む。

(もっと読む)

半導体装置及びその製造方法

【課題】ポーラス絶縁層を用いた半導体装置において、当該ポーラス絶縁層を覆うポアシール絶縁層を良好に形成すること。

【解決手段】本発明に係る半導体装置の製造方法は、(A)ポーラス絶縁層の表面にトレンチを形成する工程と、(B)ビニル基を含み−Si−O−を含む構造を備える化学物質を、ポーラス絶縁層の表面上あるいはポーラス絶縁層中に導入する工程と、(C)当該化学物質の重合を行うことにより、ポーラス絶縁層よりも高密度のポアシール絶縁層をトレンチの表面上に形成する工程と、を含む。

(もっと読む)

プラズマ化学気相堆積による、有機官能基と共にシリコンを含有するハイブリッド前駆体を使用する超低誘電材料

低誘電率層を基板上に堆積するための方法が提供される。一実施形態では、本方法は、1種または複数のオルガノシリコン化合物をチャンバに導入するステップであって、1種または複数のオルガノシリコン化合物がシリコン原子およびこのシリコン原子に結合されたポロゲン成分を含むステップと、1種または複数のオルガノシリコン化合物を、RF電力の存在下で反応させることにより、低誘電率層をチャンバ内の基板上に堆積させるステップと、低誘電率層からポロゲン成分が実質的に除去されるようにこの低誘電率層を後処理するステップとを含む。任意選択で、不活性キャリアガス、酸化ガス、またはその両方を、1種または複数のオルガノシリコン化合物と共に処理チャンバ内に導入してもよい。後処理プロセスは、堆積した材料の紫外線硬化とすることができる。UV硬化プロセスは、熱または電子ビーム硬化プロセスと同時にまたは連続して使用してもよい。低誘電率層は、良好な機械的性質および望ましい誘電率を有する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】製造コストの増加および歩留まりを低下させることなく、配線抵抗を下げることのできる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板100上の絶縁膜104上にマスク材料膜106を形成した後、第1のトレンチ形成用開口と第2のトレンチ形成用開口とを有するマスクパターン109をマスク材料膜106に形成する工程と、マスク材料膜106上に、第1のトレンチ形成用開口を露出する第3のトレンチ形成用開口112を有し、且つ、第2のトレンチ形成用開口部を覆うレジストパターン113を形成する工程と、レジストパターン113及びマスクパターン109を用いて、絶縁膜104内に第1のトレンチ115を形成する工程と、レジストパターン113を除去した後、マスクパターン109を用いて、絶縁膜104内に第2のトレンチを形成する工程とを備えている。

(もっと読む)

絶縁膜、積層体、半導体装置および半導体装置の製造方法

【課題】誘電率が低く、半導体装置の製造に適用した際に絶縁不良等の問題を生じにくい絶縁膜を提供すること。

【解決手段】本発明の絶縁膜は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む組成物を用いて形成されたものであって、フッ素系ガスでエッチングした際のエッチングレートが、SiO膜の0.75倍以下であることを特徴とする。前記重合性反応基は、芳香環と、当該芳香環に直接結合するエチニル基またはビニル基とを有するものであり、前記重合性化合物において、前記芳香環由来の炭素の数は、当該重合性化合物全体の炭素の数に対して、15%以上、38%以下であるのが好ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】低容量且つ高温特性が良好な素子分離領域を有する高速なMIS電界効果トランジスタを提供する。

【解決手段】半導体基板1にウエル領域2が設けられ、ウエル領域2内には上部、下部及び側面にシリコン酸化膜3を有し、内部が空孔4に形成されたトレンチ素子分離領域が選択的に設けられ、トレンチ素子分離領域により画定されたウエル領域2が設けられた半導体基板1上にゲート酸化膜9を介してゲート電極10が設けられ、ゲート電極10の側壁にサイドウォール11が設けられ、ウエル領域2が設けられた半導体基板1には、ゲート電極10に自己整合して低濃度のソースドレイン領域(6、7)及びサイドウォール11に自己整合して高濃度のソースドレイン領域(5、8)が設けられ、高濃度のソースドレイン領域にはそれぞれバリアメタル14を有する導電プラグ15を介してバリアメタル17を有する配線18が接続されている構造からなるMIS電界効果トランジスタ。

(もっと読む)

表示装置の作製方法

【課題】液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。

【解決手段】液滴吐出法による液滴の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させる。

(もっと読む)

441 - 460 / 2,960

[ Back to top ]