Fターム[5F033NN17]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクト部の配線構造の特徴 (690) | 接触構造 (642) | 介在層の一部を除去するもの (93)

Fターム[5F033NN17]に分類される特許

1 - 20 / 93

半導体回路装置およびその製造方法

【課題】ビアヒューズ素子の径を小さくし、ビアヒューズ素子を低電流で溶断することが可能な半導体回路装置およびその製造方法を提供する。

【解決手段】一方向に配置された複数の配線層と、前記複数の配線層のうちの少なくとも2つの前記配線層の間に設けられたビアヒューズ素子と、前記複数の配線層の配置方向に直交する平面内において前記ビアヒューズ素子に隣接する穴と、前記穴内に設けられた貫通ビアとを備えた半導体回路装置。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホールの側壁に制御性良く傾斜を形成することで、コンタクトプラグにボイドが形成されることを抑制する。

【解決手段】絶縁膜10に第1のコンタクトホール(破線部)を形成する工程と、第1のコンタクトホールの内壁を構成する絶縁膜の上方ほどエッチング量が多くなるケミカルドライエッチングを施して内壁が傾斜した第2のコンタクトホール13を形成する工程と、第2のコンタクトホール内にコンタクトプラグを形成する工程とを有する。

(もっと読む)

電子装置およびその製造方法

【課題】信頼性の高いコンタクト構造を提供する。

【解決手段】電子装置は第1の絶縁膜と、前記第1の絶縁膜の表面に形成された配線溝と、Cuよりなり前記配線溝を充填する配線パタ―ンと、前記配線パタ―ンの表面に形成され、Cuよりも大きな弾性率を有する金属膜と、前記第1の絶縁膜上に形成された第2の絶縁膜と、Cuよりなり、前記第2の絶縁膜中に形成され、前記金属膜とコンタクトするビアプラグと、を備える。

(もっと読む)

半導体装置とその製造方法

【課題】 実施形態は、製造工程が簡便な手法によって製造した半導体装置を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、実施形態にかかる半導体装置は、基板と、基板上に触媒金属膜と、触媒金属膜上にグラフェンと、前記グラフェン上に層間絶縁膜と、前記層間絶縁膜を貫通するコンタクトホールと前記コンタクトホールにカーボンナノチューブを水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した前記触媒金属膜上に又は前記層間絶縁膜を貫通するカーボンナノチューブを水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した前記触媒金属膜上に備えることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ワイヤがCuワイヤであっても、ボンディング時の衝撃による金属のスプラッシュを抑制する。

【解決手段】半導体装置は、電極パッド103を有する半導体チップと、電極パッド103にボンディングされたワイヤ(例えばCuワイヤ105)と、を有している。電極パッド103において、ワイヤがボンディングされている領域の少なくとも表層はルテニウム又は酸化ルテニウムにより構成され、その表層の膜厚は20nm以上である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】デュアルダマシン法を用いて層間絶縁膜内にCu配線を形成する際、硬度が低い層間絶縁膜および硬度が高い層間絶縁膜のそれぞれに形成されたビアホール内に配線材料を良好に埋め込むことができるようにする。

【解決手段】第2層間絶縁膜17には、配線溝30aとビアホール28aとが形成されている。また、ビアホール28aの開口部には、第2層間絶縁膜17を斜め下方に後退(リセス)させることによって、テーパ状の断面形状を有するリセス部31が形成されている。これにより、ビアホール28aの開口部の直径は、開口部よりも下方の領域の直径に比べて大きくなり、ビアホール28aの直径が微細な場合であっても、ビアホール28aの内部に配線材料を良好に埋め込むことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】絶縁膜に発生するクラックを抑制できる技術を提供する。

【解決手段】実施の形態におけるパッド構造では、単に電極層OPM1の周縁部が、平面視において、パッドPAD1の周縁部よりも内側に位置する(図8ではパッドPAD1の周縁部と絶縁膜PASに形成された開口部OP1の端部との間に位置する)ように電極層OPM1を形成するだけでなく、図8に示すように、パッドPAD1の厚さをAとし、絶縁膜PASの厚さをBとし、開口部OP1内から絶縁膜PASの端部(開口部OP1の周囲)上にはみ出す電極層OPM1のはみ出し量をCとし、電極層OPM1の厚さをDとした場合に、B≒D(図8ではB<D)を前提として、A<Bの関係を成立させることにより、B>Cの関係を成立させている。これにより、絶縁膜PASにクラックが発生することを防止できる。

(もっと読む)

開口部の形成方法及び半導体装置の作製方法

【課題】少なくともフォトマスクの枚数を増加させることなく、積層構造の下部の導電層が露出するように該導電層上の絶縁膜に対する開口部の形成方法を提供する。

【解決手段】開口部が設けられる部分の積層構造の下部の導電層を、該開口部を形成するフォトマスクと同一のフォトマスクを用いて形成されたエッチングマスクにより予め露出させ、その後保護絶縁膜を形成し、前記積層構造の上部の導電層が開口部において露出されないように、保護絶縁膜に開口部を形成する。このような開口部の形成方法は、半導体装置の作製方法に適用することができる。

(もっと読む)

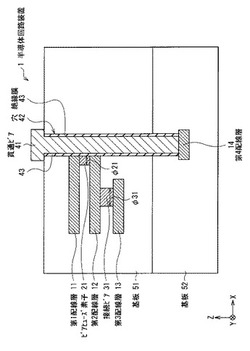

貫通配線基板の製造方法及び貫通配線基板

【課題】貫通孔の底面部付近において、導電層をカバレッジ良く形成し、接触不良がなく、電気的な安定性を向上させた貫通配線を、工程やコストを増加することなく形成する。

【解決手段】半導体基板の一方の面に第一絶縁層を介して導電部を形成する第一工程、ドライエッチング法により半導体基板の他方の面側から第一絶縁層が露呈するように貫通孔を形成する第二工程、貫通孔の内壁面および底面に第二絶縁層を形成する第三工程、第二絶縁層及び第一絶縁層のうち貫通孔の底面に位置する部分を除去し導電部を露呈する第四工程、第二絶縁層上に導電層を形成し該導電層を導電部と電気的に接続する第五工程、を有し、第四工程において、第二絶縁層に続いて導電部の一部をエッチングすると共に、エッチングにより除去された第一金属成分とエッチングガス成分とからなる第一副生成物を、貫通孔の底面部及びその近傍に位置する内壁面部に堆積させ、テーパー部を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】容量素子の良好な特性と高い信頼性を実現することが可能な半導体装置を提供する。

【解決手段】半導体基板上に第1の絶縁膜を介して形成されている下部電極と、この下部電極の周囲に形成され、下部電極の表面よりも高い表面を有するダミー電極と、下部電極上にダミー電極の最上表面よりも表面が低い位置にある誘電体膜を介して形成された上部電極と、ダミー電極に周囲を囲まれた窪みを埋める第2の絶縁膜とを具備して成る半導体装置を構成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】低伝導度領域ができるだけ少なくなるグラフェン配線構造が可能な半導体装置を提供する。

【解決手段】半導体装置は、触媒金属膜220と、グラフェン膜230と、コンタクトプラグ240と、調整膜250と、を備える。触媒金属膜は、基板上に形成される。グラフェン膜は、触媒金属膜上に形成される。コンタクトプラグは、グラフェン膜と接続する。調整膜は、前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に形成され、ディラック点位置をフェルミ準位に対してコンタクトプラグと接続する領域と同方向に調整する。

(もっと読む)

半導体基板の製造方法

【課題】ビア配孔内に形成したカーボンナノチューブを埋め込む埋め込み膜が基板に均一に形成されないため基板の平坦化処理工程において層間絶縁膜が不均一に研磨されて、下層配線と上部電極がビア配線以外で電気的につながってしまう場合が発生する。

【解決手段】半導体基板における層間絶縁膜内のビアホール内にカーボンナノチューブを形成した後、基板全体をフッ化処理することにより、カーボンナノチューブが存在するビアホールにのみ埋め込み膜が形成され、その後に基板全体の平坦化処理のために基板を研磨する工程において、層間絶縁膜が局所的に研磨されることを防止する。

(もっと読む)

半導体装置

【課題】信号線の上面に微小な凹凸が形成されても、伝送線路の伝送特性が劣化することを抑制できるようにする。

【解決手段】信号線522は、多層配線層400及び再配線層500の第a層(a≧2)に形成されている。プレーン配線444は多層配線層400及び再配線層500の第b層(b<a)に形成されており、平面視で信号線522と重なっている。2つのコプレーナ配線524は多層配線層400及び再配線層500の第c層(b≦c≦a)に形成されており、平面視で信号線522と平行に延伸しており、かつ信号線522を挟んでいる。信号線522からプレーン配線444までの距離hは、信号線522からコプレーナ配線524までの距離wより短い。信号線522の上方のうち、信号線522からwと同じ高さの範囲内には、電源線、グランド線、及び他の信号線が位置していない。

(もっと読む)

半導体装置及びその製造方法

【課題】配線間の実効的な容量の増加を抑制する。

【解決手段】半導体装置100は、6員環構造の環状シロキサンを原料とする絶縁膜11と、絶縁膜11に形成された配線溝12と、配線溝12に金属膜(配線メタル)15が埋め込まれて構成される配線10と、を有する。半導体装置100では、配線溝12の底面において、絶縁膜11の内部よりも単位体積あたりの炭素原子数、又は/及び、窒素原子数が多い改質層13が形成されている。

(もっと読む)

液晶表示装置の製造方法

【課題】配線破断を軽減する構造を有する液晶表示装置の製造方法を提供する。

【解決手段】基板上にゲート配線及び信号配線、ゲート絶縁膜、半導体パターン、データ配線、保護膜、ドレーン電極を露出させる第1接触孔及び信号配線を露出させ、側辺の長さが幅より大きく形成される複数の第2接触孔、第1及び第2接触孔を通じてドレーン電極に連結される画素電極及び信号配線に連結される信号配線補助パッドを形成する液晶表示装置の製造方法であって、信号配線を形成する段階では、信号配線に一対一に対応する複数の信号リードを有する信号伝送用フィルムを含み、信号伝送用フィルムには複数の信号リードのうちの高電圧信号を伝送する第1信号リードと低電圧信号を伝送する第2信号リードとの間にダミーリードが形成され、ダミーリードに対応するダミー配線が基板に形成され、ダミー配線は信号配線より酸化傾向が小さい特性を有する導電物質で形成される。

(もっと読む)

他の素子の処理の間のメモリセルの活性層の保護

【課題】メモリ構造に対して損傷を与えることを防止しながら選択された導電体から表面酸化物を適切に除去する。

【解決手段】導電層(102)を設け、その導電層(102)を覆うように誘電体(100)を設け、その誘電体(100)を貫通する第1および第2の開口(104,106)を設け、第1および第2の開口(104,106)内にそれぞれ第1および第2の導電体(108,110)を設けかつ第1および第2の導電体(108,110)を導電層(102)に接触させ、その第1の導電体(108)を覆うようにメモリ構造(126)を設け、そのメモリ構造(126)を覆うように保護要素(134)を設け、その第2の導電体(110)上に処理を施すことによる電子構造の製造方法。

(もっと読む)

洗浄組成物及び半導体装置の製造方法

【課題】配線構造や層間絶縁構造を損傷することなく、半導体基板上のプラズマエッチング残渣を十分に除去しうる洗浄組成物、及び前記洗浄組成物を用いた半導体装置の製造方法を提供すること。

【解決手段】57〜95重量%の(成分a)水、1〜40重量%の(成分b)第2級水酸基及び/又は第3級水酸基を有するヒドロキシ化合物、(成分c)有機酸、並びに、(成分d)第4級アンモニウム化合物、を含有し、pHが5〜10であることを特徴とする、半導体基板上に形成されたプラズマエッチング残渣除去用の洗浄組成物、並びに、前記洗浄組成物により、半導体基板上に形成されたプラズマエッチング残渣を洗浄する工程を含む、半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】配線とコンタクトプラグの短絡を効果的に防止する。

【解決手段】半導体装置の製造方法は、隣り合う配線の間に位置する層間絶縁膜内に、配線が露出した第1のコンタクトホールを含む複数のコンタクトホールを形成する。次に、(i)配線の露出した側面が、第1のコンタクトホールの第1の絶縁膜から構成される内壁側面と実質的に同一面となるか、又は(ii)第1のコンタクトホールの内壁側面において配線の露出した側面が窪んだ凹形状が形成されるように、露出した前記配線の一部を除去する。この後、コンタクトホールの内壁側面上にサイドウォール膜を形成後、コンタクトホール内に導電材料を充填することによりコンタクトプラグを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜を除去するエッチング中に、異常エッチングを防止する。エッチング工程において加わる水圧や風圧によりガードリングの形状が変形して剥離し、欠陥が発生することを防止する。

【解決手段】半導体装置は、メモリセル領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた周辺回路領域と、ガードリング及び周辺回路領域上に設けられた支持体膜と、周辺回路領域内に設けられたコンタクトプラグとを有する。ガードリングとコンタクトプラグは、同一の導電材料から構成される。

(もっと読む)

1 - 20 / 93

[ Back to top ]