Fターム[5F033PP04]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 原料ガス (624) | 無機系ガス (381) | ハロゲン化物 (210)

Fターム[5F033PP04]に分類される特許

101 - 120 / 210

半導体装置の製造方法

【目的】タングステン膜の成膜時にタングステン膜の剥れを防止できる半導体装置の製造方法を提供すること。

【解決手段】アルミ配線2を形成した半導体基板1上に第1P−TEOS膜3を形成し、その上にO3−NSG膜4を形成し、その上に第2P−TEOS膜5を形成し、その上に有機SOG膜6を形成し、エッチバックした後、その上に第3P−TEOS膜7を形成し、アルミ配線2上の前記の積層された層間絶縁膜にViaコンタクト8を形成し、その上にTiN膜9を形成し、その後でTiN膜9のアニール10を行った後、次工程でタングステン膜11を形成する。TiN膜9のアニールを行うことでタングステン膜11の剥れが防止できる。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜に開口された接続孔の内部に、チタン膜上に窒化チタン膜が形成された積層構造のバリアメタル膜を介して金属膜を埋め込んだ接続部における不具合を回避する。

【解決手段】コンタクトホールC1を形成して、その底部にニッケルシリサイド層14を露出させた後、TiCl4ガスを用いた熱反応により熱反応Ti膜21aを形成し、TiCl4ガスを用いたプラズマ反応によりプラズマ反応Ti膜21bを形成し、H2ガスを用いたプラズマ処理を施して、プラズマ反応Ti膜21bの塩素濃度を低減すると同時に、ニッケルシリサイド層14の表面の酸化膜を還元し、NH3ガスを用いた熱窒化処理及びNH3ガスを用いたプラズマ処理を施して、プラズマ反応Ti膜21bの表面に窒素リッチTiN膜21cを形成すると同時に、ニッケルシリサイド層14の表面の酸化膜を還元する。

(もっと読む)

半導体装置

【課題】 ストレスマイグレーション耐性およびエレクトロマイグレーション耐性に優れ、下部配線と上部配線との接続信頼性の高い半導体装置を提供すること。

【解決手段】 この半導体装置1において、Cuを主成分とするCu配線23とWからなるWプラグ32との間には、積層バリア膜30が介在されている。積層バリア膜30は、Taバリア膜42、TaNバリア膜43、Tiバリア膜44およびTaNバリア膜45が積層されてなる4層構造を有している。そして、Taバリア膜42は、ビアホール28の側面およびCu配線23の上面に被着されている。また、TiNバリア膜45は、積層バリア膜30の最上層をなし、Wプラグ32の表面に接触形成されている。

(もっと読む)

バリヤ層の形成方法及び処理システム

【課題】工程数を少なくし、ステップカバレジも良好にし、しかも、Ti膜とシリコン層との界面部分の抵抗値の増加を抑制することが可能なバリヤ層の形成方法を提供する。

【解決手段】表面の少なくとも一部にシリコン層6が露出している被処理体Wの表面に、Ti膜とTiN膜よりなるバリヤ層14を形成するバリヤ層の形成方法において、被処理体の表面に、シリコン層と接する部分がシリサイド化しないような温度でTi膜を形成するTi膜形成工程と、Ti膜上に前記シリコン層と接する部分がシリサイド化するような温度でTiN膜を形成するTiN膜形成工程とを有する。これにより、工程数を少なくでき、ステップカバレジも良好にし、しかも、Ti膜とシリコン層との界面部分の抵抗値の増加も抑制する。

(もっと読む)

タングステン膜の形成方法

【課題】本発明は半導体ウエハ等の被処理体に形成された凹凸部内にタングステン膜を形成するタングステン膜の形成方法に関し、Si基板上に形成された凹凸内に良好にタングステンの埋めこみを行うことを課題とする。

【解決手段】処理容器50内にMO−TiN膜からなるバリア膜3が形成されたSi基板Wを載置する工程と、処理容器50にWF6ガスとSiH4ガスとを交互に繰り返して供給する繰り返し工程を含み、前記バリア膜3上に第一のタングステン膜5を形成する工程と、処理容器50にWF6ガスとH2ガスとを同時に供給し、第一のタングステン膜5上に第二のタングステン膜6を形成する工程とを含むタングステン膜の形成方法であって、前記繰り返し工程では、Si基板Wの温度を150℃以上350℃以下に維持すると共に、前記WF6ガスの供給量を133Pa sec以上10kPa sec以下とし、WF6ガスのバリア膜3上への吸着量を飽和させる。

(もっと読む)

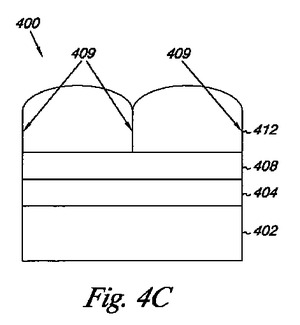

タングステンディジット線、その形成方法及び動作方法

タングステンディジット線を使用するための、及び、形成するための、方法、デバイス、及び、システムが記載されている。本開示の実施例に従って形成されたタングステンディジット線は、窒化タングステン(WNX)基板(402)上のタングステン(W)単分子層(404)と、W単分子層上のホウ素(B)単分子層(308)と、B単分子層上のバルクW層(412)とで形成されうる。バルクW層は、100nmから600nmの間の粒子サイズを有する。ディジット線は50nm未満の幅となりえる。従って、ディジット線のキャパシタンス及び抵抗は減少する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁層の剥離を抑制し、製品の歩留まりが向上するとともに製品信頼性が向上した半導体装置を得ることができる製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板上に形成された第1配線膜15と、反射防止膜17および第1レジスト膜18からなる積層体から、第1レジスト膜18を除去する工程と、前記工程において反射防止膜17表層に形成された変質膜22を除去する工程と、前記工程後に第1配線膜15に電気的に接続するビアプラグと、前記ビアプラグに電気的に接続する第2配線膜とを形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】プラグまたは局所配線による接続で低い接続抵抗と十分に小さい拡散層リーク電流を実現し、更に深さが異なる接続孔や開口断面の断面の形状や大きさが異なる接続孔または局所配線穴を用いる場合でも、十分に小さい拡散層リーク電流と低い接続抵抗を実現する製造方法を提供する。

【解決手段】基体上の絶縁膜に開口した、表面がシリコンを主成分とする層が底部に露出している第1の開口部(接続孔または局所配線穴)の群と、表面が第1の金属珪化物を主成分とする層が底部に露出している第2の開口部の群と、表面が第1の金属を主成分とする層が底部に露出している第3の開口部の群のうちの、少なくとも2群の各開口部の底部に、第2の金属珪化物を主成分とする層また第2の金属を主成分とする層を、化学気相成長法によって同時に形成する。

【効果】従来以上に高集積、高性能の半導体装置が実現される。

(もっと読む)

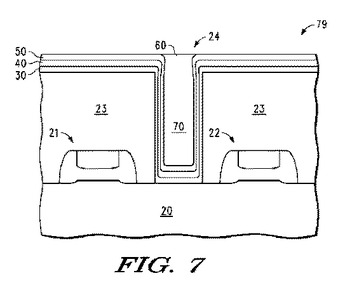

ボイドの無いコンタクトプラグ

コンタクトプラグを形成する半導体素子形成プロセスでは、チタンまたはタンタルコンタクト層(30)、窒化チタンバリア層(40)、及びタングステンシード層をコンタクト開口部(24)に順番に堆積させる。次に、コンタクトホール(24)への充填を、コンタクト開口部の底面から上に向かって、銅層(60)を電気メッキすることにより行なって、ボイドがコンタクト開口部(24)内に形成されることがないようにする。全ての余分な材料をCMPプロセスにより除去してコンタクトプラグ(70)を形成し、この場合、CMPプロセスを使用して、コンタクト層/シード層/バリア層(30,40,50)のうちの一つ以上の層を薄くする、または除去することもできる。  (もっと読む)

(もっと読む)

タングステン形成プロセス

【課題】本発明タングステン形成プロセスを提供する。

【解決手段】タングステンプラグ及び層の形成方法が、明らかにされている。ポリシリコン又はアモルファスシリコンの薄い層(たとえば15)が、接触開孔内に形成される。シリコンはWF6に露出され、それによってタングステンプラグ(たとえば21)が形成される。

(もっと読む)

半導体装置の製造方法

【課題】自己整合コンタクトプラグを形成する層間膜に、酸化シリコン膜のエッチング速度に対するエッチング速度比が100以上となる材料を適用し、コンタクトプラグとワード配線、あるいはコンタクトプラグとビット配線のショートを防止する信頼性の高いコンタクトプラグの形成方法を提供する。

【解決手段】上面及び側面が酸化シリコン膜で覆われた配線105bを形成した後、配線を覆って全面にシリコンを含有しない有機塗布膜からなる犠牲層間膜132aを形成し、犠牲層間膜および下層絶縁膜を順次にエッチングしてコンタクトホール108を形成し、コンタクトプラグを形成する。その後、犠牲層間膜を除去してコンタクトプラグの柱を形成し、その上に層間絶縁膜106を形成し、さらに層間絶縁膜を表面から一部除去し、容量コンタクトプラグの表面を露出させるようにした。

(もっと読む)

半導体装置とその製造方法

【課題】新規な特徴を有する半導体装置とその製造方法を提供すること。

【解決手段】シリコン基板10の上方に第1絶縁膜25を形成する工程と、第1絶縁膜25の所定の深さに不純物をイオン注入することにより、第1絶縁膜25に不純物層22を形成する工程と、不純物層22を形成した後、第1絶縁膜をアニールすることにより、不純物層22をバリア絶縁膜23に改質する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】浅いソース、ドレイン接合位置を保ちつつ、ソース、ドレインがシリサイド化され、かつ、接合リークが低く抑えられた半導体装置の製造方法および半導体装置を提供する。

【解決手段】MISFET(金属絶縁物半導体電界効果トランジスタ)を有する半導体装置の製造方法であって、シリコン基板1100の表面に、このMISFETのゲート絶縁膜を形成し、このゲート絶縁膜上にゲート電極を形成し、このゲート電極の両側に、{110}面方位を有するシリコン面上に設けられ、このシリコン面上の<100>方向に垂直な長辺と、この<100>方向に平行で幅が0.5μm以下の短辺からなる矩形状を呈し、MISFETのソース、ドレイン領域の一部を構成する複数のニッケルシリサイド(NiSi)領域501a、502aを形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体集積回路におけるコンタクトホールのような微細穴パターンを形成する場合に、形状を精度良くパターニングし且つ加工すること。

【解決手段】コンタクトホールを形成するためにハードマスクを作製する。このハードマスクはそれぞれ別のフォトリソグラフィ工程により作製され、素子形成領域17と平行な方向に形成された第1のハードマスク32と、素子形成領域17と交差する方向に形成された第2のハードマスク34との重ね合わせで構成されている。第1のハードマスク32と第2のハードマスク34はストライプ状の開口を有し、その交差部にコンタクトホールの開口が形成される。このような二回露光二回加工プロセスにより作製されるハードマスクを用いることで、穴状のパターンのレチクルでパターニングを行うよりも微細でより忠実なコンタクトホールの加工が可能となる。

(もっと読む)

強誘電体メモリセルおよび強誘電体メモリセルの製造方法

【課題】強誘電体キャパシタの電極を構成する金属膜相互間の接合強度を増大し、層間剥離を防止することができる強誘電体メモリセルおよび強誘電体メモリセルの製造方法を提供する。

【解決手段】半導体基板に形成されたトランジスタと、半導体基板上に形成された絶縁膜と、絶縁膜上に形成されてトランジスタと電気的に接続された下部電極と、下部電極上に形成された強誘電体からなる容量絶縁膜と、容量絶縁膜上に形成された上部電極と、を含む強誘電体メモリセルにおいて、下部電極は、酸化イリジウムからなる第1電極層と、前記第1電極層よりも上方に設けられた白金からなる第2電極層と、第1および第2電極層の剥離強度を強化する剥離強度強化手段と、を有する。

(もっと読む)

半導体装置

【課題】回路素子の集積密度が高く、かつ高性能で信頼性の高いものを製造し易い半導体装置を得ること。

【解決手段】半導体基板10に複数の回路素子22が形成され、これらの回路素子を覆うようにして第1層間絶縁膜30と第2層間絶縁膜45とがこの順番で積層され、第2層間絶縁膜に形成された複数のダマシン配線部53,57の各々と半導体基板に形成された所定の回路素子とを第1層間絶縁膜に形成された所定のコンタクトプラグ部35により接続する半導体装置60を構成するにあたり、対応するコンタクトプラグ部の上面および側面上部の各々と部分的に接して該コンタクトプラグ部に電気的に接続される少なくとも1つの第1ダマシン配線部53を上記複数のダマシン配線部に含ませる。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホール内に形成される銅プラグの接合リークの増加を抑制し、銅プラグの良好なコンタクトを達成できる半導体装置の製造方法を提供することである。

【解決手段】シリサイド層32を有する半導体基板1の上に絶縁膜38を形成し、さらに、シリサイド層32上の絶縁膜38にホール38fを形成し、ホール38f内とシリサイド層32の表面をクリーニングし、ホール38fの底面及び内周面に化学気相成長法によりチタン層41を形成し、銅拡散防止用のバリア層42をホール38f内のチタン層41上に形成し、銅層44をホール38f内に埋め込む工程を含む。

(もっと読む)

成膜方法,基板処理装置,および半導体装置

【課題】タングステンを埋め込むときのバリア層を形成する際に,チタン膜を形成し,そのチタン膜をすべて窒化して単一の窒化チタン膜をバリア層として形成することで,チタン層の変質によるタングステン膜の剥離を防止しつつ,従来よりもバリア層を薄くして,生産性を向上させる。

【解決手段】層間絶縁膜520上およびコンタクトホール530底部のシリコン含有表面512上にチタン膜を形成するチタン膜形成工程と,このチタン膜をすべて窒化し,単一の窒化チタン膜550を形成する窒化工程と,窒化チタン膜上にタングステン膜560を形成するタングステン膜形成工程とを有する。

(もっと読む)

半導体素子の配線構造及びこれの形成方法

【課題】簡単な工程を通じて形成しうる半導体素子の配線及びそれの製造方法が開示される。

【解決手段】配線は基板上に位置し、開口部を含む層間絶縁膜と、前記開口部内部を満たし、ソースガスの反応を用いる蒸着工程によって形成された第1タングステンからなるコンタクトプラグと、前記ソースガスの反応を用いる蒸着工程によって形成された第1タングステン及び物理気相蒸着工程によって形成された第2タングステンの積層された形状を有し、前記コンタクトプラグの上部面と接触する導電性パターンを含む。前記配線を形成するとき、平坦化工程が要求されない。なお、前記導電性パターンの表面モルフォルジー特性が優れている。

(もっと読む)

半導体装置とその製造方法

【課題】歩留まりを向上させることが可能な半導体装置とその製造方法を提供すること。

【解決手段】第1ホールの21a内面と、該第1ホール21aに露出する金属シリサイドパターン(導電パターン)17aの上面に、高融点金属よりなる第1バリアメタル膜22aを形成する工程と、第1バリアメタル膜22aの上に、高融点金属の窒化物よりなる第2バリアメタル膜22bを形成する工程と、第2バリアメタル膜22bをアニールする工程と、アニールの後に、第2バリアメタル膜22bの上にプラグ用導電膜23を形成する工程と、プラグ用導電膜23、及び第1、第2バリアメタル膜22a、22bを第1ホール21a内に第1導電性プラグ24として残す工程とを有する半導体装置の製造方法による。

(もっと読む)

101 - 120 / 210

[ Back to top ]