Fターム[5F033PP04]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 原料ガス (624) | 無機系ガス (381) | ハロゲン化物 (210)

Fターム[5F033PP04]に分類される特許

21 - 40 / 210

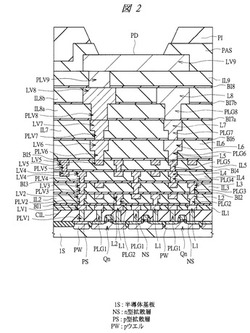

半導体装置

【課題】半導体チップ内の銅配線が一部消失することを防ぐ。

【解決手段】上層プラグ一本当たりの下層の配線の面積が10000μm2以上になるような大面積の多層配線を有する半導体装置において、前記多層配線が半導体基板1Sの主面においてn型拡散層NSを介してpウエルPWに接続される構造を形成せず、前記多層配線をp型拡散層PSを介してpウエルPWに接続する構造、前記多層配線をp型拡散層PSを介してn型拡散層NSに接続する構造、前記多層配線をn型拡散層NSを介してnウエルに接続する構造、または半導体基板1S上に形成されたMISFETのゲート電極に接続する構造を形成する。

(もっと読む)

半導体装置、半導体装置の製造方法、及び半導体装置の検査方法

【課題】層間絶縁膜に生じたボイドを高感度に検出する。

【解決手段】この半導体装置は、多層配線層(非図示、以下略)と、多層配線層中に形成された第一TEGパターン(非図示)を備える。第一TEGパターンは、互いに平行に延伸した複数の第一下層配線402と、層間絶縁膜(非図示)を貫通し、平面視で第一下層配線402間に位置する第一ビア602と、多層配線層の最上層(非図示)に形成され、第一ビア602に接続している第一端子762と、上記した同一の最上層に形成され、第一下層配線402に接続している第二端子764と、を備える。

(もっと読む)

半導体素子の製造方法

【課題】タングステン層の膜残りの発生を抑制する。

【解決手段】半導体基板1、コンタクトホール3を備えた絶縁膜2、絶縁膜2の表面およびコンタクトホール3の表面を被覆する被覆層4、並びに、コンタクトホール3を埋込むタングステン(W)層5を有するウエハに対し、ウエハを冷却せずに、W層5を被覆層4が露出しない範囲で高速でドライエッチングする工程と、ウエハを冷却せずに、W層5を被覆層4が露出しない範囲で、低速でドライエッチングする工程と、ウエハを冷却しつつ、被覆層4が露出するまで、W層5を低速でドライエッチングする工程と、ウエハを冷却しつつ、コンタクトホール3内のW層5を絶縁層2の高さまで低速でドライエッチングする工程と、を有する半導体素子の製造方法。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】より低抵抗な配線層を有する不揮発性記憶装置を提供する。

【解決手段】実施形態の不揮発性記憶装置は、書き替え可能な複数の不揮発性メモリセルと、前記複数のメモリセルのそれぞれに電気的に接続可能な配線層と、を備えた不揮発性半導体記憶装置である。前記配線層は、絶縁層に設けられたトレンチ内に設けられ、前記配線層は、第1導電層と、前記第1導電層の上に設けられた第2導電層と、を有し、前記配線層が充填されていない前記トレンチに対する前記第1導電層の埋め込み性は、前記配線層が充填されていない前記トレンチに対する前記第2導電層の埋め込み性よりも高く、前記第2導電層の比抵抗は、前記第1導電層の比抵抗よりも低い。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で横方向に成長するシリコン膜が連結されることを防ぎつつ、活性領域上に十分な厚みのシリコン膜を形成可能とした半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上に第1のシリコン膜12aを選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に第1のシリコン膜12aを覆うのに十分な厚みでマスク絶縁膜を埋め込んだ後、このマスク絶縁膜を第1のシリコン膜12aの表面が露出するまでエッチングにより除去する工程と、第1のシリコン膜12a上に第2のシリコン膜12bを選択的にエピタキシャル成長させる工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト孔に埋め込まれる金属プラグの材料が層間絶縁膜に染み出すのを防止できる半導体装置を提供する。

【解決手段】隣り合う2つのメモリセル1のサイドウォール間の不純物拡散領域に電気的接続されるコンタクトプラグ40が、層間絶縁膜18を貫通して設けられている。コンタクト孔41の側壁は、層間絶縁膜18より緻密なシール膜42で覆われている。コンタクトプラグ40は、シール膜42の表面およびコンタクト孔41の底面部を覆うように形成されたバリアメタル膜43と、バリアメタル膜43に包囲された状態でコンタクト孔41内に埋め込まれた金属プラグ44とを含む。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、ヒューズの微細化を図ること。

【解決手段】シリコン基板1に素子分離絶縁膜2を形成する工程と、素子分離絶縁膜2の上に第1の絶縁膜13を形成する工程と、第1の絶縁膜13にスリット13xを形成する工程と、スリット13xを通じて素子分離絶縁膜2をウエットエッチングして凹部2bを形成する工程と、凹部2bとスリット13xの各々の内面に第2の絶縁膜24を形成することにより、第2の絶縁膜24によりスリット13xを塞ぎつつ、凹部2b内にボイド24aを形成する工程と、ボイド24aの上の第2の絶縁膜24にホール25bを形成し、ホール25b内にボイド24aを露出させる工程と、露出したボイド24aとホール25bのそれぞれの中に導電膜27を形成することによりヒューズFを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】製造容易性、及び信頼性の高い半導体装置を提供する。

【解決手段】半導体装置100は、接続孔80を有する層間絶縁膜10と、接続孔80上に形成され、上端が接続孔80の上端より低い位置に位置する金属シード膜24と、金属シード膜24上に形成され、接続孔80内を埋め込んでおり、かつ金属シード膜24の上端を覆う金属膜20と、を備える。このためCMPによる平坦化工程において、金属シード膜24、26は露出せず、除去されない

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】半導体素子の特性を損なうことなく微細化に伴うコンタクト不良を低減した、電気的特性の良好な半導体装置を提供する。またこのような半導体装置の作製方法を提供する。

【解決手段】半導体層と電気的に接続する金属、又は金属化合物からなる下部電極を設け、この下部電極の一部が露出するように層間絶縁層に形成されたコンタクトホール内に、接続電極となる導電性シリコンウィスカーを形成する。その後、導電性シリコンウィスカーと電気的に接続する上部電極を形成すればよい。またこのように作製したコンタクトを用いて半導体装置を作製すればよい。

(もっと読む)

半導体デバイス製造方法

【課題】バリア金属膜とCVD法によって形成される金属導体膜である銅膜との間の密着性に優れた半導体デバイスの製造方法を提供すること。

【解決手段】基板上に直接にまたは絶縁体膜を介してバリア金属膜を形成する工程と、該バリア金属膜上にCVD法によって銅膜を形成する工程とを含む半導体デバイス製造方法において、該バリア金属膜を形成する工程と該銅膜を形成する工程との間に、加熱条件下アンモニア、水素、またはシランのうちの少なくともいずれか1つを含む第1の還元性ガスに暴露する工程と、該銅膜を形成する工程の後に、加熱条件下第2の還元性ガスに暴露する工程と、を有することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】パッド電極に荷重または衝撃力が加わっても、周囲の絶縁膜にクラックが発生しにくい構造の半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、平面形状が、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形、ならびに、これらの少なくとも一部分を含む形状の組合せからなる群から選ばれた平面形状となるような凹部を形成する凹部形成工程と、前記凹部の内面に少なくとも一部を被覆する下敷膜を形成する下敷膜形成工程と、絶縁膜で覆われた前記凹部に導電性の電極材質を埋め込むパッド部形成工程とを含み、前記凹部形成工程は、第1の凹部を形成する工程と、前記第1の凹部の一部分においてさらに深く凹む第2の凹部を形成する工程とを含む。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、バリアメタルの絶縁膜及びCuに対する密着性と、Cu拡散防止とを両立する。

【解決手段】 第1絶縁膜に設けた凹部の側壁に第2絶縁膜を形成し、第2絶縁膜の内側に順に第2絶縁膜との密着性が優れている第1の導電性バリア層、炭素を含有する第2の導電性バリア層、及び、Cu系埋込電極との密着性が優れている第3の導電性バリア層の3層構造のバリア層を介してCu系埋込電極を設けるとともに、前記第1の導電性バリア層と前記第2の導電性バリア層との界面と、前記第2の導電性バリア層と前記第3の導電性バリア層との界面に炭素混合領域を設ける。

(もっと読む)

半導体装置の製造方法

【課題】貫通孔となるべきアスペクト比が20以上の深孔を埋め込む貫通電極金属としては、埋め込み特性が良好なタングステンが使用されることが多いが、通常のドライエッチングによる深孔は、ボッシュプロセスによるものに比べて寸法の大きなものとなる。この比較的大きな深孔を埋め込むためには、必然的にウエハの表面に成膜すべきタングステン膜の膜厚も厚くなり、その結果、ウエハの反りが、プロセスを正常に実行できる限界を超える程度にまで増加する。また、このような問題が許容できる限度内である場合にも、タングステン膜を堆積する際に、ウエハの周辺で下地膜の剥がれが発生する等の問題がある。

【解決手段】本願発明は、貫通ビアを形成するための非貫通孔をタングステン部材で埋め込むに当たり、ウエハの周辺部において、下地のバリアメタル膜の外延部より内側に、タングステン部材の外延部を位置させるように成膜を実行するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】バリアメタルのステップカバレッジを向上させるボーダレスコンタクト構造を有する半導体装置を提供する。

【解決手段】低抵抗金属層と高融点金属元素を含む第1のバリアメタル膜を順次積層した構造の配線パタ―ン42Aと、配線パタ―ンを覆う層間絶縁膜43と、層間絶縁膜中に形成され、配線パタ―ンの上面の一部と側壁面の一部を露出し、さらに配線パタ―ンに、露出上面および露出側壁面を連結して形成された斜面をも露出斜面42dとして露出するビアホール43Aと、ビアホールの側壁面、露出上面および露出側壁面、さらに前記露出斜面に形成された、少なくとも低抵抗金属層の構成元素および高融点金属元素を含む導電性側壁膜43bと、導電性側壁膜を覆い、高融点金属元素を含む第2のバリアメタル膜と、前記第2のバリアメタル膜を介して充填し、前記第2のバリアメタル膜に接する導電性プラグと、を含む。

(もっと読む)

導電性バリア膜形成材料、導電性バリア膜形成方法、及び配線膜形成方法

【課題】溝や穴の開口部と深さとの比(開口部/深さ)が1/5〜1/7のような条件を要求されても、又、厚さが10nm以下であっても成膜が可能で、かつ、銅の拡散防止(バリア性)に優れ、更には電気抵抗が小さく、銅膜との密着性にも優れた導電性バリア膜形成材料を提供する。

【解決手段】ケミカルベーパーデポジションにより銅膜の下地膜として導電性Ta−Zr系バリア膜を形成する為の材料であって、Taを持つ金属有機化合物と、Zrを持つ金属有機化合物とを含むことを特徴とする導電性バリア膜形成材料、および、前記Ta有機化合物、前記Zr有機化合物の一方または双方を溶解する溶媒とを含むことを特徴とする導電性バリア膜形成材料。

(もっと読む)

半導体装置の製造方法

【課題】半導体製造プロセスにおけるガスの流量制御は、マスフローコントローラによって行われている。ここで使用される流量調整バルブは、流量を調整することに重点が置かれているため、閉鎖時にも微小ながらガスが流出する。このため、流量調整バルブの出力側に閉鎖特性の良好な開閉バルブが挿入されている。しかし、流量調整バルブと開閉バルブ間の流路系には、一定の容量を有するため、流量調整バルブが閉鎖されている間に、この流路系の圧力が流量調整バルブのリークを介して、上昇するという問題がある。このような出力側バルブ間空間の圧力上昇は、次に、開閉バルブが開いたときに、ガス被供給系への余剰のガス供給の原因となる。

【解決手段】本願発明は、マスフローコントローラのガス排出側の流量制御バルブと開閉バルブ間の圧力を計測することで、流量制御バルブの閉鎖時のリークガス流量を検知する半導体装置の製造方法である。

(もっと読む)

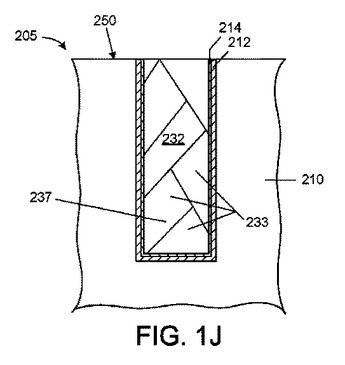

切欠構造のなかで長尺状ルテニウム膜上に多段階式銅鍍金を行う方法。

先端の集積回路にみられる切欠構造(206,207,208,209,211,213,264,275a,275b)において、長尺のルテニウム金属膜(214)に多段階で銅鍍金を行う方法である。長尺のルテニウム金属膜 (214)を利用すると、銅金属がトレンチ(266)及びビア(268)のような高アスペクト比の切欠構造(206,207,208,209,264,275a,275b)を充填するあいだ、不要な微細気泡が形成を防ぎ、前記ルテニウム金属膜(214)上に長尺の銅金属層(228)を含むサイズの大きい銅粒(233)が鍍金形成される。銅粒(233)は銅が充填された切欠構造(206,207,208,209,211,213,275a,275b)の電気抵抗を低下させ、集積回路の信頼性を向上させる。  (もっと読む)

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法を提供する。

【解決手段】本発明の半導体素子の形成方法は、基板上に半導体構造物及び絶縁パターンを形成し、絶縁パターンの一面によって定義される側壁と半導体構造物の底によって定義される底を有するオープニングを形成し、オープニングを満たす第1金属膜を形成し、第1金属膜を湿式エッチングしてオープニングの側壁を少なくとも一部露出させ、第1金属膜上に第2金属膜を選択的に形成することを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の設計自由度が高く、ゲート電極及びソース/ドレイン領域に接続されるコンタクト部の形成に問題が生じ難く、微細化プロセスに適した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基体21上にゲート電極31を形成し、基体にソース/ドレイン領域37及びチャネル形成領域35を形成し、ソース/ドレイン領域37上にゲート電極31の頂面と同一平面内に頂面を有する第1層間絶縁層41を形成した後、(b)第1層間絶縁層41に溝状の第1コンタクト部43を形成し、(c)全面に第2層間絶縁層51を形成した後、(d)第1コンタクト部43の上の第2層間絶縁層51の部分に孔状の第2コンタクト部53を形成し、その後、(e)第2層間絶縁層51上に、第2コンタクト部53と接続された配線61を形成する各工程から成る。

(もっと読む)

21 - 40 / 210

[ Back to top ]