Fターム[5F033PP04]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 原料ガス (624) | 無機系ガス (381) | ハロゲン化物 (210)

Fターム[5F033PP04]に分類される特許

201 - 210 / 210

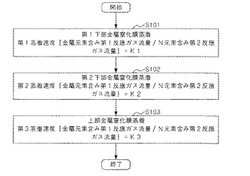

多重積層膜構造の金属窒化膜の蒸着方法

【課題】素子回路線幅の超微細化、パターン縦横比の増加、および蒸着温度の低下にもかかわらず、膜特性、段差塗布性、大気/湿気露出に対する膜質変化に対する安定性の全てを満足させる多重積層膜構造の金属窒化膜の蒸着方法を提供する。

【解決手段】基板上に第1蒸着速度で第1下部金属窒化膜を形成し、前記第1下部金属窒化膜上に第2蒸着速度で第2下部金属窒化膜を形成し、前記2段階によって形成された下部TiN膜上に、窒素(N)含有量の多い上部金属窒化膜を第3蒸着速度で形成することからなり、前記n番目膜の蒸着速度は、第2蒸着速度≧第1蒸着速度≧第3蒸着速度である。本発明によれば、基板上にTiN積層膜を形成することで、大気/湿気露出に対する安定性を向上させることができ、クラスタシステムの同一反応チャンバーまたは相違した反応チャンバーで容易に基板上にTiN積層膜を形成することができる。

(もっと読む)

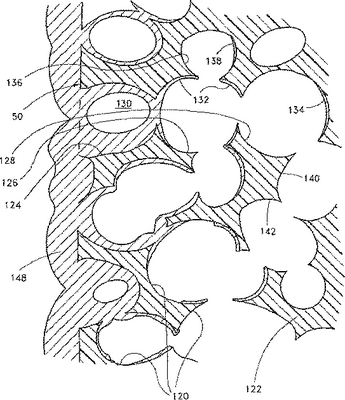

シーリング多孔質構造

集積回路中のデュアルダマシン(dual damascene)構造、特に多孔質材料中に形成された開口部のコンフォーマリティの裏張り(lining)のための方法及び構造が提供される。トレンチ(trench)及びコンタクトビア(contact via)が絶縁層中に形成される。これらのトレンチ及びビアの側壁上のポアがブロックされ、次いでこの構造は、所望のライニング材料の単層を形成するために交互に化学物質に曝される。例示的なプロセスフローにおいて、シーリング層の化学または物理気相成長法(chemical or physical vapor deposition)(CVDまたはPVD)により、不完全なコンフォーマリティに起因してポアをブロックする。交互のプロセスも、自己飽和(self−saturating)、自己制御(self−limiting)原子層堆積(atomic layer deposition)(ALD)プロセスと比較して減少されたコンフォーマリティを達成するようなパルス間隔及びパルス幅の選択によって構成され得る。なお別の構成において、異方性多孔質構造を有する層が、上部表面を選択的に溶融することによってシールされ得る。次いで、自己制御、自己飽和原子層堆積(ALD)反応により、有意にポアを充填することなくブロッキングが行われる。  (もっと読む)

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 フォトリソグラフィでのマスクの合わせズレに対するマージンが大きく、メモリ素子以外の他の素子領域を微細化することが可能な半導体装置の製造方法及び、半導体装置を提供する。

【解決手段】

半導体基板1にメモリ素子領域と、メモリ素子以外の他の素子領域とを有する半導体装置であって、メモリ領域上の第1層間絶縁膜20に設けられた第1コンタクトホールH1及び第1プラグ電極21と、ロジック領域上の第1層間絶縁膜に設けられた第2コンタクトホールH2及び第2プラグ電極22と、メモリ領域上の第1層間絶縁間20上に設けられて第1プラグ電極21上を覆う強誘電体キャパシタ30と、ロジック領域上の第1層間絶縁膜20上に設けられて第2プラグ電極22上を覆う第2配線52と、第2層間絶縁膜70と、第2層間絶縁膜70に設けられた第2配線52に至る第1ビアホールh1及び第3プラグ電極23と、を備えたものである。

(もっと読む)

半導体装置の製造方法

【目的】 ポーラス状に形成される多孔質低誘電率(p−lowk)膜内へのバリアメタルに用いたメタルの拡散を抑制することを目的とする。

【構成】 p−lowk膜を基体上に形成するp−lowk膜形成工程(S102)と、前記p−lowk膜表面側に形成される空孔が前記p−lowk膜内部側の空孔へ連結する連結位置における開口サイズより大きい分子(Ta−R1)を前記p−lowk膜表面に吸着させるTa[N(C2H5)2]5供給工程(S106)と、前記分子(Ta−R1)と反応するNH3を供給し、TaN膜を形成するNH3供給工程(110)と、前記開口サイズより小さい分子(Ta−R2)を吸着させるTaCl5供給工程(S114)と、前記分子(Ta−R2)と反応するNH3を供給し、TaN膜をさらに形成するNH3供給工程(120)と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【目的】 CVD法により形成された多孔質low−k膜上にバリアメタルを連続に形成することを目的とする。

【構成】 基体上に、有機物質原料を用いてCVD法により多孔質絶縁膜を形成するポーラスlow−k膜形成工程(S104)と、前記ポーラスlow−k膜表面に結合されるCH3基をエッチングするエッチング工程(S112)と、前記CH3基がエッチングされた前記ポーラスlow−k膜表面にALD法によりバリアメタル膜を形成するバリアメタル膜形成工程(S114)と、を備えたことを特徴とする。

(もっと読む)

低k材料上にTaN拡散バリア領域を堆積する方法(低k材料上のTaN拡散バリア領域のPE−ALD)

【課題】低k材料上にタンタル−窒化物(TaN)拡散バリア領域を堆積する方法を提供する。

【解決手段】この方法は、チャンバにおいてタンタル系前駆物質および窒素プラズマからプラズマ増強原子層堆積(PE−ALD)を実行することによって、低k材料基板(102)上に保護層(104)を形成することを含む。保護層(104)は、そのタンタル含有量よりも大きい窒素含有量を有する。次いで、タンタル系前駆物質ならびに水素および窒素を含むプラズマからPE−ALDを実行することによって、次の実質的化学量論的タンタル−窒化物層を形成する。また、本発明は、このように形成したタンタル−窒化物拡散バリア領域(108)も含む。一実施形態において、金属前駆物質は、五塩化タンタル(TaCl5)を含む。本発明は、低k材料とライナ材料との間に鮮鋭な界面を生成する。

(もっと読む)

半導体部品のための配線を組立てる方法

一面において、本発明は半導体部品のための配線を組立てる方法を含む。半導体基板が用意され、そして基板を貫通して全体に延びる開口(212)が形成される。約200℃以下の温度において開口の側壁(218)に沿って第一の材料(220)が堆積される。堆積は原子層堆積法と化学蒸着法のうちの一つまたは両方を含むことができ、そして第一の材料は金属窒化物を含むことができる。第一の材料の表面の上にソルダー湿潤材料(224)が形成される。ソルダー湿潤材料は、例えばニッケルを含むことができる。次いで、開口の中およびソルダー湿潤材料の上にソルダー(240)が設けられる。 (もっと読む)

ライン及びビア導体のための異なる材料を有するデュアル・ダマシン相互接続構造体

【課題】 ライン導体のために用いられるものと異なる、ビア又はスタッドのための材料を用いて、デュアル・ダマシン相互接続構造体を形成する方法を提供すること。

【解決手段】 ライン導体に用いられるものとは異なる、ビア又はスタッドのための材料を用いるか、又はトレンチ・ライナに用いられるものとは異なる、ビア・ライナのための材料を用いるか、或いは該トレンチ・ライナのものと異なるビア・ライナ厚を有する、デュアル・ダマシンのバックエンド・オブ・ライン(back−end−of−line:BEOL)相互接続構造体を形成する方法が開示される。改善された機械的強度のために、ビアに厚い超硬合金を用いる一方で、トレンチに薄い超硬合金だけを用い、抵抗を低くすることが好ましい。

(もっと読む)

多層配線構造及びその製造方法

【課題】 エレクトロマイグレーション耐性と、ストレスマイグレーション耐性を同時に向上させる多層配線構造及びその製造方法を提供する。

【解決手段】 AlCu膜103Cと、厚みが0〜15nmのTi膜との反応によりAl3 Ti層103DをAlCu膜とTiN膜の界面に形成することにより、界面拡散を抑制し、かつAl3 Ti層形成時に発生する引張り応力を低減し、EM耐性を向上させる。その後のFSG膜104AをHDP−CVD法で成膜する際に、ウェハ裏面に不活性ガスを流してウェハを冷却し、ウェハ温度を450℃以下にすることにより、FSGとAlCuの熱膨張率差に起因するAlCu膜の残留引張り応力の発生を低減し、SM耐性及びEM耐性を向上させる。さらに、FSG膜の上にSiON膜を設けることにより、FSG膜の遊離フッ素の上方への拡散を阻止して、上層配線の剥がれを防止する。

(もっと読む)

フリップチップ用高性能シリコンコンタクト

本発明においては、前面(14)と背面(16)とを備える半導体基板(12)であって、基板を(12)通って前面(14)と背面(16)との間を延びる孔(18、20、22)を備える半導体基板(12)を用意する。孔(18、20、22)は、部分的に、内壁部分によって規定され、外側導電性シースを形成する。導電性材料(54)を、内壁部分の少なくとも一部に隣接して形成する。その後に誘電体材料層(56)を、孔内部に、導電性材料上であってそのラジアル方向内側に形成する。次に第2の導電性材料(60)を、孔内部に、誘電体材料層(56)上であってそのラジアル方向内側に形成する。後者の導電性材料は、内側導電性コアキシャル線要素を構成する。 (もっと読む)

201 - 210 / 210

[ Back to top ]