Fターム[5F033PP04]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 原料ガス (624) | 無機系ガス (381) | ハロゲン化物 (210)

Fターム[5F033PP04]に分類される特許

41 - 60 / 210

半導体装置の製造方法

【課題】

微細化したMOSトランジスタを含む半導体装置において、リーク/ショートの可能性を抑制する。

【解決手段】

半導体装置の製造方法は、活性領域上に、ゲート絶縁膜とシリコン膜とを形成し、シリコン膜上方にゲート電極用レジストパターンを形成し、レジストパターンをマスクとして、シリコン膜を厚さの途中までエッチングしてレジストパターン下方に凸部を残し、レジストパターンを除去した後シリコン膜を覆うダミー膜を形成し、ダミー膜を異方性エッチングして、凸部の側壁にダミー膜を残存させつつ、平坦面上のダミー膜を除去し、ダミー膜をマスクとして、シリコン膜の残りの厚さをエッチングしてゲート電極を形成し、ゲート電極両側の半導体基板に、ソース/ドレイン領域を形成し、シリコン領域にシリサイドを形成する。

(もっと読む)

高アスペクト比のフィーチャーへのタングステン堆積方法

【課題】高アスペクト比のフィーチャーをタングステン含有材料で充填する。

【解決手段】部分的に製造された半導体基板上の高アスペクト比のフィーチャーをタングステン含有材料で充填する方法が提供される。ある実施形態においては、当該方法は高アスペクト比のフィーチャーにタングステン含有材料を部分的に充填する工程とフィーチャー空洞から部分的に充填された材料を選択的に除去する工程とを有する。これらの方法を用いて処理された基板においては、高アスペクト比のフィーチャーに充填されたタングステン含有材料のステップカバレッジが改善され、シームの大きさが低減する。

(もっと読む)

半導体装置およびその製造方法

【課題】プラグの上面の形状を工夫することにより、半導体装置の電気的特性において、信頼性の向上を図ることができる技術を提供する。

【解決手段】本願発明におけるプラグPLGは、上面がコンタクト層間絶縁膜CILの表面(上面)よりも突出した上に凸のドーム形状をしている。つまり、プラグPLGは、上面が上に凸のドーム形状となっており、コンタクト層間絶縁膜CILの上面の高さよりもバリア導体膜BF1の上端部の高さが高く、かつ、タングステン膜WFの上端部の高さはバリア導体膜BF1の上端部の高さよりも高くなっている。

(もっと読む)

半導体装置の製造方法

【課題】銅配線とアルミニウム配線との間のバリアを形成するための新規な技術を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の上方に形成された銅配線上に、絶縁膜を形成する工程と、絶縁膜に凹部を形成し、凹部の底に前記銅配線を露出させる工程と、凹部の底に露出した銅配線上に、250℃〜350℃の範囲の成膜温度で、フッ化タングステンの供給期間と供給停止期間とを交互に繰り返して、CVDでタングステン膜を選択的に成膜する工程と、タングステン膜上方に、アルミニウム配線を形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】ダマシン法を使用して配線を形成する半導体装置の製造技術において、信頼性の高い配線を形成する技術を提供する。

【解決手段】ハードマスク膜HM1上にハードマスク膜HM2が形成され、このハードマスク膜HM2上に有機樹脂膜ORFが形成された状態で、レジストCMPを実施する。これにより、ハードマスク膜HM2上に形成されている有機樹脂膜ORFが除去されるとともに、ハードマスク膜HM2の膜厚が膜減りする。その後、膜減りしたハードマスク膜HM2を除去し、露出したハードマスク膜HM1をマスクにしてトレンチを加工する。

(もっと読む)

半導体装置の製造方法

【課題】配線材との密着性が良く、バリア性の高い金属膜をもつ半導体装置、およびその製造方法を提供する。

【解決手段】基板上に絶縁膜、金属からなるバリアメタル膜、及びCu配線金属膜がこの順で積層された積層構造を具備してなり、バリアメタル膜の酸化物のX線回折測定による回折強度が、バリアメタル膜とCu配線金属膜との化合物の回折強度の10倍以下である。

(もっと読む)

小臨界次元のタングステン接点装置及び相互接続子の製法

【課題】高縦横比の特徴部のボイドなしの充填方法を提供する。

【解決手段】種々の実施例に於いて、この方法は低温化学蒸着工程によるタングステンでの特徴部の充填に関する。或る実施例に於いて、工程温度は特徴部充填の化学蒸着の間約350°C以下に維持される。この低温化学蒸着タングステン充填により、標準の化学蒸着充填と同様は薄膜抵抗を達成する一方、高縦横比の特徴部への向上された充填と下地層へとのフッ素移動への向上されたバリヤが得られる。発明は更に低抵抗を有するタングステンフィルムの堆積方法に関する。種々の実施例に於いて、この方法ではタングステンバルク層の堆積及び/或は低温化学蒸着によるバルク層の堆積の前に堆積された核形成層に低温低抵抗処理を実施し、その後高温化学蒸着を実施する。

(もっと読む)

小臨界次元の接点装置及び相互接続子用の超薄低抵抗タングステンフィルムの堆積方法

【課題】高縦横比の特徴部のボイドなしの充填方法を提供する。

【解決手段】種々の実施例に於いて、この方法は低温化学蒸着工程によるタングステンでの特徴部の充填に関する。或る実施例に於いて、工程温度は特徴部充填の化学蒸着の間約350°C以下に維持される。この低温化学蒸着タングステン充填により、標準の化学蒸着充填と同様は薄膜抵抗を達成する一方、高縦横比の特徴部への向上された充填と下地層へとのフッ素移動への向上されたバリヤが得られる。発明は更に低抵抗を有するタングステンフィルムの堆積方法に関する。種々の実施例に於いて、この方法ではタングステンバルク層の堆積及び/或は低温化学蒸着によるバルク層の堆積の前に堆積された核形成層に低温低抵抗処理を実施し、その後高温化学蒸着を実施する。

(もっと読む)

半導体装置の製造方法

【課題】配線層に銅配線を使用する半導体装置において、半導体基板の裏面に付着した銅原子が半導体基板の裏面から内部へと拡散することを抑制し、半導体基板の主面に形成されているMISFETなどの半導体素子の特性劣化を抑制できる技術を提供する。

【解決手段】半導体基板1Sの主面に形成される銅拡散防止膜を銅拡散防止膜DCF1aとし、半導体基板1Sの裏面に形成される銅拡散防止膜を銅拡散防止膜DCF1bとする。本実施の形態1の特徴は、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成する点にある。このように、銅配線の形成工程の前に、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成することにより、半導体基板1Sの裏面から銅原子(銅化合物を含む)が拡散することを防止できる。

(もっと読む)

被処理体の成膜方法及び処理システム

【課題】線幅やホール径が小さな凹部や高アスペクト比の凹部に対して十分な埋め込みを行うことが可能な成膜方法を提供する。

【解決手段】凹部6を有する絶縁層4が表面に形成された被処理体Wに対して薄膜を形成する成膜方法において、前記凹部内の表面を含めて前記被処理体の表面にTiを含むバリヤ層12を形成するバリヤ層形成工程と、前記バリヤ層上にRuを含むシード層16を形成するシード層形成工程と、前記シード層上に前記シード層に対する導通性を補助するためにCuを含む補助シード層164を形成する補助シード層形成工程とを有する。

(もっと読む)

成膜方法及びプラズマ成膜装置

【課題】ステップカバレジを向上させることができ、これによりスループットも高く維持することが可能な成膜方法及びプラズマ成膜装置を提供する。

【解決手段】真空排気が可能になされた処理容器22内へ凹部6を有する絶縁層4が表面に形成された被処理体Wを収容すると共に前記処理容器内へ原料ガスを供給してプラズマCVD法により前記被処理体に対してチタンを含む薄膜を形成する成膜方法において、前記薄膜の形成時の前記処理容器内のプロセス圧力を230〜630Paの範囲内に設定する。これにより、ステップカバレジを向上させることができ、スループットも高く維持することが可能となる。

(もっと読む)

成膜方法及びプラズマ成膜装置

【課題】全体としてのコンタクト抵抗を小さく維持しつつバリヤ性の高い薄膜の成膜方法及びプラズマ処理装置を提供する。

【解決手段】凹部6を有する絶縁層4が表面に形成された被処理体Wに対して薄膜を形成する成膜方法において、前記凹部内の表面を含む前記被処理体の表面にプラズマCVD法を用いて窒化チタン膜10の薄膜を形成する薄膜形成工程と、窒化ガスの存在下でプラズマを用いた窒化処理を行うことにより前記薄膜を窒化する窒化工程と、を有することを特徴とする成膜方法である。これにより、抵抗を小さく維持しつつバリヤ性の高い薄膜を形成する。

(もっと読む)

半導体装置

【課題】金属配線と金属酸化物を有する層を形成する際、電蝕といわれる腐食の発生をおさえることにより、半導体装置の動作特性および信頼性を向上させ、歩留まりの向上を実現することを目的とする。

【解決手段】配線は、耐酸化性金属からなる第1の層と、その上に形成されたアルミニウムもしくはアルミニウムを主成分とする第2の層と、その上に形成された耐酸化性金属からなる第3の層からなる3層構造とし、前記配線と電気的に接続する金属酸化物を有する層を有する。また、第2の層の上面及び下面は第1及び第3の層と接し、側面は酸素とアルミニウムを含む酸化層と接する。

(もっと読む)

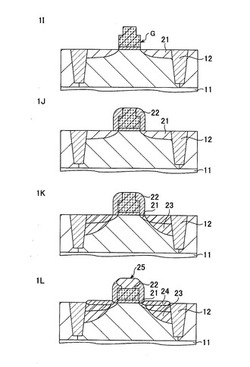

半導体装置及びその製造方法

【課題】 ビアホールの微細化及び高アスペクト比化が進むと、銅からなるシード層でビアホールの内面を連続的に覆うことが困難になる。

【解決手段】 半導体基板(10)の上に絶縁膜(20)が形成されている。絶縁膜に凹部(21)が形成されている。凹部の内面を第1の導電膜(22)が覆う。島状組織(25)が、第1の導電膜の表面に離散的に分布する。島状組織は、銅に対して、第1の導電膜の濡れ性よりも高い濡れ性を有する。凹部が、銅または銅合金からなる導電部材(31)で充填されている。

(もっと読む)

空隙を充填するべく低抵抗率のタングステン膜を堆積させる方法

【課題】抵抗率が低く、表面粗度が低く反射率が高いタングステンを、CVD法により基板上の間隙または凹状特徴部分に充填する方法を提供する。

【解決手段】基板に設けられた凹状部分を部分的に充填するタングステンバルクを堆積した後で、堆積されたタングステンの上部分を除去する。上部分の除去は、活性化されたフッ素種に基板を暴露することによって行われる。堆積されたタングステン粒子のうち急峻で突出している突起の頂点を選択的に除去することによって、除去処理は、凹状部分の側壁に沿ってタングステンを研磨することになる。堆積−除去のサイクルを複数回実行して、凹状部分を埋める。このようにして凹状部分が充填されると、CMPにおいてコアリング(coring)が発生しにくくなる。

(もっと読む)

銅配線形成方法、銅配線および半導体装置

【課題】表層部の銅を主体としてなる層の表面の結晶面の種類を低減することができ、それにより、銅配線本体の内部に存在する結晶粒界の密度を低減して、銅配線の電気抵抗を低減することができ、またEM耐性やSM耐性を改善して信頼性も向上することができるようにする。

【解決手段】この発明は、絶縁層10に銅からなる配線本体を備えてなる銅配線を形成する銅配線形成方法において、絶縁層10に開口部11を設ける工程と、開口部の内周面に、銅より酸化されやすい金属元素を含む銅合金被膜12を形成する銅合金被膜形成工程と、銅合金被膜に加熱処理を施して当該銅合金被膜からバリア層を形成するとともにその表面を構成する結晶面の種類を減じる加熱処理工程と、バリア層上に銅を被着させ、銅からなる配線本体を形成する配線本体形成工程と、を有することを特徴としている。

(もっと読む)

Ti膜の成膜方法および成膜装置、ならびに記憶媒体

【課題】CVDによりTi膜を成膜する際に、より低抵抗でかつ抵抗のばらつきが小さいTi膜を成膜することができ、プラズマダメージを小さくすることができるTi膜の成膜方法を提供すること。

【解決手段】チャンバ内にシリコンウエハを配置し、TiCl4ガスおよびH2ガスを含む処理ガスを導入しつつチャンバ内にプラズマを生成し、そのプラズマにより処理ガスの反応を促進してシリコンウエハ上にTi膜を成膜するにあたり、チャンバ内にシリコンウエハが配置された状態でTiCl4ガスを導入した後、チャンバ内にプラズマを生成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置及びその製造方法について、ホウ素含有タングステン層を核形成層とする場合に、コンタクト抵抗値の増大を抑制する。

【解決手段】半導体装置100は、半導体基板101上に形成された第1絶縁膜103と、第1絶縁膜103に埋め込まれた導電膜109を含み且つ半導体基板101に達するコンタクト110と、半導体基板101及び第1絶縁膜103のそれぞれと、導電膜109との間に形成され、高融点金属を含む第1バリア層107とを備える。更に、第1バリア層107と導電膜109との間に形成され、第1バリア層107よりも水分透過性の低い第2バリア層118を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】酸化処理や酸化剤への耐性を向上させ、かつビット線の低抵抗化を可能とする半導体装置及びその製造方法を提供する。

【解決手段】酸化処理により、第1ポリシリコン層14の側壁及び露出した基板10の底面に第3酸化膜17を形成する。次いで、ビット線16を、溝15の底面に形成し、溝15の側壁に第1窒化膜19を形成する。次いで、ビット線16上にのみ所望の厚さのタングステン層18を形成する。次いで、溝15を埋めるように第2窒化膜20を形成する。これにより、タングステン層18が第1窒化膜19及び第2窒化膜20で覆われることになり、この後に行われる熱処理や薬液処理からタングステン層18を保護することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】電極上に膜(水素バリア膜、バリアメタル)が形成される場合に、電極上での膜のカバレッジ不良の発生を防止することができる、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1では、強誘電体膜13上に、強誘電体膜13に接する電極下層15とこの電極下層15上に積層される電極上層16との積層構造を有する上部電極14が積層されている。そして、電極上層16の上面は、平坦化により、強誘電体膜13の表面モホロジーと無関係な平坦面となっている。したがって、電極上層16上で水素バリア膜17およびバリアメタル28をほぼ均一な厚さに形成することができ、上部電極14上での膜のカバレッジ不良の発生を防止することができる。

(もっと読む)

41 - 60 / 210

[ Back to top ]