Fターム[5F033PP20]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | PVD(物理的気相成長法) (5,261) | イオンビーム蒸着、イオンプレーティング (95)

Fターム[5F033PP20]に分類される特許

21 - 40 / 95

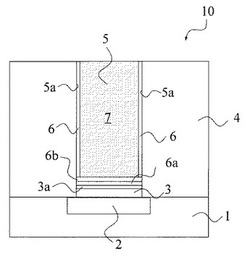

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】金属シリサイド膜と銅コンタクトプラグ本体との間の拡散バリア層として、薄膜の酸化マンガンで構成された拡散バリア層を用いてはいるものの、金属シリサイド膜への銅原子の拡散、侵入を確実に抑止することができるようにする。

【解決手段】本発明のコンタクトプラグ10は、半導体装置の絶縁膜4に設けられたコンタクトホール5に形成され、コンタクトホール5の底部に形成された金属シリサイド膜3と、コンタクトホール5内で金属シリサイド膜3上に形成され、非晶質でシリコンを含む第1の酸化マンガン膜6aと、その第1の酸化マンガン膜6a上に形成され、微結晶を含む非晶質の第2の酸化マンガン膜6bと、その第2の酸化マンガン膜6b上に、コンタクトホール5を埋め込むように形成された銅プラグ層7と、を備えることを特徴としている。

(もっと読む)

配線基板の製造方法

【課題】スループットが向上し、且つ少ない液滴量でも第1の電極と第2の電極とを導通性を確保する。

【解決手段】基体10の表面10aに形成された微細穴2の底部2aとなる下面電極3と、基体10の表面10aであって微細穴2の内壁部2bの上端近傍に配置された上面電極5とを導通させる導電層12を形成する。この導電層12の形成において、まず、金属ナノ粒子11を分散させるためのクリアインク8を微細穴2に充填する。次に、微細穴2に金属ナノ粒子11を含有する液滴を供給し、金属ナノ粒子11を微細穴2内のクリアインク8で分散させる。次に、微細穴2内のクリアインク8を揮発させることで、微細穴2の底部2a及び内壁部2bに析出した金属ナノ粒子膜11Aを有する導電層12を形成する。

(もっと読む)

半導体素子の製造方法

【課題】簡単な工程設備を用いて短い工程時間内に半導体素子のビアを形成できる半導体素子の製造方法を提供すること。

【解決手段】基板101に絶縁膜107と拡散防止膜109で内壁を被覆したビアホール105を形成する。荷電された金属粒子113を、電気力又は磁気力を利用して移動させて、このホールを金属粒子で充填する。ビアホールの下部から上方へ充填されるので、内部に空隙が発生することを抑制できる。従来技術による銅電気メッキ方式と比較すると、非常に短時間内に大きくて深いビアホールを金属粒子で充填できるため、シリコン貫通ビア(TSV)の工程コスト、及び工程時間を短縮することが出来る。また、従来技術の樹脂成分が多く含まれているメタルペーストを用いる乾式充填方式と比較すると、荷電された金属粒子を用いることで、より密なTSV金属配線を形成できる。

(もっと読む)

半導体装置

【課題】動作速度が低下することを抑制することができる半導体装置を提供する。

【解決手段】半導体装置は、MOSトランジスタ9を有するシリコン基板5と、シリコン基板5上に形成され、配線および絶縁膜により構成された配線層が複数積層された多層配線層と、多層配線層内に埋め込まれた、下部電極(下部電極膜91)、容量絶縁膜92、および上部電極(上部電極膜93)を有しており、メモリ素子を構成する容量素子90と、を備え、容量素子90とMOSトランジスタ9との間にダマシン形状の銅配線(第2層配線25)が少なくとも1層以上形成され、1つの配線(第2層配線25)の上面と容量素子90の下面とが略同一平面上にあり、容量素子90上に銅配線(プレート線配線99)が少なくとも1層以上形成されている。

(もっと読む)

伝送線路および高周波デバイス

【課題】層間膜としてコンポジット膜を用いた伝送線路において伝送損失を低減するための技術を提供する。

【解決手段】接地導体膜301、層間膜310、および配線303をこの順に積層してなる伝送線路300であって、層間膜310は、第1の材料からなる粒子302Aが絶縁材料302Bに分散されてなるコンポジット膜302を含み、層間膜310の配線303側の表面からの粒子302Aの平均直径の深さまでの範囲における粒子302Aの密度が、層間膜310のそれ以外の範囲における粒子302Aの密度よりも小さい。

(もっと読む)

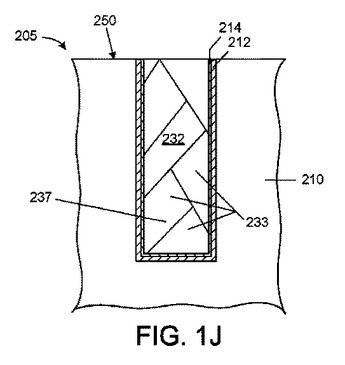

切欠構造のなかで長尺状ルテニウム膜上に多段階式銅鍍金を行う方法。

先端の集積回路にみられる切欠構造(206,207,208,209,211,213,264,275a,275b)において、長尺のルテニウム金属膜(214)に多段階で銅鍍金を行う方法である。長尺のルテニウム金属膜 (214)を利用すると、銅金属がトレンチ(266)及びビア(268)のような高アスペクト比の切欠構造(206,207,208,209,264,275a,275b)を充填するあいだ、不要な微細気泡が形成を防ぎ、前記ルテニウム金属膜(214)上に長尺の銅金属層(228)を含むサイズの大きい銅粒(233)が鍍金形成される。銅粒(233)は銅が充填された切欠構造(206,207,208,209,211,213,275a,275b)の電気抵抗を低下させ、集積回路の信頼性を向上させる。  (もっと読む)

(もっと読む)

回路基板

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】例えば、開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオン化された被着金属に、0.01eVから250eVの被着エネルギを与えるイオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体基板上の回路基板を低コストで供給する。

【解決手段】開口部101を介してチップ取り出し電極2を含む半導体基板1の一部表面が露出するようメタルマスク100を半導体基板1に被せ、イオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、半導体基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、半導体基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

回路基板の製造方法

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオン化された被着金属に、0.01eVから250eVの被着エネルギを与えるイオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

回路基板の製造方法

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

アクティブマトリックスアレイ及びその製造方法

【課題】印刷塗布して形成された絶縁膜の絶縁特性を良好に保持した状態で、生産性を向上することが可能なアクティブマトリックスアレイ及びその製造方法を提供する。

【解決手段】下地層34上に絶縁膜インクを印刷塗布する。印刷塗布された絶縁膜インクに含まれる溶媒が所定の絶縁特性が得られるまで十分に揮発させる前に終了するように絶縁膜インクを焼成して絶縁膜32を形成する。下地層34上に形成された絶縁膜32上に1つ以上の開口部33を有する導電層31を形成する。それにより、導電層31に設けられた開口部33から絶縁膜32内に残っている溶媒を揮発させることができるので、導電層31におおわれた絶縁膜32の絶縁特性を良好にすることができる。また、絶縁膜32が十分に揮発する前に、絶縁膜32上に導電層31を形成することができるので、生産性を良くすることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細な電極ピッチで形成された半導体基板が互いに接続された構造を有する半導体装置の信頼性を向上させる手段を提供する。

【解決手段】半導体装置は、第1の多層配線構造111を備えた第1の半導体基板110と、第2の多層配線構造121を備えた第2の半導体基板120とを有し、第1の半導体基板は第1の多層配線構造を構成する電極層の一部からなる第1の接合用電極層112を有し、第2の半導体基板は第2の多層配線構造を構成する電極層の一部からなる第2の接合用電極層122を有し、第1の接合用電極層は第1のディッシング部113を備え、第2の接合用電極層は第2のディッシング部123を備え、第1のディッシング部と第2のディッシング部との間に接合部材130が配置され、接合部材を介して第1の接合用電極層と第2の接合用電極層が接合される。

(もっと読む)

電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器

【課題】絶縁層へのコンタクトホール形成時における、導電層の浸食や破損の抑制された電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器を提供する。

【解決手段】導電層形成工程によって形成されたソース電極20A、ドレイン電極20B、及び画素電極20Cを含む導電層20上に、該導電層20及び酸化物半導体層18を覆うように、無機材料を主成分とする無機絶縁層23を形成する。そして、この無機絶縁層23上にフォトレジスト膜30を形成してパターン状に露光した後に、現像工程において、現像液を用いて現像することでレジストパターン30B’を形成する。現像工程では、この現像液をエッチング液として用いて、無機絶縁層23の内のレジストパターン30B’から露出した領域を除去することによって導電層20の一部を露出させて、無機絶縁層22にコンタクトホール27を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バリアメタルの被覆性を向上させる。

【解決手段】本発明の半導体装置は、キャップ絶縁膜1d上に形成された絶縁膜と、絶縁膜に形成された配線溝と、配線溝の底面に形成されたビア孔と、少なくともビア孔の側壁を覆うバリアメタル膜と、を有する。ビア孔は、径が異なる複数の孔から構成されており、複数の孔は、下に向けて径が小さくなるように深さ方向に接続し、複数の孔の接続部にキャップ絶縁膜に対してほぼ平行な面を有する。

(もっと読む)

半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器

【課題】生産性に優れた半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板7の一方の面側に、トランジスタ4のゲート絶縁体層44を形成する第1の工程と、ゲート絶縁体層44上に、厚さ方向に貫通する貫通部91を備える絶縁体層9を形成する第2の工程と、貫通部91内の底部付近のゲート絶縁体層44上、および、貫通部91の周囲の絶縁体層9上に、気相成膜法により同時にかつ互いに接触しないようにそれぞれ電極を形成し、ゲート絶縁体層44上に形成された電極を用いて、ゲート電極45を形成するとともに、絶縁体層9上に形成された電極を用いて、画素電極6を形成する第3の工程とを有する。また、平面視で、貫通部91の開口部の縁が、当該貫通部91の底部の縁より内側に位置する。

(もっと読む)

電子素子及びその製造方法、並びに表示装置

【課題】低温プロセスで製造でき、リーク電流が抑制された電子素子を提供する。

【解決手段】基板10上に、端部断面のテーパー角度が60°以下である下部電極22と、前記下部電極22上に配置され、水素原子の含有率が3原子%以下であり、波長650nmにおける屈折率nが1.475以下であるSiO2膜24と、前記SiO2膜24上に配置され、前記下部電極22と重なり部を有する上部電極26と、を有する電子素子である。

(もっと読む)

Cu合金膜および表示デバイス

【課題】透明基板との高い密着性、低い電気抵抗率、および優れたウェットエッチング性を示すCu合金膜を提供する。

【解決手段】透明基板と直接接触する表示デバイス用Cu合金膜であって、前記Cu合金膜は、下記(1)および(2)の要件を満足する酸素含有合金膜であることを特徴とする表示デバイス用のCu合金膜である。

(1)前記Cu合金膜は、Ni、Al、Zn、Mn、Fe、Ge、Hf、Nb、Mo、W、およびCaよりなる群から選ばれる少なくとも1種の元素を合計で0.10原子%以上10原子%以下含有する。

(2)前記Cu合金膜は、酸素含有量が異なる下地層と上層を有し、

前記下地層は前記透明基板と接触しており、前記下地層の酸素含有量が前記上層の酸素含有量よりも多い。

(もっと読む)

半導体配線の製造方法

【課題】例えばULSI(超大規模集積回路)等に代表されるSi半導体デバイス等の半導体装置において、高性能(低電気抵抗率)かつ高信頼性(高EM耐性)を示すCu系配線を提供する。

【解決手段】半導体基板上の絶縁膜に設けられた凹部にCu−Ti合金が直接埋め込まれてなる半導体装置のCu系配線の製造方法であって、前記Cu−Ti合金が、Tiを0.5原子%以上3.0原子%以下含むものであり、かつ、前記Cu−Ti合金をスパッタリング法で形成し、該Cu−Ti合金を前記凹部に埋め込む時または埋め込み後に、該Cu−Ti合金を下記加熱条件で加熱する工程を含むことを特徴とする半導体装置のCu系配線の製造方法。

(加熱条件)

加熱温度:350〜600℃

加熱時間:10〜120min.

室温から上記加熱温度までの昇温速度:10℃/min.以上

加熱雰囲気における酸素分圧:1×10−7〜1×10−4atm

(もっと読む)

半導体装置の製造方法

【課題】配線材料の拡散を抑えながら、金属配線の微細化を図ることができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に層間絶縁膜を形成する工程(a)と、層間絶縁膜に配線を形成する工程(b)と、配線の上面及び層間絶縁膜の上面に有機溶液を塗布する工程(c)と、工程(c)の後に、配線の上面及び層間絶縁膜の上面にシリル化溶液を塗布する工程(d)と、工程(d)の後に、基板を加熱する工程(e)と、少なくとも配線の上面上に第1のライナー絶縁膜を形成する工程(f)とを備えている。

(もっと読む)

導電層形成方法及び半導体装置

【課題】 貫通電極内部に導電層を形成する方法及び半導体装置において、貫通孔内の均一なメッキ付き周り性を向上させ、タクトタイムの短い導電層形成方法及び半導体装置を提供する。

【解決手段】 前記貫通孔の内部に第一のメッキ層を形成する第一のメッキ工程と、

前記第一のメッキ工程の後、前記貫通孔の開口部に前記第一のメッキ層とは異なる材料から成るメッキ抑制層を形成するメッキ抑制層形成工程と

前記メッキ抑制層形成工程の後、前記貫通孔の内部にメッキにより第二のメッキ層を形成する第二のメッキ工程を有する。

(もっと読む)

21 - 40 / 95

[ Back to top ]