Fターム[5F033PP20]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | PVD(物理的気相成長法) (5,261) | イオンビーム蒸着、イオンプレーティング (95)

Fターム[5F033PP20]に分類される特許

61 - 80 / 95

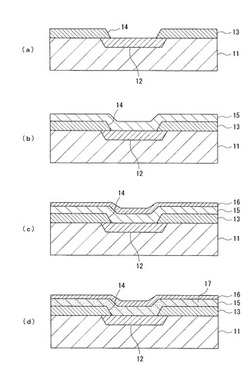

半導体装置および金属薄膜の形成方法

【課題】アルミニウム膜の流動性の低下を抑制しつつ、耐熱性を向上させる。

【解決手段】イオンビームデポジションなどの方法にて高純度アルミニウム膜15を絶縁層13上に形成した後、イオンビームデポジション法にて、添加元素17を含む添加元素膜16を高純度アルミニウム膜15上に形成し、添加元素膜16の熱処理を行うことで、添加元素膜16に含まれる添加元素17を高純度アルミニウム膜15に拡散させ、高純度アルミニウム膜15に添加元素17を添加する。

(もっと読む)

半導体装置のCu配線およびその製造方法

【課題】配線溝や層間接続路表面に形成されたTaNからなるバリア層との密着性が良好なCu配線と、このCu配線を製造できる方法を提供する。また、半導体基板上の絶縁膜に形成された配線溝や層間接続路の幅が狭く、深い場合でも、バリア層との密着性が良好で、配線溝や層間接続路の隅々に亘って埋め込まれているCu配線と、このCu配線を製造できる方法を提供する。

【解決手段】半導体基板上の絶縁膜に形成された配線溝または層間接続路に埋め込まれたCu配線を、(1)配線溝側または層間接続路側に形成されたTaNからなるバリア層と、(2)Pt、In、Ti、Nb、B、Fe、V、Zr、Hf、Ga、Tl、Ru、ReおよびOsよりなる群から選ばれる1種以上の元素を合計で0.05〜3.0原子%含有するCuからなる配線本体部とで構成する。

(もっと読む)

電子デバイス及びその製造方法

【課題】カーボンナノチューブを用いた配線構造を備える電子デバイスの製造方法について、炭素元素円筒型構造体からなるビアを歩留まり良く形成すること。

【解決手段】基板1上の第1絶縁膜2上に導電パターン5を形成する工程と、第1絶縁膜2と導電パターン5を覆う第2絶縁膜7を形成する工程と、第2絶縁膜7のうち導電パターン5の上にホール7aを形成する工程と、少なくともホール7a内の底面と第2絶縁膜7の上面に金属膜9を形成する工程と、金属膜9の表面に触媒粒子又は触媒膜からなる触媒面10を形成する工程と、触媒面10から炭素元素円筒型構造体11の束を成長する工程と、炭素元素円筒型構造体の束10の間隙に埋込膜12を形成する工程と、炭素元素円筒型構造体の束11及び埋込膜12及び金属膜9を研磨して第2絶縁膜7の上面から除去するとともに、埋込膜12及び炭素元素円筒型構造体の束11をホール7a内に残してビア13を形成する工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】多層配線構造の作製において、すべての多層配線用ビア・配線・電極および放熱用ビアなどを、相互の接続特性を良好に保って、カーボンナノチューブ(CNT)束により形成する半導体装置を提供する。

【解決手段】電導素材である、柱状構造をもったカーボンナノチューブ(CNT)束2の少なくとも一つの表面に、Au膜など金属膜を形成後、下地層を積層し、その上に触媒金属層を形成して、CVD法により柱状構造をもったカーボンナノチューブ(CNT)束7を成長することで、二つの柱状構造体カーボンナノチューブ(CNT)束を低抵抗で接続して形成する。この基本構成方法の組合せで、多層配線用の各種電導構成要素を作製する。また、成長条件によりCNTの成長先端部が平坦となることを用いて、Au膜など金属膜を利用せずに、成長方向に多段に、長いカーボンナノチューブ(CNT)束を作製でき、特に放熱用ビアなどへの適用が可能である。

(もっと読む)

半導体装置の配線形成方法

【課題】 半導体基板上にパワー素子と非パワー素子とが形成された複合集積回路において、アスペクト比が高い配線を形成するとともに、配線材料が層間絶縁膜中に拡散してデバイス特性の変動などが生じない信頼性の高い配線形成方法を実現する。

【解決手段】 層間絶縁膜形成工程により層間絶縁膜12を形成し、配線溝形成工程により層間絶縁膜12をエッチングして配線溝13を形成し、配線形成工程により配線溝13の内部にAl−Cu合金を充填し、配線18を形成する。これにより、CMOS部31に要求される微細配線とLDMOS部32に要求される厚い配線とを両立するアスペクト比が高い配線18を形成することができる。配線18にAl−Cu合金を用いるため、高温環境下で使用しても配線材料が層間絶縁膜12中に拡散して不具合を生じることがない信頼性の高い配線18を形成することができる。

(もっと読む)

半導体基板およびその製造方法

【課題】抵抗が比較的小さく、信頼性が高い金属配線を形成する。

【解決手段】第1の表面10aから反対側の第2の表面10bに貫通する貫通穴13と、第1の表面10a上に形成されたアルミ電極11と、第2の表面10bと貫通穴13の内周面とに跨って形成されアルミ電極11に電気的に接続された金属配線17とを有する。そして、金属配線17は、貫通穴13の内周面に形成された一部が、第2の表面10b側に形成された部分よりも厚くされている。

(もっと読む)

不均一窒化金属膜を用いる電気的接続構造物の形成方法およびこの方法によって製造された接続構造物

【課題】集積回路素子の電気的接続構造物の形成方法を提供する。

【解決手段】半導体基板100上に第1絶縁層200を形成し、第1絶縁層に開口を形成する。開口の側壁を不均一の窒素濃度を有する窒化第1金属層312でライニングする。開口の内部に導電パターン410が形成される。導電パターンと窒化第1金属層との間に第2金属窒化膜320が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトプラグの低抵抗化を図る。

【解決手段】シリコン基板1のソース/ドレイン領域7に接続するコンタクトプラグ14を、下層プラグ15としてタングステン層を用い、上層プラグ16として銅層を用いる構成である。下層プラグ15の高さをコンタクトホール13の1/3以下で、50nm程度とすることで、抵抗値を低下させつつも上層プラグ16の銅がシリコン基板1側に拡散するのを防止することができる。

(もっと読む)

ナノ金属粒子及びナノオーダの配線の形成方法

【課題】金属粒子の粒径のバラツキが少なく、かつその粒径の制御が容易なナノ金属粒子の形成方法及びナノオーダの配線の形成方法の提供。

【解決手段】ナノオーダの平坦性を持ち、かつ表面に化学的な結合手が極めて少ない材料からなる基板上に金属材料を真空蒸着する際に、その真空蒸着雰囲気下で基板を400℃から金属材料の融点未満までの範囲の温度に加熱した状態で、金属材料の蒸着量をナノオーダで制御して蒸着せしめ、径の制御されたナノ金属粒子又はナノオーダの配線を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】バリア膜の構造を工夫することで、銅配線と絶縁膜との密着性を向上させることを可能とする。

【解決手段】基板11上の第1絶縁膜12に形成された第1配線17を被覆する第2絶縁膜21と、前記第2絶縁膜21に形成された配線溝25と、前記配線溝25の底部の前記第2絶縁膜21に形成されたもので前記第1配線17に通じる接続孔26と、前記接続孔26底部を除く前記配線溝25と接続孔26との内面に形成された第1バリア膜31と、前記接続孔26底部の前記第1絶縁膜12上に形成された第2バリア膜34と、前記第1バリア膜31および第2バリア膜を34介して前記配線溝25および前記接続孔26に埋め込まれた第2配線35(含むプラグ36)とを備えたことを特徴とする。

(もっと読む)

回路基板及び電子機器

【課題】高周波信号の伝送特性を向上させることができるとともに、高周波ノイズの放射を低減することができる回路基板、及び当該回路基板を備える電子機器を提供する。

【解決手段】本発明の回路基板は、電気回路の信号線S1〜S5と電気的に接続されており、回路基板の表面と裏面との間であって回路基板の表面に対して交差する方向に延びるスルーホールT10〜T12と、スルーホールT10〜T12に対して隣接して設けられており、電気回路の基準電位を定めるグランド線G1〜G6に接続され、回路基板の表面に対して交差する方向に延びるスルーホールT20,T22,T23,T30〜T32を備え、スルーホールT10〜T12の各々は、少なくとも一つ以上のスルーホールT20,T22,T23,T30〜T32と隣接して配置される。

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁膜に形成された溝にタングステン膜を埋め込むことによりプラグあるいは埋め込み配線を形成する際、層間絶縁膜上に形成された不要なタングステン膜を除去する工程で生ずるエロージョンあるいはシニングを抑制できる技術を提供する。

【解決手段】酸化シリコン膜3の研磨速度に対してタングステン膜5bの研磨速度が速い第1研磨液を用いて、タングステン膜5bの研磨を酸化シリコン膜3が露出する前に終了する。その後、第1研磨液と、タングステン膜5bの研磨速度に対して酸化シリコン膜3の研磨速度が速い第2研磨液とを混合した第3研磨液を用いて、残りのタングステン膜と酸化シリコン膜の一部を研磨する。ここで、第3研磨液において、酸化シリコン膜3の研磨速度に対するタングステン膜5bの研磨速度の比を示す選択比が0.7以上1.5以下であるようにしている。

(もっと読む)

固体及び気体誘電体の組み合わせによって離間された相互接続した導電性配線及びビアを含む多層相互接続構造を形成する方法、及び、空隙を含む複数レベルの相互接続構造(空隙を含む多層相互接続構造及びその製造方法)

【課題】本発明は、空隙を含む複数レベルの相互接続構造及びその製造方法を提供する。

【解決手段】空隙を含む複数レベルの相互接続構造は、散在したライン・レベル及びビア・レベルの集合を含み、ビア・レベルは、1つ以上の誘電体層に埋め込まれた導電性ビアを含み、ビア・レベルの誘電体層は、隣接レベルのライン機構の上下に位置する固体であり、ライン機構の間でミシン目が入れられている。ライン・レベルは導電性ラインと、空隙を含む誘電体とを含む。導電性接点を含み、有孔誘電体層内に充填することによって形成された固体誘電性ブリッジ層は、散在したライン及びビア・レベルの集合上に配置されている。

(もっと読む)

100%又はそれより大きい段差被覆性を有する相互接続部金属化プロセス

【課題】 構造底部のバリア材料厚と比べると、構造側壁においてより厚いバリア材料被覆範囲を有する相互接続構造体、及び、そのような相互接続構造体を製造する方法を提供すること。

【解決手段】 構造底部のバリア材料厚と比べると、構造側壁においてより厚いバリア材料被覆範囲を有する相互接続構造体、及び、そのような相互接続構造体を製造する方法が提供される。本発明の相互接続構造体は、従来のPVDプロセス、従来のイオン化プラズマ堆積、CVD、又はALDによってバリア材料が形成される従来技術の相互接続構造体と比べると、半導体業界のための改善された技術拡張性を有する。本発明によると、構造底部のバリア材料厚(ht)より厚い、構造側壁のバリア材料厚(wt)を有する相互接続構造体が提供される。すなわち、本発明の相互接続構造体において、wt/ht比は、100%に等しいか又はそれより大きい。

(もっと読む)

半導体装置の製造方法

【課題】高度に微細化が進んでもコンタクト抵抗、バリア性及び金属埋め込み特性の三者を同様に満足のいくものとする高信頼性のコンタクトプラグ構造を有した半導体装置の製造方法を提供する。

【解決手段】下層と上層の電気的接続をするため絶縁膜41にコンタクトホール42を形成し、コンタクトホール42内に第1の高融点金属膜43を堆積し、第1の高融点金属膜43の表面を窒化し、第1の高融点金属膜の窒化表面44上に第2の高融点金属膜45を堆積し、第2の高融点金属膜45を熱処理により窒化物46に変化させる。

(もっと読む)

ナノ構造体に基づく相互接続および熱の散逸体

本発明は、導電または絶縁基板上に成長されるナノ構造体およびそれを作る方法を提供する。請求項の方法によって成長されるナノ構造体は、電子装置における相互接続および/または熱の散逸体に適切である。  (もっと読む)

(もっと読む)

表示デバイスの製造方法

【課題】 アルミニウム合金層と透明電極層とがコンタクトホールを介して直接接合された構造を有する表示デバイスにおいて、そのコンタクト抵抗値を増加させることのない、表示デバイスの製造技術を提案する。

【解決手段】 基板に形成されたアルミニウム合金層上に、絶縁層を形成し、該絶縁層にレジストを被覆してドライエッチングにてコンタクトホールを形成し、該コンタクトホールを介して透明電極層と前記アルミニウム合金層とを直接接合させる工程を備える表示デバイスの製造方法において、コンタクトホールの形成に用いるドライエッチングガスは無機ハロゲンガスとし、レジストを剥離する剥離液にはグリコール類含有の水系溶液を用いることとした。

(もっと読む)

半導体配線の製造方法

【課題】半導体基板上の絶縁膜に設けられた凹部にCu合金が埋め込まれた半導体配線を製造するに当たり、凹部にCu合金を埋め込むことができ、しかも配線の電気抵抗率を上げることなく絶縁膜とCu配線の界面にバリア層を形成することができる配線の製造方法を提供する。

【解決手段】半導体基板上の絶縁膜に設けられた、最小幅が0.15μm以下で、該最小幅に対する深さの比[深さ/最小幅比]が1以上である凹部の表面に、Tiを0.5〜3原子%とNを0.4〜2.0原子%含有するCu合金を形成した後、200℃以上、50MPa以上に加熱加圧して前記凹部内に前記Cu合金を埋め込むことによって半導体配線を形成すればよい。

(もっと読む)

半導体装置およびその製造方法

【課題】配線を低抵抗化するとともに、配線材料と層間絶縁膜との密着性を向上させる。

【解決手段】半導体装置100は、基板(不図示)上に形成された第1の銅含有導電膜124と、第1の銅含有導電膜124上に形成され、第1の銅含有導電膜124に達する凹部が形成された絶縁膜(108、110、112、114)と、これら絶縁膜の凹部側壁を覆うように形成され、銅の拡散を防止する材料により構成された第2のバリア絶縁膜128と、凹部の底面で第1の銅含有導電膜124に接するとともに凹部の側壁で第2のバリア絶縁膜128に接して凹部内壁を覆うように形成された銅と銅とは異なる異種元素との第2の接着合金膜130と、銅を主成分として含み、第2の接着合金膜130上に第2の接着合金膜130に接して凹部を埋め込んで形成された第2の銅含有導電膜132とを含む。

(もっと読む)

シリコン−ゲルマニウム立体構造CMOS上の局所配線の製造方法

【課題】シリコン−ゲルマニウム立体構造CMOSにおいて、シリコンCMOS素子とゲルマニウムCMOS素子との間の局所配線を容易に形成する。

【解決手段】シリコンCMOS素子を有するシリコン基板を準備し(12)、該素子の上部に絶縁層を形成する(14)。上記絶縁層を部分的に開口し(16)、その上にゲルマニウム薄膜を形成する(18)。アニール処理により、上記薄膜のゲルマニウムを流動化する(24)。これにより、開口部に上記ゲルマニウムが流れ込み、該ゲルマニウムと上記シリコン基板および上記シリコンCMOS素子との間に接点が形成される。さらに冷却することで、上記ゲルマニウムがLPE成長により結晶化される(26)。そして、単結晶のゲルマニウム上にゲルマニウムCMOS素子を形成する。

(もっと読む)

61 - 80 / 95

[ Back to top ]