Fターム[5F033QQ01]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 露光 (971)

Fターム[5F033QQ01]の下位に属するFターム

反射防止に関するもの (535)

Fターム[5F033QQ01]に分類される特許

141 - 160 / 436

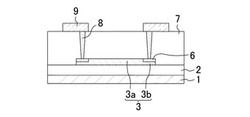

半導体装置及びその製造方法

【課題】アナログ回路を構成する抵抗体において、抵抗体の抵抗長が縮小化されることがあっても、アナログ回路を構成する各抵抗体の抵抗値間にバラツキが生じることを抑制する。

【解決手段】アナログ回路を構成する抵抗体3を有する半導体装置であって、半導体基板1上に形成され、長手方向に延びるボディ部3aと該ボディ部3aの端部に連接するヘッド部3bとを有し、且つシリコンからなる抵抗体3と、抵抗体3のヘッド部3bの上部に形成された金属シリサイド膜6と、抵抗体3を覆う層間絶縁膜7中に形成され、金属シリサイド膜6を介して、抵抗体3と電気的に接続するコンタクトプラグ8とを備え、ボディ部3aとヘッド部3bとの境界長は、抵抗体3の抵抗幅よりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】pMOSトランジスタ領域の窒化膜除去とnMOS側への後退抑制を両立する半導体装置の製造方法を得る事を目的とする。

【解決手段】本発明の一実施形態に係る半導体装置の製造方法は、(a)窒化膜16の表面に選択的にレジスト膜17を成膜する工程、(b)レジスト膜17をマスクとして窒化膜16をエッチングすると同時にレジスト膜17をもエッチングし、薄膜化され端面が退避されたレジスト膜17に覆われた窒化膜16を残す工程を備えて構成される。残される窒化膜16に対する工程(a)におけるレジスト膜17のオーバー露光量は50nm以上であり、工程(b)における窒化膜16のレジスト膜17に対する選択比は0.8〜1.2である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】製造効率を高めることができる半導体装置の製造方法等を提供する。

【解決手段】半導体装置1の製造方法は、絶縁層12のダイシング領域に溝部120を形成し、内部回路形成領域にビアホール126を形成する工程、絶縁層12上に第一のレジスト膜13を設ける工程、第一のレジスト膜13を覆う第二のレジスト膜14を設ける工程、第二のレジスト膜14の内部回路形成領域を覆う領域に配線用開口141を形成し第二のレジスト膜14のダイシング領域を覆う領域に位置合わせ用開口142を形成する工程、溝部120と位置合わせ用開口142との位置関係を検出し第二のレジスト膜14の配線用開口141が絶縁層12のビアホール126に対し所定の位置にあるかどうか検出する工程を含む。第二のレジスト膜14を選択的に除去する工程では、位置合わせ用開口142の領域が絶縁層12中の溝部120を覆うように位置合わせ用開口142を形成する。

(もっと読む)

半導体装置の製造方法

【課題】レジストポイゾニングの発生を抑制する信頼性の高い半導体装置を実現する。

【解決手段】ビアホール111を形成した後に溝114を形成する工程において、ビアホール111の形成領域に露光を行う工程と、配線溝の形成領域に露光を行う工程が含まれる。すなわち、ビアホール111を形成した後にビアホール111内に化学増幅型レジスト108が埋設されても、その後再びビアホール111の形成領域に露光が行われるため、ビアホール111の内部に十分な露光がされるようになる。これにより、ビアホール111内の感光領域、すなわち領域112および領域113が現像液で除去され、ビアホール111の内壁面の少なくとも一部が露出し、所望の構造の溝114が得られる。

(もっと読む)

半導体装置およびその作製方法

【課題】開口率の高い半導体装置又はその製造方法を提供する。また、消費電力の低い半導体装置又はその製造方法を提供する。

【解決手段】ゲート電極として機能する透光性を有する導電層と、該透光性を有する導電層上に形成されるゲート絶縁膜と、ゲート電極として機能する透光性を有する導電層上にゲート絶縁膜を介して半導体層と、半導体層に電気的に接続されたソース電極又はドレイン電極として機能する透光性を有する導電層とで構成されている。

(もっと読む)

半導体素子の形成方法及びメモリシステムの製造方法

【課題】半導体素子の形成方法、及びメモリシステムの製造方法を提供する。

【解決手段】基板400上にパターン形成対象層430を形成し、パターン形成対象層430上に、マスク層432を形成する。半導体素子の第1領域でマスク層432の一部を除去し、マスク層432を半導体素子の第2領域に残留させる。第1領域ではパターン形成対象層430上に、第2領域ではマスク層432上にモールドマスクパターン450を形成する。第1領域及び第2領域で、モールドマスクパターン450上にスペーサ層460を形成する。モールドマスクパターン450のパターン構造物の側壁に複数のスペーサが残留するようにスペーサ層460をエッチングし、第2領域でマスク層432をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】リソグラフィの露光解像限界を超えた寸法を有するパターンの形成において、工程数の削減が可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板上に形成された被加工膜上に第1のマスク材膜を形成し、前記第1のマスク材膜上にレジストパターンを形成し、前記レジストパターンを覆うように前記第1のマスク材膜上に所定の膜厚の第2のマスク材膜を形成し、前記第2のマスク材膜をエッチバックして前記レジストパターン及び前記第1のマスク材膜を露出させ、エッチバックされた前記第2のマスク材膜を残したまま、露出した前記レジストパターン及び前記第1のマスク材膜を同時に加工し、前記第1のマスク材膜下に露出する前記被加工膜部を加工する。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法を提供する。また、層間絶縁膜、平坦化膜、ゲート絶縁膜等の絶縁膜、配線、電極、端子等の導電膜、半導体膜等の半導体素子の各部位の膜を形成する方法を提供する。また、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供する。

【解決手段】ガリウムと亜鉛を含む液滴を吐出して、基板上に膜パターンを形成する。または、印刷法により、基板上にガリウムと亜鉛を含む材料を用いて膜パターンを形成する。

(もっと読む)

半導体装置の製造方法

【課題】配線用上部金属層の接続パッド部上面に柱状電極を電解メッキにより形成するためのドライフィルムレジストをラミネートするとき、配線用上部金属層間への気泡の発生を防止した半導体装置の製造方法を提供する。

【解決手段】半導体ウエハ21上の全面に形成された下地金属層8の上面周辺部にリング状のレジスト高さ位置規制部27が形成され、下地金属層の上面には配線用上部金属層9が形成されている。そして、ウエハステージ31の凹部32内に半導体ウエハを上部金属層およびレジスト高さ位置規制部の上面がウエハステージの凹部の周囲における上面と面一となるように配置する。次に、ウエハステージ、上部金属層およびレジスト高さ位置規制部の上面にドライフィルムレジスト33をラミネートする。この状態で、ドライフィルムレジストと下地金属層との間に空間35が形成されており、配線用上部金属層間の気泡の発生を防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、位置精度の高いバンプを形成することを目的とする。

【解決手段】(a)集積回路12が形成された半導体基板10であって、集積回路12と電気的に接続された電極14と、電極14の表面の外形に対して相対的な位置が固定されたマーク16と、を有する半導体基板10を用意する。(b)開口30を有し、開口30が電極14の表面と重なるメッキレジスト28を形成する。その後、(c)開口30が、電極14の表面上で予め設定された領域内にあるかどうかを、マーク16を基準にして検査する。その後、(d)メッキによって、開口30内であって電極14上に金属層34を形成する。(c)工程で、開口30が予め設定された領域内にはないことが検出されたときには、メッキレジスト28を剥離し、(b)及び(c)工程を再び行う。

(もっと読む)

表示装置およびその製造方法

【課題】 TFT液晶表示装置の動作不良や動作特性のばらつきを低減する。

【解決手段】 絶縁基板の表面上に複数の導電体パターンと、複数の半導体パターンと、複数の絶縁膜とを積層して、当該絶縁基板の表面上に走査信号線と、映像信号線と、TFT素子と、前記TFT素子に接続された画素電極と、前記映像信号線に接続された第1の外部接続端子と、前記走査信号線に接続された第2の外部接続端子とを設けた基板を有する表示装置であって、前記絶縁基板の表面上には、1つの材料膜をエッチングまたは露光現像して形成された複数の同時形成パターンを有し、当該複数の同時形成パターンは、同一の機能を有する前記同時形成パターンの側面の勾配が概ね等しく、かつ、すべての前記同時形成パターンの側面の勾配には2通り以上ある表示装置。

(もっと読む)

電子デバイス製造用基板およびそれを用いた電子デバイスの製造方法

【課題】微細なパターンを形成することができる電子デバイス製造用基板およびそれを用いた電子デバイスの製造方法を提供する。

【解決手段】電子デバイス製造用基板MSは、露光光を用いたフォトリソグラフィを施して電子デバイスを製造するためのものであって、被加工基板WSと、反射層RFと、透明スペーサ層ISと、フォトレジスト層PRとを備えている。被加工基板WSは主面を有している。反射層RFは、被加工基板WS上に設けられ、かつ反射光の位相が互いに反位相となる第1の部分P1および第2の部分P2を有している。透明スペーサ層ISは、反射層RF上に設けられ、露光光に対して透明なものである。フォトレジスト層PRは、透明スペーサ層IS上に設けられ、反射光に対する感光性を有している。

(もっと読む)

半導体装置の製造方法

【課題】 柱状電極を電解メッキにより形成するとき、半導体ウエハ上の全面に形成された下地金属層の周辺部からなるメッキ用接続端子部の部分へのメッキ液の浸入を確実に防止する。

【解決手段】 半導体ウエハ21上の全面に形成された下地金属層8の上面においてメッキ用接続端子部8aの内側には、柱状電極10形成用の第2のメッキレジスト膜28の周辺部からなるリング状の第2のシールリング接触部32が形成されている。そして、第2のメッキレジスト膜28の開口部28a内に柱状電極10を電解メッキにより形成するとき、メッキ治具のシールリング27を第2のシールリング接触部32の上面に接触させると、メッキ用接続端子部8aの部分へのメッキ液の浸入を確実に防止することができる。

(もっと読む)

半導体集積回路装置

【課題】 本発明は、NAND型のフラッシュメモリのセレクトゲート間に配置されるCB/CV連続コンタクト構造において、絶縁破壊を防止できるようにする。

【解決手段】 たとえば、半導体基板11上に設けられたセレクトゲートSG,SG間に、下層コンタクトCBと上層コンタクトCVとが直接連結された、複数のCB/CV連続コンタクト層12を千鳥状に配置する。そして、上層コンタクトCVを、そのCVパターンの底部が、セレクトゲートSGの上面よりも上方に位置するように配置することにより、CVパターンの長径寸法が、下層コンタクトCBのCBパターンの長径寸法よりも大きくなるように形成する。また、CBパターンの中心位置を、CVパターンの中心位置から内側にずらして配置する構成となっている。

(もっと読む)

ホール形成方法、ホール形成装置及びプログラム

【課題】1回の露光でより多くのホールを形成することが可能なホール形成方法を提供する。

【解決手段】ホール511、512の形成位置となる複数領域の内、一の領域を囲む他の領域のシリコン酸化膜51上に円柱を形成する。具体的には、4以上の複数領域の内、平面視において一の領域を囲む他の領域のシリコン酸化膜51上に円柱を形成する。次いで、シリコン酸化膜51及び円柱上にシリコン窒化膜を形成する。シリコン窒化膜はエッチバックされる。このエッチバックにより円柱を囲むサイドウォール541が形成される。円柱はエッチングされる。最後に、サイドウォール541をマスクにシリコン酸化膜51をエッチングする。これにより一の領域に対応するホール512及び他の領域に対応するホール511が形成される。

(もっと読む)

パターン形成方法、及び配線構造、並びに電子機器

【課題】隣接するパターン間の開口部を、投影露光機の解像度よりも微細化することが可能であって、かつパターン間の寸法精度ずれが生じにくいパターン形成方法を提供する。

【解決手段】本発明に係るパターン形成方法は、被エッチング膜を成膜する工程と、複数のパターンとして残したい領域に対応して被エッチング膜の上層に複数のマスクパターンを形成する工程と、複数のマスクパターンをマスクとして、エッチング処理を行うことにより被エッチング膜のパターンを形成する工程とを備える。この複数のマスクパターンは、其々が、第1の被覆パターンと、この第1の被覆パターンの一部の領域において積層領域を有する第2の被覆パターンとにより形成されている。積層領域の短手方向の幅は、異なる複数のマスクパターンにおける隣接するマスクパターン間で同一になるようにする。

(もっと読む)

半導体装置の製造方法

【課題】 適切なマークパターンを用いることが可能な半導体装置の製造方法を提供する。

【解決手段】 マークパターンの第1のパターン部分33aを有する第1の回路パターン原版33を用意する工程と、マークパターンの第2のパターン部分34aを有する第2の回路パターン原版34を用意する工程と、第1のパターン部分を下地領域31上のマスク膜32に転写して、マスク膜に第1の転写パターン部分32cを形成する工程と、第2のパターン部分をマスク膜に転写して、マスク膜に第2の転写パターン部分32dを形成する工程と、第1の転写パターン部分及び第2の転写パターン部分が合成された転写マークパターンを有するマスク膜をマスクとして用いて下地領域をパターニングし、下地領域に下地マークパターンを形成する工程とを備える。

(もっと読む)

電気光学装置の製造方法

【課題】フォトリソグラフィー工程を2回行って配線を形成する際のレジストパターン剥がれを防止する。

【解決手段】第1の配線51と第1の配線51を覆う層間絶縁層30とが形成された基板10上に、隣り合うように延在する複数本の第2の配線52を第1の配線51と交差するように形成する電気光学装置の製造方法であって、基板10上に導電材料層50を形成する第1の工程と、導電材料層50をパターニングして第2の配線52を形成する第2の工程と、第2の配線52を、互いに離間しているレジストパターン20で覆う第3の工程と、レジストパターン20で覆われていない領域に残る導電材料層50をエッチングする第4の工程と、を含み、第3の工程はレジストパターン20がブリッジ22により隣り合うレジストパターン20と互いに連結されるように形成する工程であることを特徴とする電気光学装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】凹部に膜を埋め込むための表面研磨を施す工程を有する半導体装置の製造方法に関し、製造歩留まりを向上させる。

【解決手段】ウェハ1の主面f1上に保護絶縁膜IP1と第1フォトレジスト膜とを順に形成し、チップ領域Rcおよび外周領域Rmの第1フォトレジスト膜に対して、第1フォトマスクを用いて露光を施すことで、分離パターンを形成する。続いて、第1フォトレジスト膜PR1をエッチングマスクとして保護絶縁膜IP1にエッチングを施した後、保護絶縁膜IP1をエッチングマスクとしてウェハ1にエッチングを施すことで溝部TRを形成する。その後、埋め込み絶縁膜IB1を形成し、ウェハ1の主面f1の全面に渡って埋め込み絶縁膜IB1を研磨することで、溝部TRに埋め込み絶縁膜IB1を埋め込むことで、分離部STIを形成する。

(もっと読む)

基板上にアライメントマークを作成する方法および基板

【課題】アライメントマーカのコントラストを強める方法を提供する。

【解決手段】基板上にアライメントマークを作成する方法は、導電性ラインセグメントおよびスペースセグメントにセグメント化された複数のラインを形成し、それによりライン間にスペースを形成して基板の第1のレイヤ内に微小構造を形成することと、基板の第2のレイヤ内に複数の導電性トレンチを作成することと、複数のトレンチをラインセグメントと電気的に接触させ且つ複数のトレンチを少なくとも部分的にスペースセグメントに重ねることとを含む。

(もっと読む)

141 - 160 / 436

[ Back to top ]