Fターム[5F033QQ01]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 露光 (971)

Fターム[5F033QQ01]の下位に属するFターム

反射防止に関するもの (535)

Fターム[5F033QQ01]に分類される特許

81 - 100 / 436

配線パターン形成方法および半導体装置の製造方法、半導体装置、データ処理システム

【課題】2回のリソグラフィ工程によるSADP法(Self Align Double Patterning)を用いて、第1配線パターン形成領域には解像限界未満のパターンを含む第1配線パターンを形成し、第2配線パターン形成領域には解像限界以上の通常パターンからなる第2配線パターンを簡便に形成する方法を提供する。

【解決手段】解像限界未満の寸法を有する複数の配線を含む第1配線パターンを、第1リソグラフィ工程と第1リソグラフィ工程の後に実施される第2リソグラフィ工程を用いて形成し、第1のリソグラフィ工程で形成されたパターンに対してのみサイドウォールの形成および除去処理を行い、その後、解像限界以上のパターンを生成する第2リソグラフィ工程を実施する。第2のリソグラフィ工程で形成される解像限界以上の通常パターンに対しては、単純なリソグラフィ工程とすることが可能となる。

(もっと読む)

半導体装置の作製方法

【課題】 レジスト材料の利用効率を向上させて、作製コストの削減を目的としたレジス

トパターンの作製方法、レジストパターンの除去方法、半導体装置の作製方法を提供する

ことを課題とする。

【解決手段】 本発明は、減圧下で、被加工物上に、感光剤を含む組成物を吐出してレジ

ストパターンを形成するステップを有することを特徴とする。また、前記レジストパター

ンをマスクとして前記被加工物をエッチングするステップ、若しくは、前記レジストパタ

ーンに、フォトマスクを介して前記感光剤の感光波長域の光を照射するステップ、前記レ

ジストパターンをマスクとして前記被加工物をエッチングするステップ、前記被加工物上

の前記レジストパターンを除去するステップを有することを特徴とする。

(もっと読む)

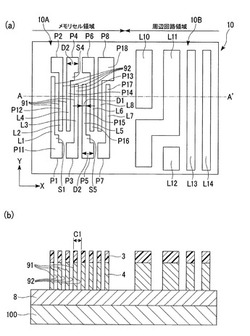

表示装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、画素部に酸化物半導体を用いた薄膜トランジスタを用い、さらに駆動回路の少なくとも一部の回路も酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

半導体装置

【課題】レジストパターンの解像不良を引き起こす反応阻害物質を確実に除去することが可能なダマシン構造の半導体装置及びその製造方法の提供。

【解決手段】基板上に、少なくとも第1層間絶縁膜6及び低誘電率膜からなる第2層間絶縁膜4を有し、第2層間絶縁膜上に形成した第1レジストパターン1aを用いてビアホール9を形成し、アミン成分を含有する有機剥離液で有機剥離処理を行った後、続いて第2層間絶縁膜上に第2レジストパターン1bを形成する工程を含む半導体装置の製造方法であって、ウェット処理後、第2レジストパターン下層の第2反射防止膜2bを塗布する前に、アニール処理、プラズマ処理、UV処理又は有機溶媒処理の少なくとも一の処理を行い、露光時にレジスト中で発生する酸の触媒作用を阻害するアミン成分を除去して第2レジストパターン1bの解像度の劣化を防止する。

(もっと読む)

半導体装置の製造方法

【課題】多層配線構造等を含む半導体装置の製造工程を簡略化する。

【解決手段】半導体装置の製造方法は、基板101上に絶縁膜102を形成する工程(a)と、絶縁膜102上にハードマスク膜103を形成する工程(b)と、ハードマスク膜103上に第1のモールド108を接触させて、陽極酸化により第1の酸化領域110を形成する工程(c)と、ハードマスク膜103上に第2のモールド111を接触させて、陽極酸化により第2の酸化領域112を形成する工程(d)と、第1の酸化領域110及び第2の酸化領域112を除去してハードマスク103aを形成する工程(e)と、ハードマスク103aをマスクとするエッチングにより、絶縁膜103中に接続孔104及び配線溝105を形成する工程(f)とを備える。第1の酸化領域110と第2の酸化領域112とは面積及び深さが異なる。

(もっと読む)

半導体集積回路

【課題】配線の幅とピッチが変化する部分の欠陥に対するマージンを十分に確保することが可能な半導体集積回路を提供する。

【解決手段】第1、第2の配線11,12は、配線の幅と配線間のスペースの幅が等しい。第3の配線13は、第1の配線11の一端に接続され、幅が第1の配線11の幅とスペースの幅に等しく、第2の配線12の側部に接続されている。第2の配線12は一部にギャップGを有している。

(もっと読む)

半導体装置の製造方法

【課題】低コストで微細パターンを形成可能な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、被加工体10上に第1のレジスト11を形成し、第1のレジスト11をパターニングする工程と、第1のレジスト11のパターニングの後、被加工体10上に第2のレジスト12を形成し、第2のレジスト12に対する選択的露光、ベーク及び現像を行い、その現像時に被加工体10上に残っている第1のレジスト11を除去するとともに、第2のレジスト12の一部を選択的に除去して、第2のレジスト12をパターニングする工程と、パターニングされた第2のレジスト12をマスクにして被加工体10を加工する工程と、を備える。

(もっと読む)

インプリント方法、配線パターンの形成方法、および積層電子部品

【課題】パターン欠陥の発生を抑制、防止して、パターンを歩留まりよく形成できるインプリント方法、それを用いた配線パターンの形成方法、該方法により形成された配線パターンを備えた積層電子部品を提供する。

【解決手段】被転写材領域R1の重心を通る直線上において、(a)被転写材領域内に位置する部分を線分被転写材部L1とし、(b)モールドパターン領域R2内に位置する部分を線分モールドパターン部L2とし、(c)プレス領域R3内に位置する部分を線分プレス部L3とした場合において、(イ)線分被転写材部の長さが線分プレス部の長さ以上で、(ロ)線分被転写材部と線分プレス部の重なる部分が線分被転写材部の92%以上を占め、かつ、(ハ)線分被転写材部の長さが線分モールドパターン部の長さ以上で、(ニ)線分被転写材部と線分モールドパターン部の重なる部分が線分被転写材部の97%以上を占めるという条件を満たしてインプリントを行う。

(もっと読む)

電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器

【課題】絶縁層へのコンタクトホール形成時における、導電層の浸食や破損の抑制された電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器を提供する。

【解決手段】導電層形成工程によって形成されたソース電極20A、ドレイン電極20B、及び画素電極20Cを含む導電層20上に、該導電層20及び酸化物半導体層18を覆うように、無機材料を主成分とする無機絶縁層23を形成する。そして、この無機絶縁層23上にフォトレジスト膜30を形成してパターン状に露光した後に、現像工程において、現像液を用いて現像することでレジストパターン30B’を形成する。現像工程では、この現像液をエッチング液として用いて、無機絶縁層23の内のレジストパターン30B’から露出した領域を除去することによって導電層20の一部を露出させて、無機絶縁層22にコンタクトホール27を形成する。

(もっと読む)

光硬化物複合体及び該光硬化物複合体を形成するための光硬化性組成物並びに光硬化物複合体の製造方法

【課題】薄膜部の厚さが制御され所望のパターン形状を有する光硬化物複合体及び該光硬化物複合体を形成するための光硬化性組成物並びに光硬化物複合体の製造方法を提供する。

【解決手段】基板1と、該基板1上に形成され薄膜部2及び該薄膜部2から突出した突出部3からなる光硬化物7とを具備する光硬化物複合体であって、前記薄膜部2は、該薄膜部2の厚さ方向に重ならない粒子6を含有し、前記薄膜部2の厚さは前記粒子6によって規定されている。

(もっと読む)

ネガ型感放射線性組成物、硬化パターン形成方法及び硬化パターン

【課題】高解像度であり、焦点深度(DOF)が広く、得られるパターン形状が良好であり、且つ低比誘電率な硬化パターンを形成することができるネガ型感放射線性組成物、並びに、それを用いてなる硬化パターン及びその形成方法を提供する。

【解決手段】ポリシロキサン(A)と、感放射線性酸発生剤(B)と、下記一般式(1)で表される構造単位(c1)を含む重合体(C)と、溶剤(D)と、を含有するネガ型感放射線性組成物。 (もっと読む)

(もっと読む)

重ね合わせ測定マーク及びパターン形成方法

【課題】重ね合わせ測定の精度を向上できる重ね合わせ測定マークを提供する。

【解決手段】第1パターンと第2パターンの重ね合わせ測定のためのマークにおいて、プラグ用ホールの開口パターンからなる第1パターンが形成された層間絶縁膜に該プラグ用ホールと同時に形成された第1ホールの開口パターンからなる第1マークと、前記層間絶縁膜に第1ホールと同時に形成され、前記プラグ用ホールの開口サイズと同程度で且つ第1ホールの開口サイズより小さい開口サイズを有する第2ホールの開口パターンからなる第2マークと、前記層間絶縁膜上の導電膜上に形成されたレジスト膜をパターニングして第2パターンと同時に形成されたレジストパターンからなる第3マークを含む構成とする。

(もっと読む)

薄膜トランジスタ基板の製造方法、薄膜トランジスタ基板、及び表示装置

【課題】コンタクトエッチングの加工精度を上げて、精度良くコンタクトホールが形成されたTFT基板及び、そのTFT基板を工程が煩雑にならずに製造コストが抑制可能なTFT基板の製造方法を提供する。

【解決手段】厚膜レジスト部21と厚膜レジスト部よりも厚みの薄い薄膜レジスト部22と、開口部23とからなる膜厚差を有するパターンのレジスト層20を設け、レジスト層20の開口部の絶縁膜のエッチングと、レジスト層20の薄膜レジスト部22の除去と、薄膜レジスト部22の下層の絶縁膜のエッチングとを同じエッチング工程で行うことにより、ゲートコンタクトホール8及びシリコンコンタクトホール9を共に形成してTFT基板1を製造した。

(もっと読む)

ポリマの指向性自己組織化を利用するサブリソグラフィ構造の形成方法

【課題】 ポリマの指向性自己組織化を利用するサブリソグラフィ構造の形成方法を提供する。

【解決手段】 ブロック・コポリマの自己組織化を含む方法であって、目標とするCD(限界寸法)を有する開口部(1つ又は複数の基板内の)から開始して、ホールを規則的な配列又は任意の配列に形成する方法を説明する。重要なことに、形成されたホールの平均直径の百分率ばらつきは、最初の開口部の平均直径の百分率ばらつきより小さくなる。形成されたホール(又はビア)を下層の基板に転写することができ、次にこれらのホールを金属導体のような材料で埋め戻すことができる。本発明の好ましい態様は、22nm以下の技術ノードにおいても、より狭いピッチ及びより優れたCDの均一性を有するビアの作成を可能にする。

(もっと読む)

ブロック共重合体を用いてホール又はビアを有するデバイスを形成する方法

【課題】 ブロック共重合体を用いて所定の位置にホール又はビアを有するデバイスを形成する方法を提供する。

【解決手段】 例えば、光リソグラフィを用いて、輪郭を付けられた凸状のセグメントによって与えられる断面を有する開口部を基板内に形成する。開口部の断面は、例えば、重なった円形領域によって与えることができる。側壁は、種々の点で隣接し、そこで突起を画定する。ブロック共重合体を含むポリマーの層を開口部及び基板の上に塗布し、自己集合させる。開口部内に個別分離ドメインが形成され、これらを除去してホールを形成し、これを下層の基板に転写することができる。これらのドメイン及びこれらの対応するホールの位置は、側壁及びそれらに付随する突起によって所定の位置に誘導される。これらのホールを隔てる距離は、何も側壁がない場合にブロック共重合体(及び何れかの添加剤)が自己集合したとする場合よりも大きく又は小さくすることができる。

(もっと読む)

配線パターンの形成方法

【課題】インプリントモールドの凹部への感光性配線ペースト層の充填不良や、ウェットエッチング(現像)工程での配線パターンの倒壊や剥がれの発生を抑制,防止して、効率よく精度の高い配線パターンを形成する。

【解決手段】感光性配線ペースト層2を形成する工程と、凹凸パターン17を有するインプリントモールド3を感光性配線ペースト層2に押し付けて光照射する工程と、感光性配線ペースト層2の未感光部をウェットエッチングにより除去して、インプリントモールドの凹凸パターンに対応する配線パターンを形成する工程とを備えた配線パターンの形成方法において、感光性配線ペースト層2の厚みtpを下記の式(1)の範囲で規定する。

6μm+(V/S)<tp<20μm+(V/S)……(1)

ただし、

tp:感光性配線ペースト層の厚み、

S:ペースト転写領域の面積、

V:前記凹凸パターンの、前記感光性配線ペースト層と接する領域における凹部の体積

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

半導体装置の作製方法

【課題】 レジスト材料の利用効率を向上させて、作製コストの削減を目的としたレジス

トパターンの作製方法、レジストパターンの除去方法、半導体装置の作製方法を提供する

ことを課題とする。

【解決手段】 本発明は、減圧下で、被加工物上に、感光剤を含む組成物を吐出してレジ

ストパターンを形成するステップを有することを特徴とする。また、前記レジストパター

ンをマスクとして前記被加工物をエッチングするステップ、若しくは、前記レジストパタ

ーンに、フォトマスクを介して前記感光剤の感光波長域の光を照射するステップ、前記レ

ジストパターンをマスクとして前記被加工物をエッチングするステップ、前記被加工物上

の前記レジストパターンを除去するステップを有することを特徴とする。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

半導体装置

【課題】高価な露光装置や高価なマスクを用いることなく、配線等のピッチを狭くすることができる半導体装置を提供する。

【解決手段】第1の導電パターン42と、第1の導電パターンに隣接して形成された第2の導電パターン42と、第1の導電パターンの所定領域下に形成された第1の導体プラグと、第1の導電パターンの所定領域上に形成された第2の導体プラグ62nと、第2の導電パターンのうちの、第1の導電パターンの所定領域に隣接する所定領域下に形成された第3の導体プラグと、第2の導電パターンの所定領域上に形成された第4の導体プラグ62n+1と、第1の導電パターン42の上方に形成され、第2の導体プラグに接続された第3の導電パターン62と、第2の導電パターンの上方に形成され、第4の導体プラグに接続された第4の導電パターン64とを有し、第4の導体プラグは、第2の導体プラグに対して、ずれた位置に配されている。

(もっと読む)

81 - 100 / 436

[ Back to top ]