Fターム[5F033QQ01]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 露光 (971)

Fターム[5F033QQ01]の下位に属するFターム

反射防止に関するもの (535)

Fターム[5F033QQ01]に分類される特許

61 - 80 / 436

半導体装置

【課題】小型化が可能な半導体装置を提供する。

【解決手段】半導体装置において、第1の導電性材料からなる第1のコンタクトと、第2の導電性材料からなり、下端部が第1のコンタクトの上端部に接続された第2のコンタクトと、第3の導電性材料からなり、下面が第1のコンタクトの下面よりも上方に位置し、上面が第2のコンタクトの上面よりも下方に位置し、第1及び第2のコンタクトから離隔した中間配線と、を設ける。そして、第2の導電性材料に対する第1の導電性材料の拡散係数は、第2の導電性材料に対する第3の導電性材料の拡散係数よりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】セルアレイ内部とセルアレイの端部とでパターンを均一に形成できる半導体装置の製造方法を提供すること。

【解決手段】 本発明は、第1の領域と第2の領域とが画定された基板上にエッチング対象層を形成するステップと、該エッチング対象層上に第1の開口を有する第1の感光膜パターンを形成するステップと、該第1の感光膜パターンの表面に遮光膜を形成するステップと、該遮光膜が形成された第1の感光膜パターン上に、前記第1の領域と第2の領域とを同時に露光して複数の第2の開口を有する第2の感光膜パターンを形成するステップと、前記第1の感光膜パターンと第2の感光膜パターンとをエッチングバリアとして、前記エッチング対象層をエッチングして複数のパターンを形成するステップとを含むことを特徴とする。

(もっと読む)

半導体装置

【課題】並列に並ぶゲートパターンを有する半導体装置において、ゲートパターンのレイアウトを工夫することによって、光近接効果を補正しつつ、集積度を向上させる。

【解決手段】並列に並ぶゲートパターン21,22の端部と、並列に並ぶゲートパターン23,24の対向端部とにおいて、ゲートパターン21の端部はゲートパターン22の端部よりもゲートパターン23,24の方に突き出ており、ゲートパターン24の対向端部はゲートパターン23の対向端部よりも、ゲートパターン21,22の方に突き出ている。引っ込んでいる方の、ゲートパターン22の端部およびゲートパターン23の対向端部について、仕上がり形状において後退が生じない程度に、補正量を大きく設定することができる。

(もっと読む)

半導体装置の製造方法

【課題】配線とコンタクトプラグの短絡を効果的に防止する。

【解決手段】半導体装置の製造方法は、隣り合う配線の間に位置する層間絶縁膜内に、配線が露出した第1のコンタクトホールを含む複数のコンタクトホールを形成する。次に、(i)配線の露出した側面が、第1のコンタクトホールの第1の絶縁膜から構成される内壁側面と実質的に同一面となるか、又は(ii)第1のコンタクトホールの内壁側面において配線の露出した側面が窪んだ凹形状が形成されるように、露出した前記配線の一部を除去する。この後、コンタクトホールの内壁側面上にサイドウォール膜を形成後、コンタクトホール内に導電材料を充填することによりコンタクトプラグを形成する。

(もっと読む)

半導体装置の製造方法及びフォトマスク

【課題】半導体記憶装置の製造において、パターン間隔を縮小し、レジスト膜厚、エッチング量等のバラツキに対応する。

【解決手段】半導体装置の製造方法は、基板上に被加工膜を形成する工程(a)、被加工膜上にレジスト膜を形成する工程(b)、フォトマスクのマスクパターン200bをレジスト膜に転写パターン200cとして転写する工程(c)、転写パターン200cを加工する工程(d)を含む。転写パターン200cは、所定間隔を開けて端部同士が対向して直列に並ぶ第1及び第2の転写ラインパターン201c及び202cと、これらに各々並列する第3及び第4の転写ラインパターン203c及び204cと、第2及び第3の転写ラインパターン202c及び203cの端部同士を接続する接続部212とを含む。工程(d)にて、接続部212の少なくとも一部を除去し、第2及び第3の転写ラインパターン202c及び203cを分離する。

(もっと読む)

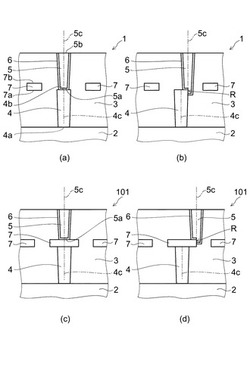

半導体装置及びその製造方法

【課題】マイクロローディング効果を防止しながら、上層配線となる金属配線のレイアウト制約のない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極4と、半導体基板1に形成された拡散層5と、半導体基板1の上に形成された絶縁膜7及び絶縁膜8と、絶縁膜及び絶縁膜8を貫通するホール9Dに埋め込まれ、側面を絶縁膜11で覆われた金属材料からなるプラグ12と、絶縁膜8を貫通しないホール10Bに埋め込まれ、絶縁膜11からなる絶縁体10Cと、絶縁膜8の上に形成され、プラグ12と電気的に接続する金属配線13Bとを備えている。

(もっと読む)

半導体装置、半導体装置の製造方法、および、リソグラフィマスクの製造方法

【課題】リソグラフィを用いて形成される半導体装置を高性能化させる。

【解決手段】互いに同じ材質からなる第1導体パターンPE1および第1ダミー導体パターンDM1を含む第1の層L1と、第2導体パターンPE2を含む第2の層L2とがシリコン基板SUB1上に積層されている。第2導体パターンPE2は、第1導体パターンPE1または第1の層L1より下層の導電部と、コンタクトプラグCP1によって電気的に接続されている。第1ダミー導体パターンDM1のうち、コンタクトプラグCP1と重なる部分には、それよりも断面積の大きい孔部HL1が形成されている。そして、コンタクトプラグCP1は孔部HL1内を通って配置されることで、第1ダミー導体パターンDM1と接触しないようにして形成されている。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写技術を使用したパターニングの加工性の向上を図る。

【解決手段】ゲート電極MGを形成するための被加工膜8上にCVD法でカーボン膜9aを形成し、続いてSOG膜を形成する。カーボン膜9aをリソグラフィ技術によるレジストパターンでハーフエッチするとともに、幅寸法をWaから半分のWbにスリミングして芯材パターン部9bを形成する。全面にアモルファスシリコン膜14を形成し、エッチバック処理でスペーサパターン14aを形成し、これをマスクとして芯材パターン部9bと共にカーボン膜9aをエッチングしてマスクパターン9を形成する。レジストを芯材パターンとして用いないので高温で加工ができ、加工性が向上する。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜を除去するエッチング中に、異常エッチングを防止する。エッチング工程において加わる水圧や風圧によりガードリングの形状が変形して剥離し、欠陥が発生することを防止する。

【解決手段】半導体装置は、メモリセル領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた周辺回路領域と、ガードリング及び周辺回路領域上に設けられた支持体膜と、周辺回路領域内に設けられたコンタクトプラグとを有する。ガードリングとコンタクトプラグは、同一の導電材料から構成される。

(もっと読む)

パターン形成方法及びパターン形成装置

【課題】生産性に優れたパターン形成方法及びパターン形成装置を提供することを目的とする。

【解決手段】被加工膜上の第1の領域に第1のパターン被覆率である第1のパターンを形成する工程と、第1の領域とは異なる被加工膜上の第2の領域に第2のパターン被覆率である第2のパターンを形成する工程と、を含む。第2のパターンを形成する工程は、ブロックコポリマー含有膜またはポリマー混合膜からなる第2の膜を被加工膜上に形成する工程と、第2の膜を自己組織化する工程と、自己組織化された第2の膜に含有される複数種のポリマーを、少なくとも1種類のポリマーを残すように選択的に除去することにより、第2のパターン被覆率を第1のパターン被覆率に近づけるように第2のパターンを第2の領域に形成する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィ時のフォトマスクの位置合わせを十分な精度で行うことが可能となる位置合わせ用の目合わせパターンを形成することを課題とする。

【解決手段】基板1上に第1絶縁層2を形成する工程と、第1絶縁層2に、1つ以上の接続孔4と、接続孔4よりも幅が広い位置合わせ用の目合わせパターンを形成するための目合わせ孔3と、を形成する工程と、第1絶縁層2の上に、接続孔4が金属で完全に埋まり、かつ、目合わせ孔3が金属で完全に埋まらないよう金属膜5を形成する工程と、金属膜5の上に、少なくとも目合わせ孔3が完全に埋まるように第1フォトレジスト膜6を形成する工程と、第1絶縁層2をストッパーとしてCMP処理を行うことで、第1フォトレジスト膜6及び金属膜5の一部を除去する工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の良好な半導体装置及びその製造方法を提供することにある。

【解決手段】一方の主面に於ける半導体素子領域2内に複数の機能素子が配設された半導体基板1と、半導体基板1の一方の主面上に配設され、複数の配線層3と複数の絶縁層4とを含む多層配線層2と、多層配線層2上に形成された第1の有機絶縁物層6と、第1の有機絶縁物層上に形成され、配線層に電気的に接続された他の配線層と、第1の有機絶縁物層6上に、他の配線層を覆うように形成された第2の有機絶縁物層10とを具備し、半導体素子領域を囲む半導体基板領域に、多層配線層を貫く溝が半導体素子領域を囲繞して配設されており、溝内には、前記有機絶縁物層6、有機絶縁物層10のいずれからも分離された有機絶縁物が配設されている。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】銅を含む層とチタニウムを含む層とをエッチングする時に、非過水系のエッチング液を使用して工程の安定性を向上させる。

【解決手段】本発明は、薄膜トランジスタ表示板に対する発明であって、より詳細には、銅(Cu)とチタニウム(Ti)とをそれぞれ含む二重層配線に形成される薄膜トランジスタ表示板に関し、構造的にはチタニウムを含む層が銅を含む層より幅が広くて、チタニウムと銅とを共にエッチングする段階と、別にエッチングする段階とを含めて製造することを特徴とする。また、ゲート絶縁膜に段差が形成されている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体層を用いた、表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】階段状に加工された複数の導電層と、各導電層に達し深さの異なる複数のコンタクトホールとの接続構造の信頼性を高めた半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基板10の第2のコンタクト領域5上に設けられ、第2のコンタクト領域5と第1のコンタクト領域4との間に段差を形成する下地層45bと、下地層45bを覆って基板10上に設けられ、下地層45b上に積層された上段部81が階段状に加工された下層側積層体91と、下層側積層体91における第1のコンタクト領域4上に積層された下段部82の上に設けられ、階段状に加工された上層側積層体92と、階段状に加工された部分を覆う層間絶縁層62と、層間絶縁層62を貫通し階段状に加工された部分の各々の導電層WLに達して形成されたコンタクトホール内に設けられたコンタクト電極51と、を備えた。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

半導体装置の製造方法

【課題】少ない工程数で樹脂コア及び樹脂保護膜を精度良く形成する。

【解決手段】電極パッド2が形成された基板(半導体基板1)上に、電極パッド2を露出させる開口3aを有する保護絶縁膜3を形成した後、感光性樹脂膜4を形成する。感光性樹脂膜4を多階調マスク5を用いて露光した後で現像する。この現像により、感光性樹脂膜4により構成される樹脂保護膜7と、樹脂保護膜7よりも厚膜の感光性樹脂膜4のパターンにより構成される樹脂コア6と、を一度に形成する。次に、樹脂コア6上から電極パッド2上に亘って配線8を形成する。

(もっと読む)

再配線構造を有する半導体素子とパッケージ、及びその製造方法

【課題】再配線構造を有する半導体素子とパッケージ、及びその製造方法を提供すること。

【解決手段】チップ基板上にチップパッドを形成し、上記チップパッド及び上記チップ基板上にパシベーション層を形成し、上記パシベーション層上に第1絶縁層を形成し、上記第1絶縁層内にリセスと第1開口を形成し、上記パシベーション層内に上記第1開口と垂直に整列された第2開口を形成し、上記リセス、上記第1開口、及び上記第2開口内に再配線ラインを形成し、上記再配線ラインと上記第1絶縁層上に第2絶縁層を形成し、及び上記第2絶縁層内に再配線パッドとして上記再配線ラインの一部を露出させる開口を形成することを含む半導体素子及び半導体素子の製造方法を提供する。

(もっと読む)

段階化キャップ層を有するパターニング可能low−k誘電体配線構造、エアギャップ包含配線構造、および製作方法

【課題】パターニングされた段階化キャップ層の表面上に配される少なくとも1つのパターニングされ且つ硬化されたlow−k物質を含む配線構造を提供する。

【解決手段】少なくとも1つの硬化され且つパターニングされたlow−k物質およびパターニングされた段階化キャップ層は、その中に組み込まれる導電的充填領域を各々有する。パターニングされ且つ硬化されたlow−k物質は、1つ以上の酸感受性イメージング可能基を有する機能性ポリマー、コポリマー、あるいは少なくとも2種の任意の組み合わせのポリマー類もしくはコポリマー類またはその両方を含むブレンドの硬化生成物であり、段階化キャップ層はバリア領域として機能する下部領域および恒久的な反射防止膜の反射防止特性を有する上部領域を含む。

(もっと読む)

配線パターン形成方法および半導体装置の製造方法、半導体装置、データ処理システム

【課題】2回のリソグラフィ工程によるSADP法(Self Align Double Patterning)を用いて、第1配線パターン形成領域には解像限界未満のパターンを含む第1配線パターンを形成し、第2配線パターン形成領域には解像限界以上の通常パターンからなる第2配線パターンを簡便に形成する方法を提供する。

【解決手段】解像限界未満の寸法を有する複数の配線を含む第1配線パターンを、第1リソグラフィ工程と第1リソグラフィ工程の後に実施される第2リソグラフィ工程を用いて形成し、第1のリソグラフィ工程で形成されたパターンに対してのみサイドウォールの形成および除去処理を行い、その後、解像限界以上のパターンを生成する第2リソグラフィ工程を実施する。第2のリソグラフィ工程で形成される解像限界以上の通常パターンに対しては、単純なリソグラフィ工程とすることが可能となる。

(もっと読む)

61 - 80 / 436

[ Back to top ]