Fターム[5F033QQ01]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 露光 (971)

Fターム[5F033QQ01]の下位に属するFターム

反射防止に関するもの (535)

Fターム[5F033QQ01]に分類される特許

21 - 40 / 436

パターン転写方法

【課題】エッチングを行わずに残膜除去処理を行うことが可能なパターン転写方法を提供する。

【解決手段】実施形態のパターン転写方法では、被加工基板上に光反応性樹脂を形成する。さらに、前記方法では、凹凸パターンを有する透明基板と、前記凹凸パターンの表面の一部に形成された遮光膜と、を備えるモールドを前記光反応性樹脂に押印する。さらに、前記方法では、前記モールドが前記光反応性樹脂に押印された状態で、前記モールドを介して前記光反応性樹脂に光を照射する。さらに、前記方法では、前記光反応性樹脂に光を照射した後に、前記モールドが前記光反応性樹脂に押印された状態で、前記光反応性樹脂を加熱する。さらに、前記方法では、前記光反応性樹脂の加熱後に、前記モールドを前記光反応性樹脂から離型する。さらに、前記方法では、前記モールドの離型後に、前記光反応性樹脂を洗浄液で洗浄する。

(もっと読む)

コンピュータ読み取り可能なマスクシュリンク制御プロセッサ

【課題】CD(限界寸法)誤差を低減し、シュリンク処理の形状依存を補正できるパターン化フォトレジスト層を実現するコンピュータ読み取り可能な媒体を備えた装置を提供する。

【解決手段】媒体614は形状レイアウトを受信するためのコンピュータ読み取り可能なコードと、形状レイアウトに対してシュリンク補正を適用するためのコンピュータ読み取り可能なコードとを備える。シュリンク補正を適用するためのコンピュータ読み取り可能なコードは、パターン化層に形状を形成するための角切り欠き部を提供して、線の幅および長さ、形の修正などを調整する。

(もっと読む)

半導体装置の製造方法

【課題】有機膜中における気泡の残存を抑制する。

【解決手段】半導体装置の製造方法は、開口(コンタクトホール36)を有する層間絶縁膜37を形成する工程と、層間絶縁膜37上及び開口内に導体膜39を形成する工程と、導体膜39上に第1感光性有機膜1を塗布形成する工程を有する。この製造方法は更に、第1感光性有機膜1において開口外の部位を露光する工程と、第1感光性有機膜1において開口外の部位を現像により除去する工程と、第1感光性有機膜1において開口内の部位を紫外線により硬化させることによって第1有機膜11を形成する工程を有する。この製造方法は更に、第1有機膜11を覆うように導体膜39上に第2感光性有機膜2を塗布形成する工程と、第2感光性有機膜2を紫外線により硬化させて第2有機膜12を少なくとも第1有機膜11上に形成する工程を有する。

(もっと読む)

シリカ系被膜の形成方法及び電子部品

【課題】密着性に優れ、電気的信頼性の高いシリカ系被膜の硬化物が得られるシリカ系被膜の形成方法を提供する。

【解決手段】本発明のシリカ系被膜の形成方法は、下記一般式(1)で表される化合物を含むシラン化合物を加水分解縮合して得られるシロキサン樹脂と、光酸発生剤及び光塩基発生剤からなる群より選択される少なくとも1種と、シロキサン樹脂を溶解可能な溶媒と、オニウム塩と、を含有する感光性樹脂組成物を基板上に塗布して被膜を得る工程と、パターンマスクを介して被膜を露光する工程と、露光する工程の後に被膜を加熱する工程と、加熱する工程の後に被膜の未露光部を現像によって除去する工程と、除去する工程の後に残存する被膜に紫外線を照射して、パターンを有するシリカ系被膜を得る工程と、を備える。

(もっと読む)

半導体素子の形成方法

【課題】相互接続領域の具現が困難なパッドレイアウトを具現化し、オーバレイマージンを増大できる半導体素子の形成方法を提供する。

【解決手段】半導体基板に被食刻層、第1のハードマスク物質層、第1の分割パターン物質層及び第2のハードマスク物質層を形成して選択食刻し第2のハードマスクパターンを形成し、これをマスクとし第1の分割パターン物質層を食刻し第1の分割パターンを形成する。第1のハードマスク物質層の上部にスペーサ物質層及び第2の分割パターン物質層を形成し、第1の分割パターンが現われるまでスペーサ物質層及び第2の分割パターン物質層を部分食刻しスペーサ物質層を露出させ、複数の第1の分割パターン間に第2の分割パターンを形成し、第1、第2の分割パターンをマスクとしスペーサ物質層及び第1のハードマスク物質層を食刻し第1のハードマスクパターンを形成し、これをマスクとし被食刻層を食刻し微細パターンを形成する。

(もっと読む)

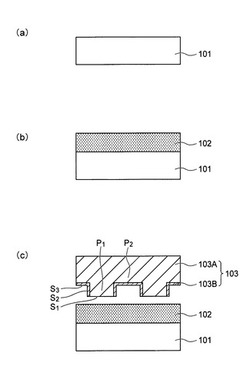

金属薄膜パターンの製造方法

【課題】高温にも耐え得る矩形断面の正確な金属薄膜パターンを、簡単な工程によって製造可能とすること。

【解決手段】下記に示す感光性金属錯体を含む塗布液1を基板10に塗布し(A)マスク20を介して所定の部分のみを露光した(B)。露光によりエステル結合が切れて易溶化した可溶部1Aを(C)、TMAH水溶液により除去し(D)、不溶部1Bを金属化するまで加熱し(E)、Cu等の金属30でメッキする(F)。

【化9】 (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、被加工材にパターンを形成するためのマスクの選択比を向上させ、プロセスコストの低減、歩留りの向上を可能とする。

【解決手段】被加工材上に所定パターンの有機膜を形成し、所定パターンの有機膜中に金属元素を導入し、金属元素が導入された所定パターンの有機膜を用いて、被加工材をエッチング処理する。

(もっと読む)

無電解メッキパターン形成用組成物、塗布液、及び無電解メッキパターン形成方法

【課題】無電解メッキパターンを正確に形成できる無電解メッキパターン形成用組成物、塗布液、及び無電解メッキパターン形成方法を提供すること。

【解決手段】表面を有機物103で修飾されるとともに、前記表面103に触媒金属微粒子105を担持した金属化合物粒子101を含む無電解メッキパターン形成用組成物。前記有機物103としては、3-ヒドロキシ-4-ピロン誘導体、又は1,2-ジオールが挙げられる。前記触媒金属微粒子105としては、パラジウム、銀、白金、ニッケル、及び銅からなる群から選ばれる1種以上の微粒子が挙げられる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細なパターンを含む半導体装置の信頼性を向上する。

【解決手段】本実施形態の半導体装置は、素子形成領域100内の半導体素子と、素子形成領域100内から引き出し領域150内に延在する複数の配線WLと、引き出し領域150内の配線WLに接続されるコンタクト部39と、を具備し、配線WLは、n番(nは1以上の整数)の側壁膜のパターンに対応する(n+1)番目の側壁膜のパターンに基づいて形成され、配線WLの配線幅WW又は素子形成領域150内の配線間隔WDに対応する第1の寸法は、リソグラフィの解像度の限界寸法より小さく、露光波長がλ、レンズの開口数がNA、プロセスパラメータがk1で示される場合、第1の寸法は、(k1/2n)×(λ/NA)以下であり、引き出し領域内で互いに隣接する配線WLの間隔WC2に対応する第2の寸法は第1の寸法より大きい。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

表示装置及びマスク

【課題】マスクの枚数を増やすことなく、ストレージキャパシタの電極間から半導体パターンを除去して高画質化を実現させる表示装置及びその製造方法を提供する。

【解決手段】本発明によるTFTパネルの製造では、半導体パターンとTFTのドレイン電極とを、同じマスクを利用したエッチングで同時にパターニングする。一方、画素電極の直下に形成される絶縁膜のパターニングには別のマスクを利用する。ドレイン電極を覆う絶縁膜の領域では、中央部の全体を感光させ、周辺部を半分の厚みまで感光させる。ストレージ電極の上方を覆う絶縁膜の領域は薄い一部を残して感光させる。ドレイン電極を覆う誘電膜をエッチングしてドレイン電極を露出させるとき、絶縁膜のその薄い一部がその下地の誘電膜を保護する。その後、絶縁膜のその薄い一部を画素電極の一部に置換し、保護された誘電膜を隔ててストレージ電極と対向させる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置を構成する配線の信頼性向上を図る。

【解決手段】テトラメチルシランガスの流量を通常条件よりも下げて形成したSiCN膜SCN1(4MS↓)と、このSiCN膜SCN1(4MS↓)上に形成され、通常のテトラメチルシランガスの流量で形成したSiCN膜SCN2と、このSiCN膜SCN2上に形成されたSiCO膜SCOからバリア絶縁膜を構成する。これにより、耐透水性の向上と低誘電率化をバランス良く実現することができる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い歩留りで製造し得る半導体装置の製造方法を提供する。

【解決手段】ゲート配線16aを形成するのと同時に形成された位置合わせマーク16fに対して位置合わせして、コンタクトホールの第1の部分パターン61a1をゲート配線の一部と重なり合うようにフォトレジスト膜に露光する工程と、活性領域11bを形成するのと同時に形成された位置合わせマーク11fに対して位置合わせして、コンタクトホールの第2の部分パターン61a2を活性領域の一部と重なり合うようにフォトレジスト膜に露光する工程と、フォトレジスト膜を現像し、第1の部分パターンと第2の部分パターンとが露光された箇所に開口部を形成する工程と、フォトレジスト膜をマスクとして絶縁膜をエッチングし、ゲート配線とソース/ドレイン拡散層20とに達するコンタクトホールを形成する工程とを有している。

(もっと読む)

半導体装置

【課題】貫通電極の形成に時間を要さず、貫通電極内でのボイドの発生を抑制できる半導体装置、およびこの半導体装置の製造方法を提供すること。

【解決手段】半導体装置1は、孔111が形成された絶縁性あるいは半導体の層11と、層11の孔111内に設けられた貫通電極12と、を備える。貫通電極12は、シード層121と、めっき層122と、を備える。シード層121は、孔111の底面111Aを覆う。また、シード層121は、孔111の側面111Bのうち、孔111の開口から、孔111の開口と孔111の底面111Aとの間の所定の位置までの第1の領域を未被覆とし、この第1の領域(未被覆領域)111B1を除いた第二の領域を被覆している。めっき層122は、シード層121と、未被覆領域111B1の少なくとも一部を覆う。

(もっと読む)

半導体装置の製造方法

【課題】レジストの膜減りによって残すべき配線がエッチングされることを防止すると共に、露光機による配線パターニング時のフォーカスずれを抑制し、配線の線幅にバラツキが生じることを防止する。

【解決手段】スクライブライン内において、スクライブラインの両側では層間絶縁膜2、4、6が存在せず半導体基板1の表面が露出する領域を設け、スクライブラインの中央位置、つまり溝Tの間に挟まれた領域には層間絶縁膜2、4、6を残す。これにより、スクライブラインとチップとの境界位置近傍において、第3配線層7を形成する際のマスクとして用いるレジスト21が膜減りすることを抑制できる。したがって、レジスト21の膜減りによって残すべき配線がエッチングされることを防止できると共に、露光機による第3配線層7のパターニング時のフォーカスずれを抑制でき、第3配線層7の線幅にバラツキが生じることを防止することが可能となる。

(もっと読む)

配線又は電極の形成方法、電子デバイス及びその製造方法

【課題】下地にダメージを与えず、また、電極材料のゴミの再付着も防止される配線又は電極の形成方法と、この配線又は電極の形成方法により配線又は電極を形成する電子デバイス及びその製造方法を提供する。

【解決手段】下地2上に第1のレジスト層1を形成し、開口部5を形成し、導電材料層3を成膜する。導電材料層3の全体を覆う第2のレジスト層4を形成し、該開口部5以外の導電材料層3上の第2のレジスト層4を除去することにより、該開口部5の導電材料層3を覆う保護レジスト層4’を形成する。該保護レジスト層4’で覆われていない導電材料層3を除去し、次いで保護レジスト層1,4’を除去することにより、残留した導電材料3よりなる配線又は電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】シェアードコンタクトの接触不良を防止して、半導体装置の製造歩留まりを向上させることのできる技術を提供する。

【解決手段】高密度版回路における電界効果トランジスタTr3のゲート電極G3と電界効果トランジスタTr4のゲート電極G4とのピッチは、高速版回路における電界効果トランジスタTr1のゲート電極G1と電界効果トランジスタTr2のゲート電極G2のピッチよりも小さいが、シェアードコンタクトホールSCが達する部分のゲート電極G3に切欠を設けることにより、シェアードコンタクトホールSCと不純物領域S/Dとの接触面積を広くする。

(もっと読む)

半導体基板への有機膜パターンの直接描画プロセスにおける前処理方法

【課題】直接描画法によりレジストの膜パターンやパッシベーション用などの有機膜パターンを形成する際に発生し易い描画性や密着性の問題を防ぐことのできる半導体基板への有機膜パターンの直接描画プロセスにおける前処理方法を提供すること。

【解決手段】相互に異なる材料で構成された複数のパターン膜2、3、4で覆われた半導体基板1表面上に、前記複数のパターン膜2、3、4上に跨って積層される有機膜パターン5を直接描画法により形成する際に、前処理として前記半導体基板1表面を、プラズマ生成ガスとして酸素と窒素を用いてアッシングし、続いて水素と窒素をプラズマ生成ガスとして用いてクリーニング処理を行う。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】スルーホールの微細化による半導体装置の高集積化と、スルーホール内に埋め込まれる導体のカバレッジ性と、を両立させる。

【解決手段】半導体装置は、下層配線2と、下層配線2上に形成され、下層配線2の上面を露出させる開口31を有する第1絶縁膜(例えば、有機絶縁膜3)と、第1絶縁膜上に形成され、スルーホール5が形成された第2絶縁膜(例えば、無機絶縁膜4)とを有する。半導体装置は、更に、スルーホール5に埋め込まれ、下層配線2と電気的に接続された導体9を有する。開口31は、上側に向けて拡径するテーパー形状に形成されている。スルーホール5の側壁5aの少なくとも下端は、開口31の側壁31aを構成する傾斜面の上に位置している。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを特徴としている。

(もっと読む)

21 - 40 / 436

[ Back to top ]