Fターム[5F033QQ01]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 露光 (971)

Fターム[5F033QQ01]の下位に属するFターム

反射防止に関するもの (535)

Fターム[5F033QQ01]に分類される特許

121 - 140 / 436

二回のカット工程によって多結晶シリコンのライン端部短縮の問題を解決する方法

【課題】ゲートストリップを二回のカット工程によって端部を改善する製造方法の提供。

【解決手段】第1アクティブ領域40と、第2アクティブ領域42とを有する基板を提供するステップと、基板にゲート電極層を形成するステップと、第1ゲートストリップ60と、第1ゲートストリップに実質的に平行する第2ゲートストリップ62と、第1アクティブ領域と第2アクティブ領域の間に位置して、第1ゲートストリップと第2ゲートストリップに平行していないが、互いに接続する犠牲ストリップ66とを残すように、ゲート電極層をエッチングするステップと、第1ゲートストリップと第2ゲートストリップの一部を覆い、犠牲ストリップ及び第1ゲートストリップと第2ゲートストリップの一部を開口部に露出させる遮蔽部を形成するステップと、開口部に露出される犠牲ストリップ及び第1ゲートストリップと第2ゲートストリップの一部をエッチングするステップを含む。

(もっと読む)

半導体装置の製造方法

【課題】側壁加工プロセスを用いて形成されたラインアンドスペースパターンを備える構成について、生産性の向上を可能とする、半導体装置の製造方法を提供すること。

【解決手段】第1のピッチの第1の層を形成し、第1の層の側壁に第2の層を形成し、第2のピッチのライン部及びスペース部を備える第1のパターン構造体を形成し、第1のパターン構造体のスペース部のうち、第1の層のスペース部に由来する第1のスペース部の幅Sxと、第1の層のライン部に由来する第2のスペース部の幅Syとから、第1のパターン構造体のライン部の位置ずれ量を計測し、第1のパターン構造体と、第1のパターン構造体に重ね合わせて形成される第2のパターン構造体との合わせ規格を、位置ずれ量に基づいて動的に補正し、第1のパターン構造体及び第2のパターン構造体の合わせずれが、補正後の合わせ規格に適合するか否かを判定することを含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置における基板貫通電極の形成において、貫通電極形成用穴内部にバリア層やめっきのためのシード層を成膜する際、貫通電極穴内部の成膜レートと、基板平面部の成膜レートが大きく異なるために、貫通電極形成用穴内部で所定の膜厚を得ようとすると、基板平面部には必要以上の厚みをもった膜が形成されてしまう。結果として、後工程でのウエットエッチングによる配線パターニングの際に、基板横方向へのエッチング液の入り込みによる大幅な寸法シフトが発生し、微細化の妨げとなっている。

【解決手段】貫通電極形成用穴の開口部を除く基板平面部にフォトレジストを形成してから成膜を行い、成膜後にフォトレジスト表面に付着した膜と共にフォトレジストを除去することで、貫通電極形成用穴内部に付着した薄膜は残したまま基板平面部を露出され、改めて基板平面部に必要分だけ成膜を行うことで課題を解決する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】溝の交差部分の中央部に窪みが形成されることを抑制でき、かつ半導体装置の歩留まりが低下することを抑制できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、基板100に第1の溝110及び第1の溝110と交差する第2の溝120を形成する工程と、基板100に対して成膜処理を行うことにより、第1の溝110内及び第2の溝120内に膜200を埋め込む工程と、基板100上に位置する膜200を除去する工程とを備える。そして第1の溝110及び第2の溝120を形成する工程において、第1の溝110と第2の溝120の交差部分130に、平面視において交差部分130の角の一つから交差部分130の中央に向けて延伸する凸部140を形成する。

(もっと読む)

薄膜トランジスタ、表示装置、およびそれらの作製方法

【課題】薄膜トランジスタの電気特性の信頼性を高めることが可能な薄膜トランジスタ及びその作製方法を提供する。また、画質を向上させることが可能な表示装置及びその作製方法を提供する。

【解決手段】また、ゲート電極と、ゲート電極上に形成されるゲート絶縁層と、ゲート電極に重畳し、且つゲート絶縁層上に形成される酸化物半導体層と、ゲート絶縁層及び酸化物半導体層上に形成される配線と、酸化物半導体層及び配線に接する有機樹脂層とを有する薄膜トランジスタである。

(もっと読む)

半導体装置の製造方法

【課題】芯材パターンの側壁に形成するマスク材を利用したパターン形成において工程数を削減できる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、露光により酸を発生する酸発生剤を含む芯材パターン15を下地膜上に形成する工程と、芯材パターン15における長手方向の端部15aを除く部分を選択的に露光する工程と、芯材パターン15から酸の供給を受けて架橋可能なマスク材16を芯材パターン15を覆うように下地膜上に供給する工程と、マスク材16をエッチバックして、芯材パターン15の上面を露出させると共に、マスク材16における芯材パターン15の端部15aに形成された部分を除去し、芯材パターン15の側壁に形成されたマスク材側壁部16aを残す工程と、芯材パターン15を除去し、下地膜上に残されたマスク材側壁部16aをマスクにして下地膜を加工する工程と、を備えた。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置に含まれる半導体基板と当該半導体基板に形成される貫通孔(TSV)を含む配線との間の絶縁性を良好に保つことができる半導体装置の製造方法を提供する。

【解決手段】

貫通孔の内壁に形成された絶縁膜の開口底部に対応する部分を除く部分をエッチングレジストで被膜し、当該エッチングレジストをマスクとしたエッチングにより当該絶縁膜を除去して電極パッドを露出させた後、導電層を形成して配線する。

(もっと読む)

半導体装置の製造方法

【課題】寸法を選択的かつ適切に制御した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、被加工膜上にレジスト膜を形成する工程と、前記レジスト膜を露光する工程と、前記レジスト膜を現像してレジストパターンを形成する工程と、前記レジストパターンの特定箇所に選択的にエネルギー線を照射して前記レジストパターンの前記特定箇所に酸性成分を発生させる工程と、記酸性成分により架橋反応を生じる架橋材を含む膜を、前記酸性成分が発生したレジストパターン箇所を覆うように、前記被加工膜上に形成する工程と、前記架橋材と前記レジストパターンを反応させて、前記レジストパターンの一部に架橋層を形成する工程と、前記レジストパターンと前記架橋層をマスクに前記被加工膜を加工する工程と、を含む。

(もっと読む)

電気的固体装置の製造方法、電気的固体装置、および電気光学装置

【課題】ウエットエッチングを採用した場合でも、未エッチング部分を発生させずに微細なパターンを形成することができる電気的固体装置の製造方法、電気的固体装置、および電気光学装置を提供すること。

【解決手段】電気光学装置の素子基板上に、スリット7bを備えた透光性の画素電極7aを形成するにあたって、透光性導電膜7の上にレジストマスク96を形成した後、ウエットエッチングを行なう。レジストマスク96において、マスク開口部96bを挟むマスク線状部96eの側面部96fは斜め上向きのテーパ面になっている。

(もっと読む)

表示装置及びその製造方法

【課題】CVD装置への出し入れ回数を減らした表示装置の製造方法および表示装置を提供すること。

【解決手段】本発明にかかる表示装置の製造方法は、絶縁基板上に第1の電極膜と第2の電極膜とを含む導電層、第1の絶縁層、半導体膜、第2の絶縁層および保護層を形成する工程と、半導体膜の上方の第1の領域に配置される所定の厚さの第1のレジスト膜と、第2の電極膜の上方の第2の領域に配置される開口部と、それら以外の領域に配置される厚い第2のレジスト膜と、を保護層上に形成する工程と、第2の領域下をエッチングする工程と、第1のレジスト膜をアッシングにより除去する工程と、第1の領域下に半導体膜に達する第1の孔を形成し、かつ第2の領域下に第2の電極膜に達する第2の孔を形成する工程と、第2のレジスト膜を除去する工程と、半導体膜および第2の電極膜と接続される配線を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜に形成する配線溝および接続孔が互いに位置ずれするのを抑制しながら、製造の容易化を図ることが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、レジスト14および15を順次塗布する工程と、マスク20を介してレジスト15に対する露光を行った後、シリル化部15aおよび15bを形成する工程と、シリル化部14aを形成する工程と、シリル化部15aを除去し、レジスト15および14をパターニングした後、レジスト15および14をマスクとして絶縁膜13をエッチングすることによって接続孔13bを形成する工程と、シリル化部14aを除去し、レジスト14をパターニングした後、レジスト15をマスクとして絶縁膜13をエッチングすることによって配線溝13aを形成する工程とを含んでいる。

(もっと読む)

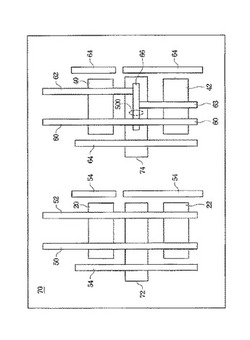

半導体装置及び半導体装置の製造方法

【課題】繋ぎ露光において、マスクパターンの一端部を幅広に形成したマスクを使用しなくても、マスクの相対的な位置ずれに伴う配線抵抗の増大や配線信頼性の低下などの電気的な特性劣化を抑制する。

【解決手段】本発明の半導体装置は、半導体基板上で隣り合う第1の露光領域及び第2の露光領域のうち、第1の露光領域に第1の露光マスクを用いて形成された第1配線パターン101と、第1配線パターン101と繋ぎ合わせるための配線パターンとして、第1配線パターン101と同層でかつ第2の露光領域に第2の露光マスクを用いて形成された第2配線パターン102と、第1配線パターン101と第2配線パターン102との繋ぎ合わせ部分に形成されたビア103,104と、ビア103,104の間に形成された繋ぎパターン105とを備える。

(もっと読む)

半導体素子の微細パターンの形成方法

【課題】複数の物質層間の溶解度差を利用してダブルパターニングを具現する半導体素子の微細パターンの形成方法を提供する。

【解決手段】半導体素子の微細パターンの形成方法は、基板100上に、空間を介して相互に離隔されている複数の第1マスクパターン120を、基板100の主面と平行方向に形成するステップと、溶解剤に対して第1溶解度を有する第1物質からなる複数のキャッピング層130を、複数の第1マスクパターン120のそれぞれの側壁及び上面に形成するステップと、溶解剤に対して第1溶解度より低い第2溶解度を有する第2物質からなる第2マスク層を、空間内に形成するステップと、溶解剤を利用してキャッピング層130を除去し、かつ、第2マスク層の一部を除去した後、空間に残った第2マスク層の残留部分を、複数の第2マスクパターン140Aとして形成するステップと、を含む。

(もっと読む)

半導体装置およびフォトマスク

【課題】シェアードコンタクトホールの開口不良を抑制できる半導体装置およびフォトマスクを提供する。

【解決手段】シェアードコンタクトホールSC1、SC2は、ゲート電極層GE1、GE2とドレイン領域PIRとの双方に達している。平面視において、ゲート電極層GE1、GE2の一方側壁E2が、一方側壁E1の仮想延長線E1aよりも他方側壁E4側にずれて位置している。平面視において、ゲート電極層GE1、GE2のシェアードコンタクトホールSC1、SC2が達する部分の線幅D1の中心線(C2−C2)が、ゲート電極層GE1、GE2のチャネル形成領域CHN1、CHN2上に位置する部分の線幅D2の中心線(C1−C1)に対してずれて位置している。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の面内方向における構成部材間の距離を短縮し、且つ所望の位置に良好な位置精度で構成部材を形成する半導体装置の製造方法を提供すること。

【解決手段】第3の構成部材のうち、長手方向における第1の構成部材と第2の構成部材との間に対向する位置から長手方向における第1の構成部材側の端部までの第1領域と、第1の構成部材とを形成するための第1のマスクパターンを半導体基板上に同時にリソグラフィにより転写する工程と、第3の構成部材のうち第1領域外の領域を含む第2領域と、第2の構成部材を形成するための第2のマスクパターンを半導体基板上に同時にリソグラフィにより転写する工程と、第1のマスクパターンと第2のマスクパターンとを用いて半導体基板上に第1の構成部材と第2の構成部材と第3の構成部材とを形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】 サイズが異なる必要半導体装置形成領域22aおよび不必要半導体装置形成領域22b、22cを有する半導体ウエハを、必要半導体装置形成領域22aの4辺に沿うダイシングストリート23に沿ってダイシングブレードで切断することにより、必要半導体装置形成領域22aを有する半導体装置を得る半導体装置の製造方法において、ダイシングブレードに銅の目詰まりが生じないようにする。

【解決手段】 不必要半導体装置形成領域22b、22cにおいては、ダイシングストリート23およびその両側に対応する領域を除く領域にのみ銅からなる柱状電極14を形成し、当該ダイシングストリート23およびその両側に対応する領域には柱状電極14は形成しない。これにより、ダイシングブレードに銅の目詰まりが生じないようにすることができる。この場合、半導体ウエハ上に複数層の低誘電率膜と同数層の配線とを交互に積層して形成し、その上に絶縁膜を介して形成された上層配線の接続パッド部上に柱状電極14を形成する。

(もっと読む)

半導体装置の製造方法

【課題】第1の再配線層のビア部内にレジスト膜を残存させることなく、第1の再配線層とビア部を介して電気的に接続される第2の再配線層を所望のパターンで形成することができる半導体装置の製造方法を提供する。

【解決手段】第2のレジスト膜34の第2の再配線層22が形成される領域に対応する領域Aに、露光光38を照射する。続けて、第2のレジスト膜34の第2の開口部20aが形成された領域に対応する領域Bに、露光光38を照射する。領域Aの内側に在る領域Bの第2のレジスト膜34は多重露光され、露光が深さ方向まで行き渡ることになる。現像処理により露光された第2のレジスト膜34を除去して、第2のレジスト膜34を所望の再配線パターンにパターニングする。第2の開口部20a内のレジスト膜34や、第1のビア部18aの凹部内のレジスト膜34も除去される。

(もっと読む)

半導体装置、その半導体装置の製造方法及びパワーモジュール

【課題】絶縁層を厚くして電極間の寄生容量を低く抑えることができ、かつ、当該絶縁層に精度良く開口部を形成して作製される小型の半導体装置、その半導体装置の製造方法、及びその半導体装置を含むパワーモジュールを提供する。

【解決手段】セル160は、基板104と、基板104上に形成されるドレイン電極180、ソース電極182、及びゲート電極184と、基板104及び各電極上に形成され、ドレイン電極180の表面を露出する開口部220が形成された絶縁層142とを含む。開口部220は、ドレイン電極180の表面から絶縁層142の表面に向かってその径を広げながら所定高さまで立上がる壁面222と、基板104の表面から当該所定高さで基板104の表面に平行となった踊り場状の平坦面224と、平坦面224から絶縁層142の表面に向かってその径を広げながら立ち上がる壁面226とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】露光条件が最適化される領域の配線と異なる方向の配線を必要とする領域の露光マージン不足を回避する。

【解決手段】半導体基板と、

前記半導体基板上に形成された層間絶縁膜と、

前記層間絶縁膜上の第1の領域において、第1のデザインルールを適用して形成された、特定方向に沿って走る、複数の第1の配線と、

前記層間絶縁膜上の第2の領域において、前記第1のデザインルールと同じ第2のデザインルールを適用して形成された、前記特定方向に沿って走る、複数の第2の配線と、

前記層間絶縁膜中に形成され、同一電位となるべき少なくとも2つの前記第2の配線を電気的に接続して所望の配線パターンを形成する、接続部材と、

を備える。

(もっと読む)

フォトレジストの縁部のバリの形成方法とアレイ基板の製造方法

【課題】フォトレジストの縁部のバリの形成方法とアレイ基板の製造方法に関する。

【解決手段】当該アレイ基板の製造方法は、基板にゲート・ラインとゲート電極パターンを形成するステップと、データ・ラインと、ソース電極と、ドレイン電極と、TFTチャネル領域パターンとを形成し、フォトレジストを残し、パッシべーション層を堆積し、剥離工程によってフォトレジスト及びその上のパッシべーション層を除去するステップと、フォトレジストを塗布し、フォトレジストに山状の縁部のバリを形成し、透明導電薄膜を堆積し、剥離工程によってドレイン電極に直接に接続する画素電極パターンを形成する。

(もっと読む)

121 - 140 / 436

[ Back to top ]