Fターム[5F033QQ09]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングの対象 (10,331) | 絶縁膜 (5,059)

Fターム[5F033QQ09]に分類される特許

61 - 80 / 5,059

半導体装置

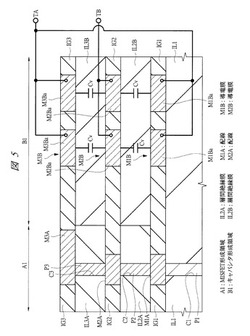

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

半導体装置およびその作製方法

【課題】ノーマリーオフの電気特性を有し、オン電流の高い、酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを用いた高速動作が可能な半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳して設けられたゲート電極と、少なくともゲート電極を覆って設けられた、開口部を有する層間絶縁膜と、層間絶縁膜上に設けられ、開口部を介して酸化物半導体膜と接する配線と、を有し、少なくとも酸化物半導体膜と配線とが接する領域の、下地絶縁膜および酸化物半導体膜の間に、絶縁膜および絶縁膜上に設けられたバッファ層を有する半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】レジスト層、中間層、レジスト層のパターン形状をさらに良好にする半導体装置の製造方法を提供する。

【解決手段】下層フォトレジスト7、無機材料の中間層8、上層フォトレジスト9を形成し、上層フォトレジスト9をパターニングして上層レジストパターン9aを形成し、半導体基板1をチャンバー内の下部電極上に設置し、チャンバー内に二酸化硫黄ガス、酸素ガスを有する第1反応ガスを導入してプラズマを発生させるとともに下部電極への高周波電力の供給を切断して上層レジストパターン9aをトリミングし、第1反応ガスを第2反応ガスに置換するとともに下部電極に高周波電力を供給して上層レジストパターン9aをマスクにして中間層8をエッチングして中間層パターン8aを形成し、第2反応ガスを第3反応ガスに置換してプラズマを発生させるとともに下部電極に高周波電力を供給して中間層パターン8aをマスクにして下層フォトレジスト層7をエッチングする。

(もっと読む)

電子装置およびその製造方法

【課題】信頼性の高いコンタクト構造を提供する。

【解決手段】電子装置は第1の絶縁膜と、前記第1の絶縁膜の表面に形成された配線溝と、Cuよりなり前記配線溝を充填する配線パタ―ンと、前記配線パタ―ンの表面に形成され、Cuよりも大きな弾性率を有する金属膜と、前記第1の絶縁膜上に形成された第2の絶縁膜と、Cuよりなり、前記第2の絶縁膜中に形成され、前記金属膜とコンタクトするビアプラグと、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】クラックの発生を抑制できるとともに、SOG膜の剥離を抑えることが可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体素子が形成された半導体基板3上に、SOG膜を含む層間絶縁膜10が形成されており、この層間絶縁膜10を介して、配線層12a〜12dが半導体素子と電気的に接続されている。さらに、一方面側がボンディング接続されるパッド部12d(第4配線層12d)と、層間絶縁膜10に配置されると共に配線層12a〜12cを接続するビアホール15a〜15cと、ビアホール15a〜15c内に埋め込まれる導電層16a、16bとを有している。そして、ビアホール15a〜15cは、パッド部12dよりも下方に設けられており、導電層16a、16bの少なくとも一部は、内部に空洞部17を有している。

(もっと読む)

半導体装置、モジュール、及び電子機器

【課題】大量生産上、大型の基板に適している液滴吐出法を用いた製造プロセスを提供す

る。

【解決手段】液滴吐出法で感光性の導電膜材料液を選択的に吐出し、レーザ光で選択的に

露光した後、現像またはエッチングすることによって、レーザ光で露光した領域のみを残

し、吐出後のパターンよりも微細なソース配線およびドレイン配線を実現する。TFTの

ソース配線およびドレイン配線は、島状の半導体層を横断して重ねることを特徴としてい

る。

(もっと読む)

半導体装置の製造方法、及び、半導体装置

【課題】 より一層、製品の歩留まりを向上させることのできる半導体装置の製造方法を提供する。

【解決手段】 本開示の半導体装置の製造方法では、まず、第1半導体部及び第2半導体部を貼り合わせた半導体部材の一方の面上に形成された絶縁膜30上に、所定の薬液で処理された際に該所定の薬液が絶縁膜に浸透しないような耐性を有するストッパー膜31を形成する。次いで、半導体部材のストッパー膜31側に、第1半導体部及び第2半導体部を電気的に接続するためのCu配線接合部34を形成する。次いで、Cu配線接合部34上にCu拡散防止膜34を形成する。次いで、Cu配線接合部34の形成領域以外の領域のCu拡散防止膜33を除去して該領域に存在する不要なCu部210,211を露出させる。そして、所定の薬液を用いて、不要なCu部210,211を除去する。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、および電子機器

【課題】裏面照射型の固体撮像装置において、受光面と遮光膜との距離を小さくすることにより、光電変換部での受光特性の向上を図る。

【解決手段】光電変換部が配列形成された画素領域を有するセンサ基板と、センサ基板において光電変換部に対する受光面とは逆の表面側に設けられた駆動回路と、画素領域における受光面上に設けられた遮光膜と、遮光膜を覆って設けられた保護絶縁膜と、画素領域の外側の周辺領域において、保護絶縁膜からセンサ基板にかけて埋め込まれ駆動回路に接続された複数の貫通ビアを備えた固体撮像装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビア層絶縁膜にビア用の孔を形成する工程において、シールリングのうちビア層絶縁膜に位置する部分に、導体を埋め込むための溝を形成しないで済むようにする。

【解決手段】ビア層絶縁膜40及び第2配線層絶縁膜50にはシール溝121が形成されている。また、エッチングストッパー層30には複数の孔31が形成されている。第2シール導体パターン120は、複数の孔31及びシール溝121に埋め込まれている。そして、エッチングストッパー層30は、シール溝121の底面に位置する部分が薄膜部32となっており、シール溝121が形成されていない部分と比較して薄くなっている。

(もっと読む)

半導体装置

【課題】多層配線プロセスでSOGエッチバックにて平坦化を行なうプロセスにて、ヒューズ開口部に起因する水分の浸入における長期信頼性の劣化を防止する半導体装置の製造方法を提供する。

【解決手段】ヒューズ開口部からの水分侵入を防ぐためのメタル1層目のガードリングの下部まで多結晶シリコンが伸びているヒューズ形状にする。これによりヒューズの電極をとるためのメタル配線とガードリングのメタル配線の高さがそろい、SOG層がIC内部に到達することを防ぐことが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】外部からの不純物等に対する耐性を向上することができる半導体装置及びその製造方法を得る。

【解決手段】GaAs基板1上に下層配線2が設けられている。GaAs基板1及び下層配線2上に樹脂膜4が設けられている。樹脂膜4は、下層配線2上に開口5を有する。下層配線2及び樹脂膜4上にSiN膜6が設けられている。SiN膜6は、開口5内に開口7を有する。下層配線2及び樹脂膜4の一部上に上層配線8が設けられている。上層配線8は、開口5,7を介して下層配線2に接続されたTi膜8aと、Ti膜8a上に設けられたAu膜8bとを有する。上層配線8及び樹脂膜4上にSiN膜9が設けられている。SiN膜9は、樹脂膜4上においてSiN膜6に付着している。SiN膜6,9はTi膜8aの周囲を保護する。

(もっと読む)

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

半導体装置

【課題】高温環境下で使用することができる半導体装置を提供する。

【解決手段】第1インナー電極と第2インナー電極との積層からなるワイヤー接続領域を合金化防止溝によって第1アウター電極および第2アウター電極と分離することでワイヤーボンディング界面から成長したAu−Al合金層の進行を抑制し、半導体装置表面のパッシベーション膜のクラックを防止する。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】異なる深さに位置する導電層を露出させた接続孔を有する半導体装置において、浅い導電層の過剰なエッチングを防止し、半導体装置の歩留まりの向上を図る。

【解決手段】第1導電層および第1導電層よりも深く配置された第2導電層を内部に有する基板上に、第1導電層および第2導電層の上部を露出する開口を有する大径レジストパターンを形成する。この大径レジストパターンをマスクにしたエッチングに基づいて、第1導電層を底部に露出させた大径凹部を、基板に形成する。基板上に、第2導電層の上部を露出する開口を大径凹部の形成範囲内に有する小径レジストパターンを形成する。この小径レジストパターンをマスクにしたエッチングに基づいて、第2導電層を底部に露出させた小径凹部を、基板に形成する。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。また信頼性の高い半導体装置を提供する。

【解決手段】チャネル形成領域と、ソース領域またはドレイン領域を有する島状半導体膜131と、ゲート絶縁膜と、ゲート電極103とを有する薄膜トランジスタと、層間絶縁膜と、層間絶縁膜中に形成され、ソース領域またはドレイン領域の一方に達する複数のコンタクトホールを含む第1のコンタクトホール142と、ソース領域またはドレイン領域の他方に達する第2のコンタクトホール141とを有し、第2のコンタクトホール141の径は、第1のコンタクトホール142に含まれる複数のコンタクトホール142のそれぞれの径より大きく、第1のコンタクトホールの底面積の合計と、第2のコンタクトホール141の底面積は等しい半導体装置に関する。

(もっと読む)

半導体装置及び半導体装置の形成方法

【課題】配線層間に絶縁物が堆積しない配線の形成方法を提供する。

【解決手段】半導体装置10は、第1絶縁体層14と、第1絶縁体層14上に間隔を空けて配置された複数の配線層18a、18bと、配線層18a、18bの側面上に形成された水素を吸蔵及び放出する水素吸蔵層19b、19c、19d、19eと、複数の配線層18a、18b上に、配線層間の溝20b上を跨ぐように形成された第2絶縁体層23と、を備えた配線を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグが微細化しても埋め込み不良が生じることなく、低コストで形成することができ、さらに種々の半導体装置に適用可能であるプラグ及びその形成技術を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板上に酸化シリコン膜を形成し、酸化シリコン膜にビアを形成し、ビア内側に密着層を形成し、密着層上にシリコン層を形成し、タングステンを含むガスをシリコン層と反応させることにより、ビアに埋め込まれたタングステン膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】配線幅が異なる第1及び第2の配線を有する配線パターンの上に形成された絶縁層を、十分に平坦化すること。

【解決手段】基板上に、第1の配線及び第1の配線よりも配線幅が小さい第2の配線を有する配線パターンを形成する配線形成工程S10と、配線パターンの上から、第1の絶縁層及び第2の絶縁層をこの順に形成する絶縁層形成工程S20と、第2の絶縁層の上に、配線パターンの反転パターンを有するレジストパターンを形成するレジスト形成工程S30と、第2の絶縁層の方が第1の絶縁層よりもエッチングされやすい条件で等方性エッチングするエッチング工程S40と、レジストパターンを除去するレジスト除去工程S50と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】新規な構造のコンタクトプラグを有する半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板と、半導体基板に形成され、ソース/ドレイン領域及びゲート電極を有するトランジスタと、トランジスタのソース/ドレイン領域及びゲート電極を覆う絶縁膜と、絶縁膜中に形成され、トランジスタのソース/ドレイン領域またはゲート電極に接されるコンタクトプラグとを有し、コンタクトプラグは、絶縁膜の厚さ方向に延在しトランジスタのソース/ドレイン領域またはゲート電極に接触する柱部と、柱部の上部から絶縁膜の表面と平行な方向に張り出し上面が平坦化された鍔部とを有する。

(もっと読む)

61 - 80 / 5,059

[ Back to top ]