Fターム[5F033QQ10]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングの対象 (10,331) | 積層膜 (1,279)

Fターム[5F033QQ10]に分類される特許

1,261 - 1,279 / 1,279

半導体装置及びその製造方法

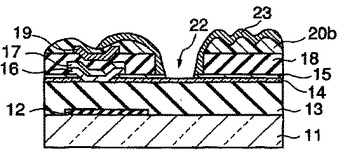

底部電極(11)及び又はキャパシタ誘電体上に導電性平滑化層(16、19)を形成することにより、幾何学的に高くされた電場を低下させると共に、電極を平滑化することで、形成されるMIMキャパシタの信頼性を向上させることができる。一実施形態において、難溶性窒化物で形成された第1のキャッピング層(14)上には、難溶性金属又は難溶性金属リッチ窒化物を含む第1の層(16)が形成される。更に、キャパシタ誘電体上には、難溶性金属(18)又は難溶性金属リッチ窒化物を含む第2の層(19)が形成される。導電性平滑化層(16、19)は、例えば、ゲート電極とゲート誘電体との間のトランジスタ等の他の半導体装置にも使用される。  (もっと読む)

(もっと読む)

製造方法

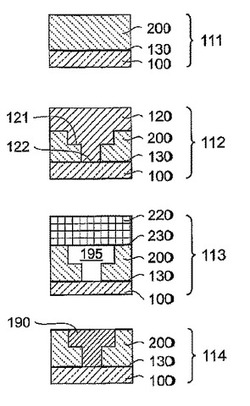

【課題】 基板内に導電性構造体を形成する方法を提供すること。

【解決手段】 表面上に多段階層構造体を形成する方法が記載される。この方法は、表面上に硬化可能な液体層を堆積させるステップと、内部に多層パターンを有するスタンプを液体層に圧入し、該パターンによって定められる多段階層構造体を該液体層内に生成するステップと、液体層を硬化させ、内部に多段階層構造体を有する固体層を生成するステップとを含む。機械的位置合わせを用いて、構造体を形成することになる基板上に離間配置された複数の突出部及びスタンプのパターン内の相補的陥凹部を介して、基板に対するスタンプの光学的位置合わせを強化することができる。

(もっと読む)

液晶表示装置の製造方法

アクティブマトリクス型液晶表示装置の薄膜トランジスタにおける下地電極上の絶縁膜上にフォトエンボッシング材料を用いて凹凸を有する有機膜を形成し、この有機膜にドライエッチングを施して有機膜の膜厚を減少させてコンタクトホール形成領域の絶縁膜を露出させる。その後、露出した絶縁膜にドライエッチングを施してコンタクトホールを形成すると共に下地電極を露出させ、得られた構造上に反射電極を形成して、露出した下地電極と反射電極とを接続する。  (もっと読む)

(もっと読む)

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

集積接続部およびその製造方法

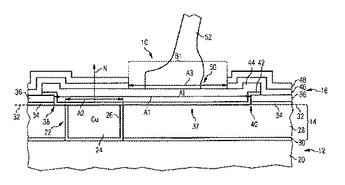

本発明は、電気的に導電性ではない絶縁層(34,36)における切り欠き部(37)に、少なくとも部分的または全体的に配置された外部導電構造部(44)を有する接続部に関する。切り欠き部(37)の底部には、導電性の内部導電構造部(22)が、絶縁層(34,36)の一方側に配置され、コンタクト領域において外部導電構造部と境界を形成している。コンタクト面は、切り欠き部(37)の他方側において、外部導電構造部(44)に配置されている。コンタクト領域とコンタクト面とは、互いに重ならないか、部分的にのみ重なっている。切り欠き部(37)の底部は、法線方向から見ると、コンタクト面の少なくとも半分または全面に重なるように配置されている。その結果、絶縁層(34、36)の段状部分は、コンタクト面と内部導電構造部(22)との間に延びる主要電流路の外側において、切り欠き部(37)の端部に位置する。  (もっと読む)

(もっと読む)

金属−絶縁物−金属キャパシタおよび配線構造

【課題】 金属−絶縁物−金属キャパシタおよび配線構造を提供する。

【解決手段】 ダマシン工程を利用してMIMキャパシタおよび配線構造を含む半導体装置を製造する。前記MIMキャパシタおよび配線構造は静電容量を増やしつつ同じ深さで形成する。

(もっと読む)

溝配線を有する半導体装置および半導体装置の製造方法

【課題】 多層配線において、ショートやビア抵抗増加のような目合わせずれによる問題を回避し、信頼性の高い多層配線を得る。

【解決手段】 半導体装置は、第1配線層(201)と、層間絶縁層(202〜208)とを具備する。第1配線層(201)は、基板の上面側に設けられ、第1配線を含む。層間絶縁層(202〜208)は、前記第1配線層(201)上に設けられ、一方の端を前記第1配線に接続されたビアと、前記ビアの他方の端に接続された第2配線とを含む。前記層間絶縁層(202〜208)はシリコン酸化膜より低い比誘電率を有する。前記層間絶縁層(202〜208)の上部は、下側から順に、シリコン酸化膜(206)、シリコン窒化膜(207)、シリコン酸化膜(208)を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体チップ上に絶縁膜を介して外部端子と再配線とが形成される半導体装置において、従来は外部端子、若しくは再配線からのノイズの影響から電子回路を保護する為、接地電位層を設けていたが、この接地電位層の為に工程が大幅に増加し、さらに、半導体装置の厚さが厚くなってしまう可能性があった。

【解決手段】本発明では、基板上の多層配線、即ち、それぞれが層間絶縁膜を介して積層された複数の層と、それぞれの層内に形成された配線とを有する多層配線の最上位の層内において、配線が配置された領域以外の領域に、定電位が与えられるノードに電気的に接続するメタル部材が形成される。これにより、工程を大幅に増加することなく、かつ、半導体装置の厚さを厚くすることなく、電子回路がノイズの影響を受けてしまう可能性を低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】段差が存在する下地上でAl合金配線を形成するためのエッチング時にイオンシェーディング現象の発生を抑制してAl合金配線の側面が逆テーパー形状となるのを抑制できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、段差を有する下地である層間絶縁膜11上にTi層を形成する工程と、このTi層上にAl層又はAl合金層を形成する工程と、熱処理を行うことにより、Ti層とAl層又はAl合金層を合金化反応させてAl3Ti層5aを形成する工程と、このAl3Ti層5aの上にレジストパターン12を形成する工程と、このレジストパターン12をマスクとしてAl3Ti層5aをエッチングすることにより、層間絶縁膜11上にAl合金配線13を形成する工程と、を具備するものである。

(もっと読む)

配線構造及びその形成方法

【課題】 Cuを含有する材料に代表されるような層間絶縁膜に対する易拡散性の材料を用いて配線を構成した場合に、前記易拡散性の材料の層間絶縁膜への拡散や材料の剥離を確実に防止するとともに、層間容量を低減させ、しかも高い耐酸化性を保持する。

【解決手段】 Cu配線に対応した保護膜として、当該Cuの拡散防止及びビア孔23形成時のエッチングストッパーとしての機能を有し、しかも低誘電率を示す構造の保護膜16を提案する。この保護膜16は、水素化シリコンカーバイド膜(SiC:H膜)21上にシリコン窒化膜(SiN膜)22が積層されてなる2層構成のものである。

(もっと読む)

積層絶縁膜の加工方法及び配線構造の形成方法

【課題】 積層絶縁膜を良好に加工する方法、並びにその方法を用いた配線構造の形成方法を提供すること。

【解決手段】 互いに異なる複数の絶縁膜4、5(更には3)のそれぞれについて少なくとも反応ガスの種類及び/又はその供給量に対するエッチング速度の関係を求めておき、この関係に基づいて反応ガスの供給量を設定してエッチング速度を選択し、エッチングを行う。各絶縁膜のエッチング速度をそれぞれ適切に選択するので、複数の絶縁膜が積層していても、常に良好な加工形状を得ることができる。膜種ごとに異なるエッチング速度の反応ガスの供給量に対する依存性を、複数の絶縁膜の相互間で差別化し、積層絶縁膜のエッチング選択比を目的にあわせて適切に設定する。

(もっと読む)

デュアルダマシンによる半導体装置の製造方法

【課題】 放熱性が良好で、製造コストが低く、微細加工に好適なデュアルダマシンによる半導体装置の製造方法を提供する。

【解決手段】 基板1上に無機層間膜5、有機層間膜6、シリコン酸化膜からなる下部マスク7、シリコン窒化膜からなる上部マスク8を形成し、上部マスク8上にシリコン酸化窒化膜からなり膜厚が20乃至100nmであるカバーマスク10を形成する。そして、反射防止膜11及びレジスト膜12を形成する。次に、レジスト膜12をマスクとして、反射防止膜11、カバーマスク10、下部マスク7をエッチングする。そして、カバーマスク10をマスクとして、有機層間膜6及び無機層間膜5をエッチングしてビアホールを形成する。次に、上部マスク8をマスクとして有機層間膜6をエッチングして配線溝を形成する。

(もっと読む)

配線構造の形成方法

【課題】 絶縁膜及びその上のARL膜に埋め込まれた配線同士の間における短絡を防止する。

【解決手段】 基板100上に形成されたFSG膜109及びARL膜110に複数の配線用溝111を形成した後、各配線用溝111が完全に埋まるようにARL膜110上にバリアメタル膜(窒化タンタル膜112)及び配線用導電膜(銅膜113及び114)を順次堆積する。その後、各配線用溝111の外側の銅膜113及び114を研磨により除去した後、各配線用溝111の外側の窒化タンタル膜112を研磨により除去する。その後、研磨時に研磨パッド及び基板100に付着した異物を同時に除去した後、ARL膜110の表面を研磨する。

(もっと読む)

配線構造及びその形成方法

【課題】 配線遅延を抑止し配線の微細化及び多層配線化を可能とする配線構造、及び当該配線構造の材料に固有の諸問題、例えば一方の材料の他方の材料への溶出等の不都合を解決して、信頼性の高い配線構造を実現する。

【解決手段】 Cu配線101と電気的に接続されるWプラグ102を形成するに際して、

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

半導体チップ、配線基板およびそれらの製造方法ならびに半導体装置

【課題】複数の半導体チップを配線基板に積層しても、半導体チップを積層した半導体装置の厚みおよび基板面積の増大および半導体チップ間の配線長の増加を招かない半導体チップ、その製造方法および半導体装置等を提供する。

【解決手段】半導体基板13と、半導体基板13の第1の面14に形成された第1の外部電極21と、半導体基板13の第2の面17に形成された第2の外部電極22と、半導体基板13に形成された貫通孔16とを有し、貫通孔16は第2の面17となす内角が鈍角をなして形成された斜面15に設けられ、第1の外部電極21と第2の外部電極22とは、貫通孔16の内壁および斜面15を経由して形成された導電パターン19により電気的に接続されている。

(もっと読む)

表示素子用配線、これを利用した薄膜トランジスタ基板及びその製造方法

【課題】 物理的に接着力が向上し、電気的には接触抵抗が良好な特性を有する表示素子用配線及びこれを利用した薄膜トランジスタ基板並びにその製造方法を提供することを目的とする。

【解決手段】 表示素子用配線を、低融点金属の合金元素が少なくとも一つ以上合金されているAg合金で形成する。液晶表示パネルにおいて、このような表示素子用配線を用いてゲート配線22,24,26及びデータ配線65,66,68を形成すれば、接触部で他の導電物質と連結される過程で腐食が発生して素子の特性を低下させるのを防止できる。

(もっと読む)

半導体装置及びその製造方法

【課題】チップサイズパッケージの実装時における信頼性を向上させる。

【解決手段】上面の面積を底面の面積より大きくすると共に、側面をくびれ形状に湾曲させた柱状端子9を形成し、この上に半田ボール12を搭載する。これにより、柱状端子9と半田ボール12の接触面積Sが従来のSに比して大きくできるため、せん断応力に対する強度を向上することができる。また、くびれ形状に湾曲させたことにより、剛性が低減し(つまりしなやかになり)、弾力性が増すことで、応力緩和性能も改善される。

(もっと読む)

配線構造とこれを利用する薄膜トランジスタ基板及びその製造方法

【課題】 銀を利用する低抵抗配線構造を提供する。

【解決手段】

絶縁基板上に、ゲート配線が形成され、ゲート絶縁膜がゲート配線を覆っており、ゲート絶縁膜上に半導体パターン半導体が形成されている。半導体パターン半導体及びゲート絶縁膜の上には、ソース電極及びドレーン電極とデータ線を含むデータ配線が形成されており、データ配線上には、保護膜が形成されている。保護膜上には、接触孔を通じてドレーン電極と連結されている画素電極が形成されている。この時、ゲート配線及びデータ配線は、接着層、Ag層、及び保護層の3重層からなっており、接着層はクロムやクロム合金、チタニウムやチタニウム合金、モリブデンやモリブデン合金、タリウムやタリウム合金のうちのいずれか一つからなり、Ag層は銀や銀合金からなり、保護層はIZO、モリブデンやモリブデン合金、クロムやクロム合金のうちのいずれか一つからなっている。

(もっと読む)

1,261 - 1,279 / 1,279

[ Back to top ]