Fターム[5F033QQ28]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287) | 絶縁膜 (1,171)

Fターム[5F033QQ28]に分類される特許

141 - 160 / 1,171

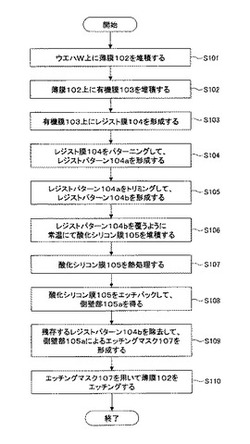

微細パターンの形成方法

【課題】側壁部の形成の基礎となるパターンをレジストにより形成する場合であっても、側壁部の傾きを抑制できる微細パターンの形成方法を提供する。

【解決手段】基板上に形成されたエッチング対象層の上に有機膜を形成する有機膜形成ステップと、有機膜上にレジスト膜を形成し、このレジスト膜をパターニングするパターニングステップと、パターニングされたレジスト膜から露出する有機膜と、パターニングされたレジスト膜とを覆うように酸化シリコン膜を常温にて堆積する堆積ステップと、基板を加熱して酸化シリコン膜に引っ張り応力を生じさせる加熱ステップと、処理ステップの後に、パターニングされたレジスト膜の側壁に酸化シリコン膜が残るように当該酸化シリコン膜をエッチングする第1のエッチングステップと、パターニングされたレジスト膜を除去する除去ステップとを含む、微細パターンの形成方法が開示される。

(もっと読む)

半導体素子及びその半導体素子のパターン形成方法

【課題】 フォトリソグラフィ工程の解像限界内で、具現可能なサイズのパターンを利用して超微細な幅及び間隔を持つ高密度パターンを形成できる配置構造を持つ半導体素子及びその半導体素子パターン形成方法を提供する。

【解決手段】 半導体素子は、コネクション領域に隣接するメモリセル領域を含む基板、メモリセル領域からコネクション領域まで第1方向に延びて配され、第1ライン幅及び第1ライン間隔を持つ複数の第1導電ライン、第1導電ラインそれぞれに連結されるように配され、第2ライン幅及び第2ライン間隔を持つ複数の第2導電ライン、コネクション領域に配され、第1導電ラインに電気的に連結された複数のパッド、を備える。半導体素子上のパターン形成方法は、微細ライン幅及び間隔を提供するために2段階のスペーサ形成工程を含むことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトホールの形状制御が容易な半導体装置の製造方法を得る。

【解決手段】実施形態の半導体装置の製造方法は、基板1上にゲート絶縁膜2、ゲート電極3,4、第1ハードマスク5を形成し、第1ハードマスクをパターンニングして第1マスクを形成し、これをマスクにゲート電極及びゲート絶縁膜を基板が露出するまでエッチングしラインパターンを形成し、露出した基板及び第1マスクを覆うようにライナー膜7を形成する。更にライナー膜に覆われたラインパターンの間隙を有機系絶縁膜で埋め込み、少なくともライナー膜が露出するまで有機系絶縁膜を平坦化してその上に第2ハードマスク9を形成し、第2ハードマスクを第1マスクと交差するようにパターンニングして第2マスクを形成し、第1及び第2マスクをマスクに有機系絶縁膜をライナー膜が露出するまでエッチングしてコンタクトホールを形成する。

(もっと読む)

半導体素子用パターン構造物の形成方法

【課題】ラインパターン構造物の形成方法を提供すること。

【解決手段】ラインパターン構造物及びその形成方法において、ラインパターン構造物は切断部位を含むライン形状を有する少なくとも1つの第1ラインパターンを含む。最外郭に位置する前記第1ラインパターンと隣り合って前記第1ラインパターンと平行した延在ラインと、前記第1ラインパターンの切断部位と隣接する領域で前記第1ラインパターン方向へ向かうように前記延在ラインから突出された少なくとも1つの突出パターンを含む2つの第2ラインパターンを含む。前記ラインパターン構造物は不良が減少し、簡単な工程を通じて形成されてもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】プローブの先端が電極パッドから外れてしまうことによる測定不良を十分に抑制する。

【解決手段】半導体装置(例えば、半導体ウェハ200)は、複数層の配線層と、相互に隣り合う配線層の間に介在する層間絶縁膜と、を含む多層配線層90を有する。更に、多層配線層90上に形成された無機絶縁膜(例えば、酸化膜4と酸化窒化膜5との積層膜)と、無機絶縁膜上に形成された有機絶縁膜6とを有する。更に、多層配線層90の複数層の配線層のうち、最上層でない配線層(例えば、最下層の配線層)に形成された電極パッド40と、有機絶縁膜6、無機絶縁膜、及び、多層配線層90において、電極パッド40上に位置する部位に形成された開口41と、を有する。

(もっと読む)

半導体装置およびその製法

【課題】トレンチ構造のトランジスタセルがマトリクス状に多数個形成され、そのゲート電極に金属膜からなるゲート配線がコンタクトされる半導体装置でも、ゲート耐圧を充分に高くすることができる構造の半導体装置を提供する。

【解決手段】半導体層1に凹溝11が形成され、その凹溝11内にゲート酸化膜4が形成され、その凹溝11内にポリシリコンなどからなるゲート電極5が設けられるトレンチ構造のトランジスタセルがマトリクス状に配列されたセル領域10を有している。そして、金属膜からなるゲート配線9とコンタクトするため、ゲート電極5と連続してゲートパッド部5aが設けられるが、そのゲートパッド部5aが凹溝11と同時に設けられる凹部12内に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間容量を低減する。

【解決手段】半導体装置の製造方法は、基板の上方に絶縁膜を形成する工程と、絶縁膜を貫通する第1の溝及び絶縁膜の内部で終端する第2の溝を絶縁膜に形成する工程と、絶縁膜の内部で終端する配線溝を絶縁膜に形成する工程と、第1の溝の表面及び配線溝の表面に第1の金属膜を形成するともに、第2の溝の上方を覆うように第1の金属膜を形成する工程と、第1の溝及び配線溝に第2の金属膜を埋め込む工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】 メモリセルアレイ領域と周辺回路領域との配線溝の深さを最適化する。

【解決手段】 本発明の一態様の半導体装置の製造方法によれば、レジストパターンをマスクとして芯材膜を加工する工程と、前記芯材膜上に被加工膜とエッチング選択比がある側壁膜を形成する工程と、前記側壁膜を異方性エッチング工程により加工する工程と、前記芯材膜を前記側壁膜と選択的に除去する工程と、第1領域の前記側壁膜上および前記被加工膜上に絶縁膜を第1の膜厚を有するように形成し、第2領域の前記被加工膜上に前記絶縁膜を第2の膜厚を有するように形成する工程と、を備えている。さらに、前記第2領域においてフォトリソグラフィ工程によりレジストパターンを形成する工程と、前記第1領域における前記側壁膜と前記第2領域における前記レジストパターンとをマスクとして前記絶縁膜および前記被加工膜を加工し、前記被加工膜に配線溝を形成する工程と、を備えている。

(もっと読む)

配線構造及び配線構造の形成方法

【課題】配線の洗浄液への溶解を低減する配線構造の形成方法を提供する。

【解決手段】絶縁層13に犠牲配線溝21及び主配線溝31を形成し、犠牲配線溝21及び主配線溝31内にバリア層16を形成し、バリア層16が形成された犠牲配線溝21及び主配線溝31内に導電層17を埋め込んだ後に、絶縁層13上の導電層17の部分を研磨する工程と、犠牲配線溝21及び主配線溝31内の露出したバリア層16及び導電層17の表面を洗浄する工程と、を備え、研磨する工程の後における絶縁層13の平面視において、犠牲配線溝21内のバリア層16の部分の面積と導電層17の部分の面積との比S1が、主配線溝31内のバリア層16の部分の面積と導電層17の部分の面積との比S2よりも大きくなる。

(もっと読む)

窒化物半導体装置

【課題】活性層の上に電極パッドを形成する場合に生じる問題を解決し、オン抵抗の上昇を抑えた窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、活性領域102Aを有する窒化物半導体層積層体102と、活性領域の上に互いに間隔をおいて形成されたフィンガー状の第1の電極131及び第2の電極132とを備えている。第1の電極の上に接して第1の電極配線151が形成され、第2の電極の上に第2の電極配線152が接して形成されている。第1の電極配線及び第2の電極配線を覆うように第2の絶縁膜が形成され、第2の絶縁膜の上に第1の金属層161が形成されている。第1の金属層は、第2の絶縁膜を介して活性領域の上に形成され、第1の電極配線と接続されている。

(もっと読む)

半導体装置の製造方法

【課題】高さのばらつきが低減された埋め込みビット線を有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板内にビット線とワード線を有する半導体装置の製造方法において、半導体基板をエッチングして第1の方向に延在する第1の溝を形成することによって、複数の第1の半導体ピラーを形成する工程と、第1の半導体ピラーの側面の一部に拡散層を形成する工程と、隣接する前記第1の半導体ピラー間の前記第1の溝に、拡散層に接続するビット線を形成する工程と、第1の半導体ピラーと前記ビット線を覆う第1の絶縁膜を形成する工程と、第1の半導体ピラーの少なくとも一部が露出するように前記第1の絶縁膜に、第1の方向に直交する第2の方向に延在する第2の溝を形成する工程と、露出した第1の半導体ピラー上にエピタキシャル層を成長させて第2の半導体ピラーを形成する工程と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ビアを形成するとともに配線を形成する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、まず、第1のパターンを導電体上に形成された被加工材に転写することにより、第1のパターンを有する第1の溝を被加工材の上部に形成する工程を行い。次に、第1のパターンと一部が重なる第2のパターンを被加工材に転写することにより、第1および第2のパターンの和集合からなるパターンを有する第2の溝を被加工材の上部に形成し、第1および第2のパターンの積集合からなるパターンを有し、底部に導電体が露出する孔を被加工材の第2の溝の下に形成する工程を行い。孔内にビアを形成し、第2の溝内に配線を形成する工程を行う、ことを含む。

(もっと読む)

配線基板の製造方法

【課題】コンタクトホールを、生産性良く、低コストで、且つ信頼性良く製造する配線基板の製造方法を提供する。

【解決手段】基板1に第1電極3及び第2電極7が形成される。第1電極3及び第2電極7を連通するように形成された微細穴の側壁部及び底部に、導電膜9を形成してコンタクトホール2を形成する。この配線基板100の製造する際に、微細穴を形成する微細穴形成工程において、微細穴の側壁部の開口端側に相対的に浅い溝からなる第1溝領域4が形成され、微細穴の側壁部の底部側に相対的に深い溝からなる第2溝領域5が形成される。このように区分けした溝領域4,5のうち、第2溝領域5に導電性材料を含有する液体を付与して、導電膜9を形成する。

(もっと読む)

半導体装置

【課題】コンタクト抵抗の上昇を防止することが可能な半導体装置を提供すること。

【解決手段】シリコン基板に形成される複数の拡散領域と、複数の拡散領域にボトム部が接続して形成される複数のコンタクトプラグ33と、ボトム部を含んでシリコン基板上に形成されるアモルファスカーボン膜24とを備え、ボトム部はアモルファスカーボン膜24を貫通して拡散領域に接合される。アモルファスカーボン層24をコンタクトプラグ33形成時のエッチングストッパ層として用いることで、拡散領域がオーバーエッチングによりダメージを受けることが防止される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】研磨工程を含む新規な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、絶縁膜を形成する工程と、絶縁膜に、第1の深さを有するダミー溝と、第1の深さよりも深い第2の深さを有する配線溝と、配線溝の底面に配置されるビアホールとを形成する凹部形成工程と、ダミー溝内、配線溝内、ビアホール内、及び絶縁膜上方に、導電材を堆積させる工程と、絶縁膜上方の導電材を研磨除去する工程とを有する。

(もっと読む)

半導体装置

【課題】ゲートコンタクトプラグ形成のためのコンタクトホールの深さを適切に制御可能とする。

【解決手段】半導体装置1は、活性領域ARを囲む第1の絶縁体ピラー21と、第1の絶縁体ピラー21の活性領域AR側の側面21sとy方向に相対向する側面22sを有する第2の絶縁体ピラー22と、第1及び第2の絶縁体ピラー21,22の上面を覆う絶縁膜31と、第1のゲート電極16と電気的に接続し、かつ少なくとも側面21s,22sを覆う第2のゲート電極23と、底面に絶縁膜31及び第2のゲート電極23が露出したコンタクトホールの内部に設けられ、かつ第2のゲート電極23の上面と電気的に接続するゲートコンタクトプラグ42とを備え、側面21s,22s間の距離は、ゲートコンタクトプラグ42のx方向の長さより短く、ゲートコンタクトプラグ42は側面21s,22s間の領域で第2のゲート電極23と電気的に接続する。

(もっと読む)

半導体装置の製造方法、配線用銅合金、及び半導体装置

【課題】半導体装置の歩留まりと信頼性を向上させる。

【解決手段】配線凹部に埋め込まれた部分以外のバリアメタル膜3b上のCu膜5bを化学機械研磨によって除去する。そして配線凹部内のCu膜5b上に、添加元素からなる層6bを形成する。添加元素を層6bからCu膜5b中に拡散させて、Cu表面、及びCu結晶粒の粒界及び該粒界近傍の位置においてCu結晶粒内部よりも添加元素の濃度が高い界面及びその近傍を形成するとともに、Cu膜5b中の酸素を層6bにゲッタリングさせる。その後、余剰な層6bを除去し、さらに絶縁膜上のバリアメタル膜3bを除去する。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】基板上で第1方向に延在するラインパターンと、ラインパターンの端部から、第1方向と異なる方向に延在する分岐ラインパターンとをそれぞれ含む第1導電ライン;第2導電ライン;第3導電ラインとを含む半導体素子であり、中間に位置する導電ラインの分岐ラインパターンは、他の導電ラインの分岐ラインパターン間に位置し、長さもさらに短い。これにより、コンタクト・パッドが、導電ラインの分岐ラインパターンと一体に形成されうる。

(もっと読む)

半導体装置およびその製造方法

【課題】高い耐電圧特性、および耐リーク特性を有する配線構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体素子が設けられた基板と、前記基板上に形成された第1および第2の配線と、前記第1の配線の下面の前記第2の配線側に接続されたビアと、前記ビアを含むビア層絶縁膜と、を有する半導体装置を提供する。前記ビアは、前記第1の配線と前記第2の配線の間の領域である配線間領域下の上端に凹部を有する。前記ビア層絶縁膜は、前記第1および第2の配線の幅方向に前記ビアと隣接する領域を含む溝を前記配線間領域の下に有する。前記配線間領域および前記溝内にはエアギャップが含まれる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性が損なわれるのを防止しつつ、電気的特性の良好な半導体装置を提供する。

【解決手段】半導体基板10上に、化学気相堆積法により、シリコンと酸素と炭素とを含む絶縁膜42を形成する工程と、絶縁膜を形成する工程の後、350℃以下の温度で加熱しながら絶縁膜に対して紫外線キュアを行う工程と、紫外線キュアを行う工程の後、絶縁膜に対してヘリウムプラズマ処理を行う工程とを有している。

(もっと読む)

141 - 160 / 1,171

[ Back to top ]