Fターム[5F033QQ28]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287) | 絶縁膜 (1,171)

Fターム[5F033QQ28]に分類される特許

161 - 180 / 1,171

半導体装置および半導体装置の製造方法

【課題】歩留まりに優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、基板内の記憶回路領域に形成されており、多層配線層内に埋め込まれた少なくとも1以上の容量素子および周辺回路を有する記憶回路と、平面視において、基板内の憶回路領域とは異なる領域である論理回路領域に形成された論理回路と、を備え、容量素子は、下部電極、容量絶縁膜、上部電極、埋設電極および、上部接続配線で構成されており、上部接続配線と埋設電極とは、同一の材料かつ一体に構成されており、上部接続配線と下部電極との間には、論理回路を構成する前記配線が少なくとも1以上設けられており、上部接続配線の上面と、上部接続配線と同じ配線層に形成された論理回路を構成する配線の上面とが、同一面を構成する。

(もっと読む)

半導体装置の製造方法

【課題】チップ面積の削減が可能な側壁加工プロセスを用いた半導体装置の製造方法を提供すること。

【解決手段】実施形態の半導体装置の製造方法は、基板301上に被加工膜302を形成し、被加工膜の上に芯材膜304を形成し、芯材膜の一部であって被加工膜の加工時まで残存させる残存部分とそれ以外の芯材膜である除去予定部分との間が所定距離の間隙となるように芯材膜をパターニングする。パターニングの後に芯材膜の側面に側壁305を形成して除去予定部分および残存部分の側面を側壁で覆うとともに残存部分と除去予定部分との間の所定距離の間隙を側壁で閉塞する。さらに、側面が側壁で覆われた残存部分の上面を覆うようにレジスト306を形成し、レジストの形成後にウェットエッチングを行うことにより除去予定部分を除去し、ウェットエッチングの後にレジストを除去する。レジストを除去した後に側壁および残存部分をマスクとして被加工膜を加工する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に伴うLERやLWRに起因する配線の抵抗率の増大を抑制し得る手法を提供する。

【解決手段】半導体装置は、基板101と、基板上において同一の配線層内に形成された複数の配線111と、配線間に埋め込まれるよう形成された複数の絶縁膜112とを備える。そして、これら複数の配線は、両側面のLER(Line Edge Roughness)の相関係数が正である配線が、連続して2N本(Nは4以上の整数)以上並んだ配線群を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極の形成に時間を要さず、貫通電極内でのボイドの発生を抑制できる半導体装置、およびこの半導体装置の製造方法を提供すること。

【解決手段】半導体装置1は、孔111が形成された絶縁性あるいは半導体の層11と、層11の孔111内に設けられた貫通電極12と、を備える。貫通電極12は、シード層121と、めっき層122と、を備える。シード層121は、孔111の底面111Aを覆う。また、シード層121は、孔111の側面111Bのうち、孔111の開口から、孔111の開口と孔111の底面111Aとの間の所定の位置までの第1の領域を未被覆とし、この第1の領域(未被覆領域)111B1を除いた第二の領域を被覆している。めっき層122は、シード層121と、未被覆領域111B1の少なくとも一部を覆う。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明ではフォトリソグラフィー技術解像限界付近のパターン形成を安定して形成すると共に、コンタクトプラグなどの構造物における目合わせずれや接触面積の縮小による接触電気抵抗の増大や接続不良を解決する。

【解決手段】半導体基板上に形成された絶縁材料層100に、第1の方向に延在し、底部の幅W1より上部の幅W2が広い第1の溝101を形成する工程と、第1の溝101内に、溝の上端より低い位置まで埋め込み層102を形成する工程と、埋め込み層102上に露出している第1の溝101の側壁を覆うサイドウォール103を形成する工程と、サイドウォール103をマスクとして埋め込み層102をエッチングして第1の方向に分離する工程と、

を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ビット線材料埋設体の形状のばらつきに起因するビット線の配線抵抗値のばらつきを防ぐ半導体装置の製造方法を提供する。

【解決手段】製造方法は、第一溝4内に第一のビット線材料埋設体6および第二のビット線材料埋設体10からなるビット線11を形成する第一工程と、ビット線11に含まれる不純物を拡散させて第一不純物拡散領域13を形成する第二工程と、ピラー部1bを形成する第三工程と、ピラー部1bに対向する配線17を第二溝15内に形成する第四工程と、ピラー部1bの先端部に、第二不純物拡散領域19を形成する第五工程と、を具備し、第一工程が、第一溝4を完全に埋め込むように第一ビット線材料を形成した後に第一ビット線材料表面を平坦化し、第一溝4底部に残るように第一ビット線材料をエッチバックする工程を具備する。

(もっと読む)

半導体素子、及びその形成方法

【課題】 信頼性が向上する半導体素子、及びその形成方法を提供する。

【解決手段】 半導体素子の形成方法は、半導体基板100の上にゲート電極120及びゲート電極120の両側にスペーサー110を形成する段階、ゲート電極120の上にキャッピングパターン170を形成する段階、ゲート電極120の間にメタルコンタクト195を形成する段階を含み、キャッピングパターン170の幅はゲート電極120の幅より大きく形成される。これにより、形成された半導体素子は、メタルコンタクト195とゲート電極120との間での電気的な短絡を效果的に防止することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトホール形成時の重ね合わせずれに起因したリークの増大やコンタクト抵抗の上昇が抑制された半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100と、半導体基板100上にゲート絶縁膜101を介して形成されたゲート電極102と、ゲート電極102の側壁上に形成されたサイドウォールスペーサ150と、半導体基板100のうち、ゲート電極102及びサイドウォールスペーサ150を間に挟んで両側に形成されたソースドレイン領域106と、ゲート電極102、サイドウォールスペーサ150、及び半導体基板100の上面を覆う応力絶縁膜110とを備えている。サイドウォールスペーサ150は、少なくとも中央部のゲート長方向膜厚よりも上部のゲート長方向膜厚の方が大きくなっている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ビア深さのバラツキを抑制することができる半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に、SiおよびCを含むキャップ絶縁膜を形成する工程と、キャップ絶縁膜上に、キャップ絶縁膜と比較して、シリコン原子数に対する炭素原子数の組成比が高い、有機シリカ膜を形成する工程と、不活性ガス、Nを含むガス、フッ化炭素ガスおよび酸化剤ガスを含む混合ガスを用いたプラズマ処理により、有機シリカ膜に、異なる開口径を有する2以上の凹部を形成する工程と、を含む。

(もっと読む)

他の素子の処理の間のメモリセルの活性層の保護

【課題】メモリ構造に対して損傷を与えることを防止しながら選択された導電体から表面酸化物を適切に除去する。

【解決手段】導電層(102)を設け、その導電層(102)を覆うように誘電体(100)を設け、その誘電体(100)を貫通する第1および第2の開口(104,106)を設け、第1および第2の開口(104,106)内にそれぞれ第1および第2の導電体(108,110)を設けかつ第1および第2の導電体(108,110)を導電層(102)に接触させ、その第1の導電体(108)を覆うようにメモリ構造(126)を設け、そのメモリ構造(126)を覆うように保護要素(134)を設け、その第2の導電体(110)上に処理を施すことによる電子構造の製造方法。

(もっと読む)

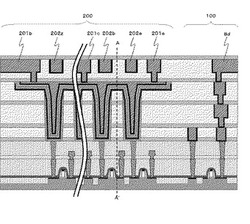

半導体記憶装置およびその製造方法

【課題】記憶素子の下にあるコンタクトプラグの上面の平坦性を改善し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、半導体基板上に設けられた複数のスイッチングトランジスタと、隣接する2つのスイッチングトランジスタ間に埋め込まれ、該隣接する2つのスイッチングトランジスタの各ゲートから絶縁されかつ該隣接する2つのスイッチングトランジスタのソースまたはドレインに電気的に接続され、上面がスイッチングトランジスタの上面よりも高い位置にあるコンタクトプラグと、コンタクトプラグの上面上に設けられ、データを記憶する記憶素子と、記憶素子上に設けられた配線とを備えている。

(もっと読む)

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】サイドウォールスペーサを利用してリソグラフィー解像限界未満のパターンと任意の寸法のパターンとが混在するパターンを形成する。

【解決手段】アモルファスカーボン膜3及びシリコン酸窒化膜4からなる被エッチング部材上に塗布膜5をスピン塗布法により成膜し、塗布膜5をパターニングすることによってサイドウォールコアを形成し、サイドウォールコアの少なくとも側面を覆うシリコン酸化膜7を成膜し、シリコン酸化膜7上に有機反射防止膜8をスピン塗布法により成膜する。次いで、有機反射防止膜8をエッチングすることによって、シリコン酸化膜7の凹部7aを覆う埋込マスクを形成し、シリコン酸化膜7をエッチングすることにより、サイドウォールコアまたは埋込マスクと重ならない被エッチング部材を露出させ、被エッチング部材をエッチングすることでフォトリソグラフィー解像限界未満のパターンを得る。

(もっと読む)

半導体装置の製造方法

【課題】SMAP法と比べて少ない積層数の膜構成で被加工部材に対し高アスペクト比の加工を行うことができる半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法によれば、被加工部材上にBを含む第1の膜、及びシリコン酸化膜からなる第2の膜を形成し、凹凸形状によりパターンが形成された原版を第2の膜に押し付けてパターンを第2の膜に転写し、パターンが転写された第2の膜をマスクとして、CH3FとO2を含み、酸素濃度を50〜90原子%とするエッチングガスを用いて第1の膜をエッチングしてパターンを第1の膜に転写し、パターンが転写された第1の膜をマスクとして被加工部材を加工してパターンを有する凹部を形成する。

(もっと読む)

半導体装置の製造方法

【課題】新規な半導体装置の製造方法を提供する。

【解決手段】本実施形態に係る半導体装置の製造方法は、下層配線としてCu配線を含む多層配線と、前記Cu配線を形成するために用いられるCuアクセサリとが形成された半導体基板を、ポリイミド膜で覆う工程と、前記多層配線の最上層配線の表面および前記Cuアクセサリの表面を露出させる工程と、前記半導体基板をCu腐食防止剤の蒸気にさらして、前記最上層配線の表面および前記Cuアクセサリの表面にCu腐食防止膜を形成する工程と、前記最上層配線の表面に形成されたCu腐食防止膜を選択的に除去する工程と、前記Cuアクセサリの表面にCu腐食防止膜が形成された状態で、前記ポリイミド膜をベーク処理する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数及び製造コストを削減しつつ、信頼性の高い半導体装置を製造することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層1上にTiを主成分とする密着層2を形成する工程と、密着層2上にWを主成分とする導電層3を形成する工程と、導電層3上にSiONを主成分とするハードマスク層4を形成する工程と、ハードマスク層4上にレジストパターン5を形成する工程と、レジストパターン5を保護膜とするエッチング処理により導電層3の一部3aを露出させる工程と、レジストパターン5及びハードマスク層4の残部4aを保護膜とするエッチング処理により密着層2の一部2aを露出させる工程と、その後、エッチング処理により下地層1の一部1aを露出させると共に、導電層3の残部3bを露出させる工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】簡易な追加工程を設けることで、基板のベベル部から膜が剥離することを抑制する。半導体装置の製造歩留まりの低下を抑制すると共に、製造コストの増加を抑制する。

【解決手段】半導体基板上の全面に、1以上の膜を有する構造を形成した後、膜構造上にパターンを有する第1のマスクを形成する。ベベル部上の第1のマスクを覆うように第2のマスクを形成する。第1のマスク及び第2のマスクを用いて、膜構造をエッチングした後、残留した第1のマスク及び第2のマスクを除去する。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタの誘電体膜を構成する強誘電体又は高誘電体の結晶性が良好であり、キャパシタのスイッチング電荷量が高く、低電圧動作が可能で信頼性が高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板110にトランジスタT1、T2を形成した後、ストッパ層120及び層間絶縁膜121を形成する。そして、層間絶縁膜121にコンタクトホールを形成し、層間絶縁膜121上に銅膜を形成してコンタクトホール内に銅を埋め込む。その後、低圧CMP研磨又はECMP研磨により層間絶縁膜121上の銅膜を除去して表面を平坦化し、プラグ124a,124bを形成する。次いで、バリアメタル125、下部電極126a、強誘電体膜127及び上部電極128aを形成する。このようにして、強誘電体キャパシタ130を有する半導体装置(FeRAM)が形成される。

(もっと読む)

基板の製造方法、半導体装置の製造方法、電気光学装置

【課題】任意の方向に傾斜した開口部を形成可能な基板の製造方法、半導体装置の製造方法、およびこれを適用した半導体装置を備えた電気光学装置を提供すること。

【解決手段】本適用例の素子基板101の製造方法は、素子基板101上に設けられた半導体装置としてのTFT110を覆うと共に第1開口部としての孔104aが設けられた第2絶縁膜としての層間絶縁膜104をマスクとして、素子基板101の面法線101aと交差する一の方向からドライエッチングを第1絶縁膜としてのゲート絶縁膜103に施して、孔104aに連通すると共にTFT110のドレイン電極110dに開口する第2開口部としての孔103aを形成する。

(もっと読む)

半導体ウエハとその製造方法、及び半導体チップ

【課題】半導体チップ領域内へのクラック伝播を抑制でき新規な構造を持つ金属リングを有する半導体ウエハを提供する。

【解決手段】半導体ウエハは、半導体素子が形成された第1半導体チップ領域と、半導体素子が形成された第2半導体チップ領域と、第1半導体チップ領域と第2半導体チップ領域との間に挟まれたスクライブ領域とを有し、第1半導体チップ領域は、第1半導体チップ領域に形成された半導体素子を囲む金属リングを含み、金属リングは、下側金属層と下側金属層上に重なる上側金属層とを含む複数の金属層で形成され、上側金属層の第1半導体チップ領域外側の側面が、下側金属層の外側の側面と揃っているか、または、下側金属層の外側の側面に対して第1半導体チップ領域内側に位置しているように、下側金属層上に上側金属層が重なっている。

(もっと読む)

161 - 180 / 1,171

[ Back to top ]