Fターム[5F033QQ28]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287) | 絶縁膜 (1,171)

Fターム[5F033QQ28]に分類される特許

201 - 220 / 1,171

成膜方法、半導体装置の製造方法及び半導体装置

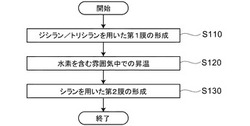

【課題】表面の平坦性の優れたシリコン膜を形成する成膜方法、半導体装置の製造方法及び半導体装置を提供する。

【解決手段】基体上にジシラン及びトリシランの少なくともいずれかを用いて第1温度で第1膜を形成する第1膜形成工程と、前記基体及び前記第1膜を、水素を含む雰囲気中において、前記第1温度から、前記第1温度よりも高い第2温度に向けて昇温する昇温工程と、前記昇温の後に、前記第1膜の上に、シランを用いて前記第2温度で第2膜を形成する第2膜形成工程と、を備えたことを特徴とする成膜方法が提供される。

(もっと読む)

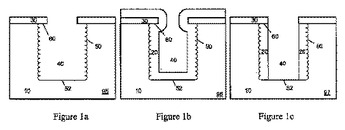

ビア及びエッチングされた構造におけるコンフォーマル絶縁層の形成方法及びパターン形成方法

マスク層の下にアンダーカット形状を形成するエッチングプロセスによって基板にビアが形成される。ビアはコンフォーマルな絶縁層で覆われ、この構造にエッチングプロセスを実施して水平面から絶縁層を取り除くと共にビアの垂直な側壁の絶縁層を残す。ビアの上部領域はエッチバックプロセスの際、アンダーカットハードマスクによって保護される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】側壁転写によるマスクパターンの倒れ、マスクパターンの接触を抑制する。

【解決手段】シリコン基板1上に、第1のTEOS酸化膜2、シリコン窒化膜3、第1のアモルファスシリコン膜4、第2のTEOS酸化膜5を積層形成する。レジストによるパターニングでTEOS酸化膜5を第1幅D1の中間パターン5aに加工し、スリミング処理をして第2幅D2の芯材パターン5bを形成する。第2のアモルファスシリコン膜6を形成してスペーサ処理をすることで側壁膜6aを形成し、芯材パターン5bを除去して孤立したマスクパターン6bを得る。下地に同じアモルファスシリコン膜4を用いるので、マスクパターン6bの倒れや接触の発生を抑制できる。

(もっと読む)

半導体集積装置の評価システム及び評価用半導体チップ

【目的】プラズマプロセスによる半導体集積装置の各製造段階において、所望のエッチング工程で生じたチャージアップの度合いのみを測定することが可能な半導体集積装置の評価システム及び評価用半導体チップを提供することを目的とするものである。

【構成】評価用半導体チップにプラズマエッチング処理を施している間にこの評価用半導体チップ内に生じたチャージアップに伴って流れる電流を、評価用半導体チップから外部に導出されている第1リード線及び第2リード線を介して計測する。評価用半導体チップは、シリコン基板上にゲート酸化膜、ゲート電極、プラズマによる電子電流の流入を部分的に遮断するパターンを有するレジストが積層された構造を有する。この際、レジスト上面側からシリコン基板の表面までを貫通する第1のコンタクトホールを介して上記第1リード線がシリコン基板の表面と電気的に接続されていると共に、上記レジストを貫通する第2のコンタクトホールを介して第2リード線がゲート電極の表面と電気的に接続されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】素子の信頼性を劣化させることなく、より比誘電率の低い絶縁膜を形成する。

【解決手段】この半導体装置の製造方法は、下地膜101に、環状シロキサンをプラズマ重合させて第一の絶縁膜102を形成する工程と、第一の絶縁膜102を形成する工程の後、連続的に、第一の絶縁膜102上に、環状シロキサンをプラズマ重合させて第二の絶縁膜103を形成する工程と、を含む。第一の絶縁膜102の成膜速度は、第二の絶縁膜103の成膜速度よりも遅い。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写技術を使用したパターニングの加工性の向上を図る。

【解決手段】ゲート電極MGを形成するための被加工膜8上にCVD法でカーボン膜9aを形成し、続いてSOG膜を形成する。カーボン膜9aをリソグラフィ技術によるレジストパターンでハーフエッチするとともに、幅寸法をWaから半分のWbにスリミングして芯材パターン部9bを形成する。全面にアモルファスシリコン膜14を形成し、エッチバック処理でスペーサパターン14aを形成し、これをマスクとして芯材パターン部9bと共にカーボン膜9aをエッチングしてマスクパターン9を形成する。レジストを芯材パターンとして用いないので高温で加工ができ、加工性が向上する。

(もっと読む)

ドライエッチング方法

【課題】コストの上昇を招くことなく、より安定した状態でInPの層がドライエッチング法によりエッチングできるようにする。

【解決手段】塩素ガスを用いたドライエッチング法によりマスクパターン106をマスクとして基板101を選択的にエッチングすることで、基板101にビアホール(開口パターン)107を形成する。例えば、温度条件を200℃程度とし、塩素ガスを用いた反応性イオンエッチング法によりエッチングすればよい。

(もっと読む)

半導体装置、及びその製造方法

【課題】配線の導通信頼性を損なうことなく、エアギャップを形成でき、配線間容量Cが低減した配線膜構造を有する半導体装置を提供することである。

【解決手段】 半導体装置の製造方法において、第1絶縁膜を形成する第1絶縁膜形成工程と、前記第1絶縁膜に配線膜を形成する配線膜形成工程と、前記配線膜が形成されてない箇所の前記第1絶縁膜にドライエッチングで溝を形成するドライエッチング工程と、前記ドライエッチング工程の後、前記溝が埋め尽くされることが無いよう、前記配線膜および前記溝上に第2絶縁膜を形成する第2絶縁膜形成工程とを具備する。

(もっと読む)

半導体装置の製造方法

【目的】ウェット処理を行った場合でも絶縁膜上に庇形状が形成されない半導体装置の製造方法を提供する。

【構成】本発明の一態様の半導体装置の製造方法は、基板上に絶縁膜を形成する工程(S102)と、絶縁膜上に保護膜を形成する工程(S104)と、保護膜に第1の開口部を形成する工程(S114)と、第1の開口部内に保護膜よりもウェットエッチングレートが大きい犠牲膜を形成する工程(S116)と、第1の開口部内の犠牲膜に第1の開口部よりも幅の狭い第2の開口部を形成する工程(S122の一部)と、第2の開口部を転写することで絶縁膜に第3の開口部を形成する工程(S122の一部)と、第3の開口部が形成された後に、ウェット処理を行なう工程(S126)と、ウェット処理後に、第3の開口部内にバリアメタル膜を形成する工程(S128)と、第3の開口部内に導電性材料を埋め込む工程(S132)と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 組み立て工程やCMP工程時における剥離を抑制した、低誘電率層間絶縁膜の製造方法とそれを用いた半導体装置を提供する。

【解決手段】低誘電率層間絶縁膜の成膜の際、高周波と低周波の2周波を切り替え、膜厚方向に膜特性の変調をかけることで、低誘電率を保持したまま密着強度を向上させる。プラズマ発生のための高周波と低周波が同一電極から印加される。そして絶縁膜の成膜開始時あるいは成膜終了時の少なくとも一方において、低周波の入力が成膜開始時及び成膜終了時を除いた他のタイミングより高い。例えば絶縁膜は、厚さ方向における少なくともどちらか一方の端部が、高周波と低周波の2周波により密着層となり、密着層以外の部分は低周波の入力を低下あるいは0にすることで低誘電率絶縁膜となる。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

基板処理方法及び記憶媒体

【課題】低誘電率膜であるSiCOH膜とCu配線との夫々の露出面に炭素の脱落したダメージ層及び酸化物が夫々形成された基板に対してダメージ層を回復させ且つ酸化物を還元すること。

【解決手段】SiCOHを含む層間絶縁膜4とCuを含む配線2との夫々の露出面に炭素の脱落したダメージ層15及び酸フッ化層16が夫々形成されたウエハWに対して、H2ガスの供給とシリコン及び炭素を含むTMSDMAガスの供給とを同一の処理容器51においてこの順番で連続して行うことによって、酸フッ化層16の還元処理及びダメージ層15の回復処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】配線幅の拡大の阻止を図ることができる半導体装置の製造方法を提供する。

【解決手段】基板上に層間絶縁膜を形成する工程と、前記層間絶縁膜に配線溝を形成する工程と、前記配線溝に配線を形成する工程とを具備し、前記配線溝を形成する際に、前記配線溝内に酸素ラジカルを吸収する酸素ラジカル吸収物質を形成する(ステップS104)。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、炭化シリコン薄膜の機械強度を高め、膜の消失や剥離を防止する。

【解決手段】 ポーラスな誘電率低誘電率絶縁膜上に−CH2−結合が環状になってSiと結合し且つ二重結合を含む官能基を有する原料を用いて炭化シリコン薄膜を形成する工程と、前記炭化シリコン薄膜を所定パターンにエッチングしてハードマスクを形成する工程と、前記ハードマスクをエッチングマスクとして前記低誘電率絶縁膜をエッチングして配線形成用溝或いはビアホールの少なくとも一方を形成する工程とを設ける。

(もっと読む)

EM保護が施された半導体ダイを形成する方法

【課題】電磁(EM)妨害あるいはEMIに対してある程度の保護を具備した半導体装置において、低コストで、半導体ウエハからEM保護の施されたダイを形成する方法を提供する。

【解決手段】半導体ダイ12,13,14は、傾斜したサイドウォール35,36,37を有するように形成される。この傾斜サイドウォール上、および、半導体ダイの底部表面上に導体40が形成される。導電材料である導体40は、ダイ12−14に対しEMIから保護する。

(もっと読む)

半導体装置の製造方法、半導体装置、及び半導体製造装置

【課題】有機シリカ膜を成膜したのちのプラズマ反応室の内壁のクリーニング時間を短縮する。

【解決手段】まずプラズマ反応室内壁をプリコート膜で被覆する(プリコート工程)。次いで基板上に、シリコン炭素組成比(C/Si)が1以上である有機シリカ膜を成長させる(基板処理工程)。次いで、基板を取り出した後、プラズマ反応室内壁に付着した有機シリカ膜とプリコート膜とをプラズマを用いて除去する(クリーニング工程)。プリコート膜としては、基板上に成膜された有機シリカ膜よりも少なくとも炭素含有率が低い有機シリカ膜である高酸素含有プリコート膜を用いる。

(もっと読む)

EM保護が施された半導体ダイを形成する方法

【課題】電磁(EM)妨害あるいはEMIに対してある程度の保護を具備し半導体装置において、半導体ウエハからダイを低コストで形成する方法を提供する。

【解決手段】半導体ダイ12,13,14は、傾斜したサイドウォール35,36,37を有するように輸送テープあるいはキャリヤ・テープ38上に形成される。この傾斜サイドウォール上、および、底部表面上に導体40が形成される。導電材料である導体40は、ダイ12−14に対しEMIからの保護を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜を除去するエッチング中に、異常エッチングを防止する。エッチング工程において加わる水圧や風圧によりガードリングの形状が変形して剥離し、欠陥が発生することを防止する。

【解決手段】半導体装置は、メモリセル領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた周辺回路領域と、ガードリング及び周辺回路領域上に設けられた支持体膜と、周辺回路領域内に設けられたコンタクトプラグとを有する。ガードリングとコンタクトプラグは、同一の導電材料から構成される。

(もっと読む)

ハードマスク材料

【課題】集積回路製造工程のバックエンドプロセス、およびフロントエンドプロセスにおいて利用することができる、高硬度、且つ低応力のハードマスク膜を提供する。

【解決手段】ハードマスク膜は、応力が約−600MPaから600MPaの範囲内であり、硬度は少なくとも約12Gpaである。ハードマスク膜は、PECVD処理チャンバにおいて、高密度化プラズマ後処理を複数回行うことによって、ドープ済または未ドープのシリコンカーバイドの副層を複数成膜することによって得られる。ハードマスク膜は、SixByCz、SixByNz、SixByCzNw、BxCy、およびBxNyから成る群から選択される高硬度のホウ素含有膜を含む。ハードマスク膜は、ゲルマニウム含有率が少なくとも約60原子パーセントと、ゲルマニウム含有率が高いGeNxハードマスク材料を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極にシリサイドを形成しつつ、拡散領域に接続するコンタクトとゲート電極の間隔を確保する。

【解決手段】被覆絶縁膜120は、ゲート電極140のチャネル幅方向における少なくとも一部上に形成されている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、ゲート電極140上、及び被覆絶縁膜120上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。シリサイド層142は、ゲート電極140上に形成されている。サイドウォール160は、被覆絶縁膜120が形成されている領域においてはゲート電極140より高く形成されている。そしてコンタクト210は、ゲート電極140のうち被覆絶縁膜120が形成されている領域に面している。

(もっと読む)

201 - 220 / 1,171

[ Back to top ]