Fターム[5F033QQ28]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287) | 絶縁膜 (1,171)

Fターム[5F033QQ28]に分類される特許

121 - 140 / 1,171

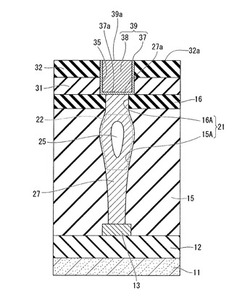

半導体装置の製造方法

【課題】低コストで、かつ簡便な方法で、コンタクトプラグ上に形成される銅配線の上面にヒロックが生じて短絡が発生することを抑制可能な半導体装置の製造方法を提供する。

【解決手段】配線13を覆う層間絶縁膜15の上面に、層間絶縁膜よりもエッチング速度の遅いエッチングストッパ膜16を形成する。エッチングストッパ膜のうち、配線と対向する部分を貫通する第1の開口部16Aを形成する。エッチングストッパ膜よりも層間絶縁膜がエッチングされやすい条件を用いて、配線の上面が露出するまで第1の開口部の下方に位置する層間絶縁膜をエッチングして、第1の開口部と共にコンタクトホールを構成する第2の開口部15Aを形成する。第1の開口部を埋め込むように、コンタクトホール内に導電膜を成膜することでコンタクトプラグ27を形成する。電解メッキ法により、コンタクトプラグの上面と接触する銅配線39を形成する。

(もっと読む)

エッチング方法

【課題】 有機Si系低誘電率膜をマスクとして被処理体のSiC部分をエッチングガスのプラズマによりエッチングする場合に、エッチングレートおよび有機Si系低誘電率膜に対するエッチング選択比を高くしてエッチングすることができるエッチング方法を提供すること。

【解決手段】 SiC膜61と、その上に形成された有機Si系低誘電率膜62とを有する構造において、有機Si系低誘電率膜62をマスクとしてSiC膜61をエッチングガスのプラズマによりエッチングするに際し、エッチングガスとして、CH2F2を含有するガスまたはCH3Fを含有するガスを用いる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、多層配線構造を有する半導体装置及びその製造方法に関し、信頼性や製造歩留りが高く、設計的な制約の小さい半導体装置及びその製造方法を提供することを目的とする。

【解決手段】基板10上に形成された配線20、40、60、80と、配線20、40、60、80の周囲に形成された低誘電率膜12、32、52、72、92と、低誘電率膜12、32、52、72、92の形成材料より弾性係数の大きい誘電体材料で形成され、基板面に垂直に見て配線20、40、60、80に重なって配置された補強用絶縁膜42a、62a、82a、102aと、配線20、40、60、80に交差して配置された補強用絶縁膜22b、42b、62b、82b、102bとを有するように構成する。

(もっと読む)

パターン化金属膜及びその形成方法

【課題】ドライエッチングが困難な遷移金属の膜を、サイドエッチングが極力生じないようにパターニングする。

【解決手段】絶縁膜の上にバリア層・密着層を形成し(S1)、その上に遷移金属からなるシード層を形成する(S2)。シード層の上にSiO2膜及びフォトレジスト膜を順次形成し(S3、S4)、フォトレジスト膜、SiO2膜をパターニングして開口を形成し(S5,S6)、開口内にCu膜及びマスクAl膜を積層する(S7、S8)。次に、SiO2膜をエッチング(S9)、露出したシード層をその膜厚方向に異方的に改質し(S10)、改質されたシード層、露出したバリア・密着層、及びマスクAl膜を順次エッチングにより除去することにより(S10〜S13)、パターン化金属膜を得る。

(もっと読む)

半導体装置の製造方法

【課題】パターン疎密差の影響を受けないハードマスク形成法を提供する。

【解決手段】基板101上に、第1から第3の膜111,112,113およびレジスト層114を形成した後、疎部R1と密部R2が存在するパターンを前記レジスト層に形成して前記第3の膜をエッチングする。次に、前記第3の膜及び前記レジスト層をマスクとして、密部R2内では前記第2の膜が残存するが、疎部R1内では前記第1の膜が露出するまで、前記第2の膜を除去する。その後CXFYHZガスを使用して、第5の膜115を、疎部R1内に露出した前記第1の膜上に第1の膜厚T1で形成し、密部R2内に残存する前記第2の膜上には膜厚T1よりも薄い第2の膜厚T2で形成する。膜厚T1の前記第5の膜で疎部R1内に露出した前記第1の膜を保護しながら密部R2内に残存する前記第2の膜を除去し、最後に、前記第3から第5の膜を除去して前記第2の膜をハードマスクとする。

(もっと読む)

半導体装置の製造方法

【課題】 接続孔のホールサイズについて制御性良い半導体装置の製造方法を提供する。

【解決手段】 実施形態の半導体装置の製造方法では、半導体基板上に上層絶縁膜が形成され、前記上層絶縁膜上にSiを含む非晶質膜が形成される。前記非晶質膜上に第1のレジスト膜が形成され、前記第1のレジスト膜に第1のレジストパターンが形成される。前記第1のレジスト膜をマスクとして、前記非晶質膜が加工され、前記上層絶縁膜が露出される。前記第1のレジストパターンが除去され、前記非晶質膜および露出した前記上層絶縁膜上に遷移金属膜が形成される。前記非晶質膜および前記遷移金属膜の熱反応により、前記非晶質膜よりも体積が大きいシリサイド膜が形成される。前記遷移金属膜が除去され、前記シリサイド膜をマスクとして、前記上層絶縁膜を加工し、前記上層絶縁膜に第1の溝が形成される。

(もっと読む)

多相超低誘電膜の形成方法

【課題】誘電率が2.7以下であり、弾性計数および硬度の改善等、機械的特性を向上させた超低誘電率(k)膜、および膜の製造方法を提供する。

【解決手段】多相超低k誘電膜44は、Si、C、O、およびHの原子を含み、誘電率が約2.4以下であり、ナノサイズの孔または空隙を有し、弾性係数が約5以上であり、硬度が約0.7以上である。好適な多相超低k誘電膜44は、Si、C、O、およびHの原子を含み、誘電率が約2.2以下であり、ナノサイズの孔または空隙を有し、弾性係数が約3以上であり、硬度が約0.3以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

ビアホールの製造方法およびビアホールを有する半導体素子の製造方法

【課題】内部への埋め込み材料を増量させて放熱性向上効果を得ることが可能なビアホール構造を、ビアホール形成のための半導体基板へのエッチングの回数を少なくしつつ製造することのできるビアホールの製造方法およびビアホールを有する半導体素子の製造方法を提供する。

【解決手段】メタルマスク8は、メタルマスク10の開口23により露出させられた部分8aを有する。メタルマスク10は、メタルマスク8よりも厚く形成する。メタルマスク10の厚さは、開口23内のエッチングが半導体デバイス形成層4にほぼ到達すると同時に、開口22のエッチングがソース電極1に到達する厚さに設定する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の多層配線において配線間隔を低減させても所定の低比誘電率を維持できるとともに、電気的特性の劣化などを抑制できる多孔性の層間絶縁膜の形成方法を提供する。

【解決手段】 半導体基板1上に形成される配線構造を構成し、空孔を有する多孔性絶縁膜13を得るための母体となる母体絶縁膜を気相成長法を用いて堆積する。この際、多孔性絶縁膜13の比誘電率、配線20間の間隔や絶縁耐圧のような、配線構造を決める因子に要求される設計値に応じて、多孔性絶縁膜13の分子骨格形成材料の流量に対する多孔性絶縁膜13の空孔形成材料の流量の比の、少なくとも範囲をまず決定する。この後、決定した流量比の範囲で母体絶縁膜を堆積し、この母体絶縁膜に熱や紫外線などのエネルギーを与えて空孔を有する多孔性絶縁膜13にする。

(もっと読む)

埋め込み配線を備える基板、その製造方法、これを利用する半導体装置およびその製造方法

【課題】 低抵抗の埋め込み配線を備える基板の製造方法を提供する。

【解決手段】 始めに半導体用基板100の第1面S1上に導電層120を形成する。次に、導電層120をパターニングして第1方向に延長する線形の導電層パターン122を形成する。導電層120をパターニングするとき露出する半導体用基板100をエッチングして導電層パターン120の下部に第1方向に延長する線形の半導体パターン104を形成する。次に導電層パターン120および半導体パターン104上に絶縁層150を形成する。半導体用基板100の第1面S1側の絶縁層150が支持基板160と当接するように支持基板160上に配置する。次に半導体用基板100のイオン注入層102側の絶縁層150が露出するように半導体用基板100を除去する。これにより、導電層パターン120は、半導体パターン104の埋め込み配線として利用することができる。

(もっと読む)

半導体装置の製造方法

【課題】的確かつ効果的にパターンを形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地領域上に、第1のピッチで配置された複数のダミーラインパターン21cを形成する工程と、ダミーラインパターン21cの両長側面に形成された所定マスク部分を有し、ダミーラインパターンを囲む閉ループ形状のマスクパターン25cを形成する工程と、ダミーラインパターン21cを除去する工程と、マスクパターン25cの両端部分を除去して所定マスク部分を残す工程と、所定マスク部分をマスクとして用いて下地領域をエッチングする工程とを備える。

(もっと読む)

重合体、膜形成用組成物、絶縁膜、半導体装置および重合体の製造方法

【課題】エッチング工程によってもダメージを受けにくい絶縁膜を形成し得る重合体を含む膜形成用組成物、前記絶縁膜、該絶縁膜を備える半導体装置、さらには前記重合体の製造方法を提供すること。

【解決手段】本発明の膜形成用組成物は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する化合物Cを含む重合性化合物を重合することにより得られる、分散比が1.0以上2.5以下の重合体を含むものである。

(もっと読む)

半導体装置の製造方法

【課題】容量コンタクトパッドと容量コンタクトプラグが一体となった構造を形成する。これにより、従来は2回、必要だったフォトリソグラフィ工程を1回に削減して、製造コストを低減する。

【解決手段】半導体装置の製造方法では、層間絶縁膜上に、開口を有するマスクパターンを形成する。このマスクパターンを用いて、層間絶縁膜をエッチングすることにより、開口の下の層間絶縁膜内に容量コンタクトホールを形成する。湿式エッチングにより、マスクパターン内の開口を大きくした後、開口内に導電材料を埋め込むことにより、それぞれ容量コンタクトプラグ及び容量コンタクトパッドを形成する。この後、容量コンタクトパッド上にキャパシタを形成する。

(もっと読む)

半導体装置とその製造方法

【課題】ダマシン配線構造を有する半導体装置において、フルオロカーボン膜へのエッチングダメージによるCu配線構造でのリーク電流の増加や誘電率の低下を抑制し、信頼性の担保された半導体装置の製造方法を提供する。

【解決手段】エッチング処理の施されたフルオロカーボン膜の表面に対し、窒化プラズマ処理またはCFプラズマ処理を行う、半導体装置の製造方法が提供される。これによれば、配線溝形成時のフルオロカーボン膜へのエッチングダメージが修復され、Cu配線構造におけるリーク電流の増加や誘電率の低下を抑制することができる。

(もっと読む)

パターン形成方法及びデバイス製造方法

【課題】露光装置の解像限界よりも微細な非周期的な部分を含むパターンを、露光装置を用いて形成する。

【解決手段】パターン形成方法は、ウエハW上に第1L&Sパターン71を形成し、第1L&Sパターン71を覆うように第1保護層48、周期方向が直交する第2L&Sパターン78、及びフォトレジスト層60を形成し、第2L&Sパターン78の一部と重なるように、フォトレジスト層60に第1開口部60A,60Bを有する第3パターンを形成し、第1開口部60A,60Bを介して第1保護層48に第2開口部48A,48Bを形成し、第2開口部48A,48Bを介して第1L&Sパターン71の一部を除去する。

(もっと読む)

半導体装置の製造方法

【課題】厚みのばらつきが低減したCu配線層を形成する半導体装置の製造方法を提供する。

【解決手段】実施形態の半導体装置の製造方法は、基板1上に所望の配線厚みに対応する厚みのエッチングストッパー膜2を形成し、酸化膜3を形成し、マスク材4を形成し、マスク材に配線の形状の溝パターンを形成し、溝パターンが形成されたマスク材をマスクとして酸化膜に溝パターンが形成されるようにエッチングする。溝パターンが形成された酸化膜をマスクとして、溝パターンが形成されるようにエッチングストッパー膜を貫通するまでエッチングし、エッチングストッパー膜および酸化膜に形成された溝パターンを埋め込み、酸化膜の上面を覆いつくすようにCu膜5を形成し、エッチングストッパー膜をストッパーとして、その上面が露出するまでCu膜及び酸化膜にCMPを行う。

(もっと読む)

半導体装置およびその製造方法

【課題】サイドウォール間に層間絶縁膜を埋め込むときに埋め込み不良の発生を防止できる半導体装置の製造方法を提供する。

【解決手段】シリコン基板2の表面上に、ゲート酸化膜6、ポリシリコン層(第1ゲート層)9、タングステンシリサイド層(第2ゲート層)10および絶縁層8が形成される。絶縁層8が所定のゲートパターンにエッチングされる。タングステンシリサイド層10が前記所定のゲートパターンにエッチングされる。タングステンシリサイド層10の側壁が後退される。この後、ポリシリコン層9が前記所定のゲートパターンにエッチングされる。ゲート酸化膜6が前記所定のゲートパターンにエッチングされる。

(もっと読む)

121 - 140 / 1,171

[ Back to top ]