Fターム[5F033QQ28]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287) | 絶縁膜 (1,171)

Fターム[5F033QQ28]に分類される特許

101 - 120 / 1,171

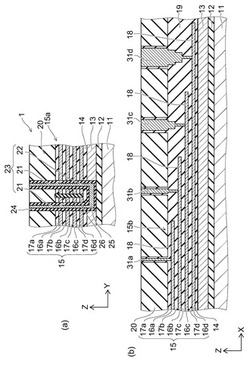

半導体記憶装置及びその製造方法

【課題】コストが低い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、絶縁膜及び電極膜が交互に積層された積層体を形成する工程と、前記積層体上に、サイズが相互に異なる複数のホールが形成されたハードマスクを形成する工程と、マスク材料を堆積させることにより、最も小さい前記ホールを閉塞させると共に、その他の前記ホールを小さくする工程と、前記マスク材料及び前記ハードマスクをマスクとしてエッチングを施すことにより、前記その他のホールの直下域において、各所定枚数の前記絶縁膜及び前記電極膜を除去して、コンタクトホールを形成する工程と、前記コンタクトホールを介してエッチングを施すことにより、前記電極膜の一部分を除去して隙間を形成する工程と、前記隙間内に絶縁材料を埋め込む工程と、前記コンタクトホール内に導電材料を埋め込む工程と、を備える。

(もっと読む)

パターンの形成方法

【課題】LELEプロセスよりも少ない工程数で、フォトリソグラフィ技術を2度使用することなく、微細なホール又はトレンチパターンを形成する方法を提供すること。

【解決手段】被処理体の上にレジスト膜を成膜し、成膜した前記レジスト膜をパターニングする、レジスト膜形成工程と、前記被処理体及び前記レジスト膜を被覆するようにスペーサ膜を成膜して、前記スペーサ膜で囲まれた凹部を形成する、スペーサ膜成膜工程と、前記凹部の底面にある前記被処理体及び前記レジスト膜の上面を露出させると共に、前記レジスト膜の側面側に前記スペーサ膜が残るようにエッチングして、前記凹部から第1の開口部を形成する、第1開口部形成工程と、前記レジスト膜を除去することにより第2の開口部を形成する、第2開口部形成工程と、を含むパターンの形成方法。

(もっと読む)

銅の光子誘起除去

【課題】基板から銅含有層の少なくとも一部を除去する方法を提供する。

【解決手段】第1反応チャンバ中で、銅含有表面層4の少なくとも一部を、ハロゲン化銅表面層5に変える工程と、第2反応チャンバ中で、光子含有雰囲気6に晒して、ハロゲン化銅表面層5の少なくとも一部を除去して、揮発性のハロゲン化銅生成物8の形成を始める工程とを含む。光子含有雰囲気6に晒す間に、この方法は、更に、第2反応チャンバから揮発性のハロゲン化銅生成物8を除去し、第2反応チャンバ中で揮発性のハロゲン化銅生成物8の飽和を避ける工程を含む。本発明の具体例にかかる方法は、銅含有層のパターニングに用いられる。例えば、本発明の具体例にかかる方法は、半導体デバイス中に銅含有相互接続構造を形成するのに使用される。

(もっと読む)

半導体装置

【課題】貫通電極の形成に時間を要さず、貫通電極内でのボイドの発生を抑制できる半導体装置、およびこの半導体装置の製造方法を提供すること。

【解決手段】半導体装置1は、孔111が形成された絶縁性あるいは半導体の層11と、層11の孔111内に設けられた貫通電極12と、を備える。貫通電極12は、シード層121と、めっき層122と、を備える。シード層121は、孔111の底面111Aを覆う。また、シード層121は、孔111の側面111Bのうち、孔111の開口から、孔111の開口と孔111の底面111Aとの間の所定の位置までの第1の領域を未被覆とし、この第1の領域(未被覆領域)111B1を除いた第二の領域を被覆している。めっき層122は、シード層121と、未被覆領域111B1の少なくとも一部を覆う。

(もっと読む)

半導体素子及びその製造方法

【課題】絶縁膜を貫通するコンタクトプラグの抵抗を改善させられる半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグと、前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の容量の増大が実現される半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、半導体基板1内の記憶回路領域に形成されており、多層配線層内に設けられた凹部40内に埋め込まれた少なくとも1以上の容量素子19および周辺回路を有する記憶回路200と、平面視において、半導体基板1内の記憶回路領域とは異なる領域である論理回路領域に形成された論理回路100と、当該凹部40内において、下部電極14、容量絶縁膜15、及び上部電極16から構成される前記容量素子19上に積層している上部接続配線18と、容量素子19が埋め込まれている配線層のうち最上層に設けられた論理回路100を構成する配線8bの上面に接するように設けられたキャップ層6cと、を備え、上部接続配線18の上面30とキャップ膜6cの上面34とが、同一面を構成している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を製造する。また、スループットを向上させ、製造コストを低減する。

【解決手段】開口部OA1および絶縁膜(21、23)上に銅のCuシード層27を形成する工程と、Cuシード層上に、フォトレジスト膜を形成する工程と、Cuシード層上に、メッキ成長により銅膜31aを形成する工程と、銅膜上に、Ni膜31bを形成する工程と、により、再配線31を形成する。この後、再配線31上の開口部(OA2、パッド領域)にAu膜33bを形成した後、フォトレジスト膜を除去し、Ni膜31bに不動態化処理を施す。この後、再配線31の形成領域以外のCuシード層27をエッチングする。かかる工程によれば、Ni膜31bの表面に不動態化膜35が形成され、上記エッチングによるNi膜31bの膜減りを低減できる。また、膜減りを考慮したNi膜の厚膜化による基板の歪みによる不具合を低減できる。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコンプラグと上層の導体プラグとの界面に十分な膜厚の金属シリサイド層を形成してコンタクト抵抗の低減を図る。

【解決手段】多結晶シリコンプラグを形成した後、多結晶シリコンプラグの表面からゲルマニウムイオン注入を実施してゲルマニウム含有多結晶シリコン16Gとし、その後、シリサイド化可能な金属膜を成膜して金属シリサイド層19を形成し、金属シリサイド19上に導体膜(バリア膜20、W膜21)を形成する。

(もっと読む)

半導体装置の製造方法及びハードマスクの形成方法

【課題】アモルファスカーボン膜のパターン寸法ばらつきが低減した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に下地膜を形成する工程と、下地膜上にアモルファスカーボン膜を成膜する工程と、アモルファスカーボン膜のパターンを形成する工程と、アモルファスカーボン膜をマスクにして下地膜をエッチングする工程を有する。アモルファスカーボン膜は、アモルファスカーボン膜の表面から下地膜に接する面に向かってその厚み方向を進むにつれて、アモルファスカーボン膜の膜密度を小さくする。

(もっと読む)

半導体装置およびその製造方法

【課題】 表面側から特性試験が行える縦型の半導体装置を提供する。

【解決手段】 半導体装置10では、半導体基板11は第1の面と、第1の面に対向する第2の面を有している。半導体素子12は半導体基板11のダイシングライン14、15で囲まれた矩形状格子に形成されるとともに、第1の面に形成された第1電極26と、第2の面に形成された第2電極28とを有している。電流は第1電極26と第2電極28の間に流れる。貫通電極16は半導体基板11のダイシングライン14、15で囲まれていない領域に形成されるとともに、一端が第1の面上に延在し、他端が第2電極28と電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

半導体装置の製造方法及び製造装置

【課題】半導体装置のエッチングを精度良く行い、再生率を低減させる

【解決手段】基板にトランジスタを形成し、トランジスタを覆うように第1層間絶縁膜22を形成する。さらに、第1層間絶縁膜22の上方に形成したレジスト膜27を用いて第1層間絶縁膜22をエッチングし、トランジスタのソース/ドレイン領域に到達するコンタクトホール31を形成する。この際、レジスト膜27の開口部27Aの半径rと、開口部27Aが設計位置からずれている位置ずれ量ΔXとを測定し、コンタクトホール31に必要な半径Rxと、コンタクトホール31を形成可能な限界距離Sとから、r+ΔX−S<ES<r−Rxを満たす半径差ESを決定し、半径差ESからエッチング条件を決定する。

(もっと読む)

半導体装置の製造方法

【課題】携帯電話などのフロントエンドモジュールに使用されているハイパワーアンプは、シリコン系CMOS集積回路をベースとするデバイスであるが、その出力段に多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成したLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。このポリシリコンプラグは、熱処理に起因する固相エピタキシャル成長により収縮し、シリコン基板に歪が発生する。

【解決手段】本願発明は、LDMOSFET等の半導体装置の製造方法において、基板の表面からエピタキシャル層を貫通するホールを形成し、ポリシリコンプラグを埋め込むに際して、ホールの内面に薄膜酸化シリコン膜が存在する状態で、ポリシリコン部材の堆積を行うものである。

(もっと読む)

埋め込みビットラインを備えた半導体装置の製造方法

【課題】埋め込みビットラインの抵抗を減少させることができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板201に活性領域203を分離するトレンチ202をエッチングにより形成するステップと、活性領域203の何れか1つの側壁の一部を露出させた開口部207を有する絶縁膜205を形成するステップと、絶縁膜205上にトレンチ202を部分的に埋め込み、開口部207を埋め込むようにシリコン膜パターン208Aを形成するステップと、シリコン膜パターン208A上に金属膜209を形成するステップと、金属膜209及びシリコン膜パターン208Aを反応させて、埋め込みビットラインとなる金属シリサイド膜211を形成するステップとを含む。

(もっと読む)

側壁イメージ転写からパターンを作る改善された方法

【課題】実施の容易な、側壁イメージ転写により部分的に定義されるパターンを生成する方法を提供する。

【解決手段】基板1には、第1の材料2の層と、第1のエッチングマスク4と、カバリング層3と、第2のエッチングマスクとが設けられている。カバリング層3は、覆われた主領域と、覆われていない副領域とを有する。カバリング層3の副領域は、第2のエッチングマスクを介して部分的にエッチングされ、突出パターンが形成される。第3のエッチングマスクを定義する突出パターンの周囲に、横スペーサが形成される。第2のエッチングマスクは除去される。カバリング層3は、第3のエッチングマスクを用いてエッチングされ、カバリング層3における突出パターンが形成され、第1のエッチングマスク4および第1の材料2が露出される。第1の材料2の層は、エッチングされ、第1の材料2から作られるパターンが形成される。

(もっと読む)

半導体装置の作製方法

【課題】コンタクトホールを微細化する。この時、微細化されたコンタクトホールであっ

ても、半導体装置における電極のコンタクトを確実なものとする。

【解決手段】珪化膜と樹脂材料膜とからなる多層の層間絶縁膜を形成する。その後、コン

タクトホールを形成する。このとき、珪化膜に設けられるコンタクトホールの大きさを樹

脂材料膜に設けられるコンタクトホールの大きさよりも小さくする。このような構成は、

パターンが複雑化してもコンタクトのとりやすいものとすることができる。

(もっと読む)

三次元積層構造を持つ半導体装置の製造方法

【課題】 三次元積層構造を持つ半導体装置において、積層された半導体回路層間の積層方向の電気的接続を、埋込配線を使用して容易に実現する半導体装置の製造方法を提供する。

【解決手段】 第1半導体回路層1aの半導体基板11の表面に、絶縁膜14で内壁面が覆われたトレンチ13を形成し、トレンチ13の内部に導電性材料を充填して導電性プラグ15を形成する。次に、トレンチ13とは重ならないように所望の半導体素子を基板11の表面または内部に形成し、その上に層間絶縁膜19を介して多層配線構造30を形成してから、多層配線構造30の表面にプラグ15に電気的に接続されたバンプ電極37を形成する。そして、電極37を用いて基板11を支持基板40に固定してから基板11をその裏面側から選択的に除去し、絶縁膜14を基板11の裏面側に露出させる。基板11の裏面側に露出せしめられた絶縁膜14を選択的に除去してプラグ15を露出させ、その端に電極42を形成する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル部に印加される応力を増加させて、電流増加効果を高めることを可能とする。

【解決手段】半導体基板上にダミーゲートを形成した後、該ダミーゲートの側壁に側壁絶縁膜を形成し、該ダミーゲートの両側の前記半導体基板にソース・ドレイン領域を形成する工程と、前記ダミーゲートおよび前記ソース・ドレイン領域の上に応力印加膜を形成する工程と、前記ダミーゲートの上の領域に形成された前記応力印加膜と前記ダミーゲートを除去して溝を形成する工程と、前記溝内の前記半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、を備えた半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】低コストで、かつ簡便な方法で、コンタクトプラグ上に形成される銅配線の上面にヒロックが生じて短絡が発生することを抑制可能な半導体装置の製造方法を提供する。

【解決手段】配線13を覆う層間絶縁膜15の上面に、層間絶縁膜よりもエッチング速度の遅いエッチングストッパ膜16を形成する。エッチングストッパ膜のうち、配線と対向する部分を貫通する第1の開口部16Aを形成する。エッチングストッパ膜よりも層間絶縁膜がエッチングされやすい条件を用いて、配線の上面が露出するまで第1の開口部の下方に位置する層間絶縁膜をエッチングして、第1の開口部と共にコンタクトホールを構成する第2の開口部15Aを形成する。第1の開口部を埋め込むように、コンタクトホール内に導電膜を成膜することでコンタクトプラグ27を形成する。電解メッキ法により、コンタクトプラグの上面と接触する銅配線39を形成する。

(もっと読む)

101 - 120 / 1,171

[ Back to top ]