Fターム[5F033QQ28]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287) | 絶縁膜 (1,171)

Fターム[5F033QQ28]に分類される特許

61 - 80 / 1,171

半導体装置およびその製造方法

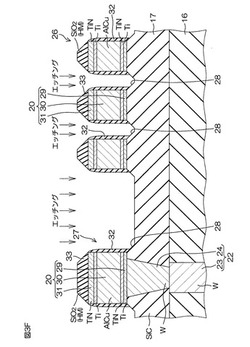

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】SiCからなる第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2からなるハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、第1AlCu配線20を形成する。第1AlCu配線20の形成後、第2層間膜17をエッチングすることにより低段部28を形成する。このとき、第2層間膜17(SiC)からCを解離させ、その解離したCを含む反応生成物を側壁保護膜32に定着させることによって、側壁保護膜32を厚くする。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2膜33およびSiC膜35からなる積層膜36を形成し、この積層膜36をパターニングすることによりハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、当該エッチングによりSiC膜35から解離したCを含む反応生成物を含む側壁保護膜32を、エッチング途中のAlCu膜30の側面に形成しながらAlCu配線層34をパターニングすることによって、第1AlCu配線20を形成する。

(もっと読む)

電気光学装置の製造方法

【課題】層間絶縁膜のコンタクトホールの内部にコンタクト用導電膜および埋め込み膜を設けた場合でも、コンタクトホールの外部で画素電極とコンタクト用導電膜とを確実に導通させることができる電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置100を製造するにあたって、層間絶縁膜45上にコンタクトホール45aの底部45eおよび内壁45fに重なるコンタクト用導電膜90をITO膜により形成した後、コンタクトホール45aの内部を埋める埋め込み膜48をシリコン酸化膜により形成し、その後、埋め込み膜48に対して反応性イオンエッチングを行い、コンタクト用導電膜90を露出させる。また、コンタクトホール45aの内部には埋め込み膜48を残す。その際、埋め込み膜48とコンタクト用導電膜90とのエッチング選択比を利用して埋め込み膜48を選択的に除去してコンタクト用導電膜90を露出させる。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の低抵抗化を図る。

【解決手段】本実施形態の半導体装置は、半導体基板10を覆う第1の層間絶縁膜上に設けられる配線60と、配線60の上面上に設けられるキャップ層68と、配線60と第2の層間絶縁膜との間に設けられるバリア膜62と、を含む。配線60は高融点導電層を含み、配線60の配線幅W1は、キャップ層68の幅W2よりも小さい。バリア膜62は、高融点導電層60が含む元素の化合物からなり、配線60を覆う層間絶縁膜69,70に起因する不純物が配線60内に拡散するのを抑制する。

(もっと読む)

半導体装置の製造方法

【課題】電解めっき法によるCu膜の確実に析出させる。

【解決手段】抑制剤と促進剤を添加しためっき液とシリコン基板の相対速度が100m/分以上になる速度でシリコン基板を回転させながら、シリコン基板をめっき槽に浸漬させる。抑制剤の分子がシード層の表面に吸着し、シード溶解が抑制される。導電膜を成長させるときは、シリコン基板とめっき液の相対速度が30m/分以下になる速度でシリコン基板を回転させながら、シリコン基板とアノード電極の間に通電する。ボトムアップ成長が促進され、配線溝内での空孔の形成が防止される。

(もっと読む)

半導体装置の製造方法

【課題】CMP法により、金属膜を研磨して、層間絶縁膜に設けられた開口部内に導体パターンを形成する際、リセス、ディッシング、及びエロージョンを抑制可能な半導体装置の製造方法を提供する。

【解決手段】CMP法により、層間絶縁膜14の上面よりも上方に形成された金属膜19及びバリア膜18を除去することで、開口部内に、バリア膜18及び金属膜19よりなる導体パターンを形成する研磨工程と、を有し、該研磨工程では、層間絶縁膜14の上面が露出する前に、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件を用いて研磨を行なうことで、導体パターンを形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

半導体装置の製造方法

【課題】反射防止膜を確実に除去して半導体装置の欠陥発生を低減する。

【解決手段】第1の層間絶縁膜の上に、絶縁膜と、反射防止膜と、レジスト膜とを順番に形成する。レジスト膜を用いて反射防止膜と絶縁膜をエッチングし、絶縁膜からハードマスクを作成する。この後、ラジカル照射によってレジスト膜と反射防止膜を除去する。ラジカル照射は、基板温度を100℃、150℃、250℃と順番に上昇させながら行う。基板温度が低い初期段階では、反射防止膜の膜材料の飛散防止と、反射防止膜の表面に残留する他の物質の除去が行われる。この後、基板温度を高くすることで、反射防止膜が確実に除去される。

(もっと読む)

多層接続構造及びその製造方法

【課題】3次元積層ICデバイスにおいて、相互接続領域のコンタクトレベルのスタックへの電気接続形成工程を簡略化する製造方法を提供する。

【解決手段】各コンタクトレベルは導電層と絶縁層とを有する。コンタクト開口を作り出すために、第1のコンタクトレベルを露出させるように上部層の一部が除去される。N個のマスクを用いて、最大2N個のコンタクトレベルまでコンタクト開口がエッチングされる。各マスクは、コンタクト開口のうちの実効的に半数をエッチングするために使用される。Nが3であるとき、第1のマスクにより1つのコンタクトレベルがエッチングされ、第2のマスクにより2つのコンタクトレベルがエッチングされ、第3のマスクにより4つのコンタクトレベルがエッチングされる。コンタクト開口の側壁に誘電体層が形成され得る。コンタクト開口内に導電体が形成され、前記誘電体層が該導電体を前記側壁から電気的に絶縁する。

(もっと読む)

半導体装置の製造方法

【課題】基板のエッジ部分での膜剥がれを防止し、半導体装置を効率良く製造する。

【解決手段】基板1の上方に低誘電体膜31を形成する際に、基板1のエッジ部分1Aをエッジカット工程にて洗い流すことで段差部31Aが形成される。低誘電体膜31に配線溝41を形成した後、導電膜43を埋め込む。基板1のエッジ部分1Aの導電膜43を洗い流すと、導電膜43が埋め込まれていない配線溝41Aが形成される。配線溝41Aを保護フィルム51で覆ってから、CMP法にて余分な導電膜43を除去する。この後、保護フィルム51を基板1から取り外す。

(もっと読む)

半導体装置およびその製造方法

【課題】ダイシング工程で発生する膜剥離やクラックがチップ内部に伝播するのを防ぐ。

【解決手段】半導体装置100は、基板102と、ビア層130および配線層132が形成される素子形成領域であるチップ内部202と、平面視においてチップ内部202を囲むようにチップ内部202の外周に形成されたシールリング部204と、を含む。シールリング部204において、シールリングは、平面視においてチップ内部202を囲むように形成された貫通孔122aを有する第1のメタル層122と、第1のメタル層122上に第1のメタル層122に接して形成された第2のメタル層124と、を含み、第1のメタル層122の貫通孔122aの下部分には絶縁性材料(層間絶縁膜106)が形成され、貫通孔122aの上部分には第2のメタル層124を構成するメタル材料がくい込んで形成される。

(もっと読む)

パターン形成方法

【課題】微細なパターンと比較的サイズが大きめのパターンとを有するパターン形成方法で、サイズが大きめのパターンを従来に比して精度良く形成することができるパターン形成方法を提供する。

【解決手段】実施形態によれば、加工対象上の芯材膜31に開口を形成した後、マスク膜32をコンフォーマルに形成する。マスク膜32をエッチバックして芯材膜31の側面に第1の幅のマスク膜32を残す。開口の形成領域以外の領域にレジストパターン35aを形成し、これをマスクに芯材膜31をエッチングする。さらに、芯材膜31をスリミングして第1の幅より小さい第2の幅のラインアンドスペース状のパターンを形成する。側壁膜をコンフォーマルに形成した後、エッチバックし、さらに芯材膜31を除去して、加工対象上に側壁膜からなる側壁パターンを形成する。そして側壁パターンで加工対象をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極の形成過程で、余分な酸化膜を確実に除去する。

【解決手段】貫通電極を形成するビアホール25の内面に酸化膜26を形成した後、Cu膜28を埋め込む。第1層間絶縁膜22の上に形成された余分なCu膜28をCMP法による研磨で除去するときに、酸化膜26も研磨されて膜厚が薄くなる。膜厚が薄くなった酸化膜26Bをハードマスクとして第1層間絶縁膜14に配線溝を形成する。このとき、酸化膜26Bの膜厚が薄くなる。配線溝に導電材を埋め込んだ後、余分な導電材を研磨によって除去する。このとき、残りの酸化膜26Bが全て研磨により除去される。

(もっと読む)

半導体装置の製造方法

【課題】 低k膜と金属マスクとの間の界面に歪みを引き起こすことなく、高い精度の望ましいパターンを得ること。

【解決手段】 半導体装置を製造する方法では、金属マスクと絶縁マスクをと備える多層ハードマスクを用いて形成される配線層を含む半導体装置が形成される。第1パターンにアラインされた第2開口パターンを形成するために、第1ステップで多層ハードマスクが使用された後、金属マスクが除去され、絶縁マスクが、第2のステップで絶縁層中に第1のパターン構造を形成するために使用される。

(もっと読む)

複数の開口部を備える基板上への層の蒸着方法

【課題】多孔性低誘電率絶縁膜のトレンチおよびビア内にカバレージ良くライニング層を形成する半導体装置の製造方法を提供する。

【解決手段】第1パルス期間に供給される第1反応物と、第2パルス期間に供給される第2反応物とを利用する原子層堆積(ALD)プロセスにより成膜する。まずシーリング層を低コンフォマリティーを有する条件で成膜し、ポアをブロックする。この後、接着層を高いコンフォマリティーを有する条件で成膜する。

(もっと読む)

半導体装置、半導体装置の製造方法、固体撮像装置及び電子機器

【課題】 ビア形成時のエッチングによる基板や配線への影響を抑制しつつ積層された半導体ウェハの回路どうしを接続する。

【解決手段】 半導体装置の製造方法は、第1基板と第1基板の一面と接するように形成された第1絶縁層を有する第1の半導体ウェハと、第2基板と第2基板の一面と接するように形成された第2絶縁層を有する第2の半導体ウェハを接合する工程と、第1基板の他面に第3絶縁層を形成する工程と、第3絶縁層、第1基板、及び第1絶縁層を貫通し第2絶縁層に形成された第2の配線上に第2絶縁層が残るようにエッチングを行い第1接続孔を形成する工程と、第1接続孔に絶縁膜を形成する工程と、第2の配線上の第2絶縁層及び絶縁膜のエッチングを行い第2接続孔を形成し第2の配線を露出させる工程と、第1及び第2接続孔の内部に形成され第2の配線と接続する第1のビアを形成する工程とを備え、第1基板の他面に形成された第1接続孔の径は第3絶縁層に形成された前記第1接続孔の径より大きい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ワイヤがCuワイヤであっても、ボンディング時の衝撃による金属のスプラッシュを抑制する。

【解決手段】半導体装置は、電極パッド103を有する半導体チップと、電極パッド103にボンディングされたワイヤ(例えばCuワイヤ105)と、を有している。電極パッド103において、ワイヤがボンディングされている領域の少なくとも表層はルテニウム又は酸化ルテニウムにより構成され、その表層の膜厚は20nm以上である。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】配線幅若しくは配線間隔の縮小に伴い、加工限界の制約を受けるために微細な配線形成が困難になりつつある。

【解決手段】絶縁層(第1の絶縁層12及び第2の絶縁層13)に溝15を形成し、導体膜(バリア膜16及び金属膜17)を溝15を埋設しない膜厚で形成し、続いて導体膜をエッチバックすることで溝15の側壁にサイドウォール状の配線18を形成することで、配線幅は導体膜の膜厚で制御できるために加工限界の制約を受けず、配線抵抗は配線高さを高くすることにより所定の配線抵抗を維持することができる。

(もっと読む)

集積回路装置及びその製造方法

【課題】ビアの形成が容易で抵抗が低い集積回路装置及びその製造方法を提供する。

【解決手段】相互に平行に配列された複数本の配線14a、14bと、各配線に接続されたビア16とを備える。配線におけるビアが接続された部分には、配列の方向に延出した凸部31が形成されており、配線における凸部が形成された部分から離隔した部分には、配列の方向に後退した凹部32が形成されている。隣り合う2本の配線において、一方の配線に形成された凸部と他方の配線に形成された凹部とは相互に対向している。各配線において、凹部が形成された部分はその両側の部分から切込33で分断されており、凸部が形成された部分からも分断されている。

(もっと読む)

半導体素子の形成方法

【課題】相互接続領域の具現が困難なパッドレイアウトを具現化し、オーバレイマージンを増大できる半導体素子の形成方法を提供する。

【解決手段】半導体基板に被食刻層、第1のハードマスク物質層、第1の分割パターン物質層及び第2のハードマスク物質層を形成して選択食刻し第2のハードマスクパターンを形成し、これをマスクとし第1の分割パターン物質層を食刻し第1の分割パターンを形成する。第1のハードマスク物質層の上部にスペーサ物質層及び第2の分割パターン物質層を形成し、第1の分割パターンが現われるまでスペーサ物質層及び第2の分割パターン物質層を部分食刻しスペーサ物質層を露出させ、複数の第1の分割パターン間に第2の分割パターンを形成し、第1、第2の分割パターンをマスクとしスペーサ物質層及び第1のハードマスク物質層を食刻し第1のハードマスクパターンを形成し、これをマスクとし被食刻層を食刻し微細パターンを形成する。

(もっと読む)

61 - 80 / 1,171

[ Back to top ]